| University of Cincinnati                                                                                                     |                                                                                             |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| Date: 4/14/2015                                                                                                              |                                                                                             |  |  |  |  |

|                                                                                                                              | asi , hereby submit this original work as part of aster of Science in Computer Engineering. |  |  |  |  |

| It is entitled:<br>Study of Ultra Low Power Design and Power Reduction Techniques for VLSI<br>Circuits at Ultra Low Voltages |                                                                                             |  |  |  |  |

| Student's name: Phani Kames                                                                                                  | wara Abhishikth Varanasi                                                                    |  |  |  |  |

|                                                                                                                              | This work and its defense approved by:                                                      |  |  |  |  |

|                                                                                                                              | Committee chair: Wen-Ben Jone, Ph.D.                                                        |  |  |  |  |

| 17                                                                                                                           | Committee member: Ranganadha Vemuri, Ph.D.                                                  |  |  |  |  |

| UNIVERSITY OF Cincinnati                                                                                                     | Committee member: Philip Wilsey, Ph.D.                                                      |  |  |  |  |

|                                                                                                                              |                                                                                             |  |  |  |  |

|                                                                                                                              |                                                                                             |  |  |  |  |

|                                                                                                                              | 16163                                                                                       |  |  |  |  |

|                                                                                                                              |                                                                                             |  |  |  |  |

|                                                                                                                              |                                                                                             |  |  |  |  |

|                                                                                                                              |                                                                                             |  |  |  |  |

# Study of Ultra Low Power Design and Power Reduction Techniques for VLSI Circuits at Ultra Low Voltages

A thesis submitted to the

Division of Research and Advanced Studies of the University of Cincinnati

> in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE

in the School of Electronic and Computing Systems of the College of Engineering and Applied Sciences

April, 2015

by

### Phani Kameswara Abhishikth Varanasi

B.E (EEE), M. V. S. R. Engineering College, 2011

Thesis Advisor and Committee Chair: Dr. Wen Ben Jone

### Abstract

The advancements and scaling in technology are continuously increasing in accordance with Moore's Law. This results in an increase in the performance of chips, but comes with a price due to the increased power consumption, and hence resources are spent on cooling, packaging and other methods to reduce the after effects. This additional cost has to be eliminated, and the most obvious solution is to reduce the power consumption of a design which would also protect the chips from permanent failure due to additional heat in the chips.

Various power reduction methods including supply voltage scaling, dynamic voltage and frequency scaling, multi voltage design, clock gating for dynamic power reduction, and multi-Vth technique, power gating for leakage power reduction have been proposed. The main aim of our research was to reduce the supply voltage which has a quadruple effect on reducing the power consumption, and hence operate the designs in or as close to the subthreshold region of operation as possible. This kind of ultra low power designs are especially useful in biomedical applications. Carry skip adder and magnitude comparator designs are considered for our research due to the extensive use of such designs in almost all arithmetic applications. Simulations are performed at 45nm CMOS technology and at very low voltages, (e.g., 0.4V) to check the functionality first, followed by the application of some of the most widely used power reduction techniques in the industry, including clock gating and power gating, to test their effectiveness at such low voltages. Error detection sequential circuits were also employed to check if they can further reduce the power consumption and improve the performance of the designs with ultra low supply voltages. The results obtained give interesting insights into the effectiveness of various power reduction techniques at ultra low voltages.

### Acknowledgements

I would like to thank my academic advisor, Dr. Wen Ben Jone, for his extremely helpful and enthusiastic nature which paved way for the formation of our thesis. It was due to his constant encouragement and relentless attitude, coped with his words of wisdom, which helped me learn many new things. He was always supporting and never hesitated to clear my doubts or to discuss about the work, irrespective of the time, for which I am indebted to him. I would also like to thank Dr. Ranga Vemuri and Dr. Philip Wilsey for their valuable time to serve as my Masters' thesis committee members. I would also like to thank them for the courses they taught with such enthusiasm which helped me during various stages of my Masters program. I express my thanks to Rob Montjoy who helped me out whenever I had issues while working with the software.

I would like to greatly appreciate and thank my parents, who were always there for me when I needed, which motivated me to overcome tough situations. I cannot thank them enough for the sacrifices they have done for me. I would also like to immensely thank my brother, Suresh Kumar, for his constant support and advices right from my childhood till now, which helped me in all aspects of life. Special thanks to my cousin, Vishwanath Kotta for his constant support while in the US for which I am grateful to him.

I express my thanks to my roommates Nikhil, Naren, Ujwal, and friends, for all the good times we had, and for being there through thick and thin for making my Master's experience such an enjoyable one. Lastly, I would like to thank God, the almighty, for his love and for what I am right now.

# Contents

| 1 | Inti | roduction                                                             | 1  |

|---|------|-----------------------------------------------------------------------|----|

|   | 1.1  | Power Consumption Considerations                                      | 1  |

|   | 1.2  | Review of Clock Gating and Power Gating in Ultra Low Voltage Region . | 3  |

|   | 1.3  | Subthreshold Region of Operation                                      | 5  |

|   | 1.4  | Thesis Organization                                                   | 6  |

| 2 | Bac  | ekground                                                              | 8  |

|   | 2.1  | Ultra Low Voltage Design                                              | 8  |

|   | 2.2  | Adder Configurations                                                  | 9  |

|   | 2.3  | Magnitude Comparator Design                                           | 11 |

|   | 2.4  | Power Gating                                                          | 13 |

|   | 2.5  | Clock Gating                                                          | 15 |

|   | 2.6  | EDS                                                                   | 17 |

| 3 | Des  | ign and Simulation of Carry Skip Adder and Magnitude Compara-         |    |

|   | tor  | Circuits                                                              | 22 |

|   | 3.1  | Design Aspects of Circuits                                            | 22 |

|   | 3.2  | Method of Measurement of Worst Case Delay and Power                   | 23 |

|   | 3.3  | Simulation and Measurement Results                                    | 24 |

|   |      | 3.3.1 Power Tables                                                    | 24 |

|   |      | 3.3.2 Explanation of Worst Case Delays                                | 25 |

|   |      | 3.3.3 Worst Case Delay Tables                                         | 30 |

|   |      | 3.3.4 Selection of Operating Voltage and Model File Pair              | 31 |

|   | 3.4  | Observations                                                          | 32 |

|   | 3.5  | Delay Dependency on Number of Blocks per Stage                        | 34 |

| 5                  | Cor | nclusio                        | ns and Future Work                                                 | 72          |  |

|--------------------|-----|--------------------------------|--------------------------------------------------------------------|-------------|--|

|                    | 4.6 | Obser                          | vations                                                            | 68          |  |

|                    |     | 4.5.3                          | Procedure Followed During Simulations                              | 66          |  |

|                    |     | 4.5.2                          | Input Application Details for Clock Gating                         | 63          |  |

|                    |     | 4.5.1                          | Application and Simulation Details of Clock Gating for Our Designs | 59          |  |

|                    | 4.5 | Clock                          | Gating                                                             | 59          |  |

|                    |     | 4.4.1                          | Simulations for CSA                                                | 52          |  |

|                    | 4.4 | .4 Observations                |                                                                    | 52          |  |

|                    |     | 4.3.3                          | Procedure Followed During Simulations                              | 51          |  |

|                    |     | 4.3.2                          | Input Application Details for Power Gating                         | 47          |  |

|                    |     | 4.3.1                          | Application and Simulation Details of Power Gating for Our Designs | <b>5</b> 47 |  |

|                    | 4.3 | 3 Power Gating                 |                                                                    |             |  |

|                    | 4.2 | 4.2 Power Reduction Techniques |                                                                    |             |  |

|                    | 4.1 | Impor                          | tance of Power Reduction                                           | 45          |  |

| Comparator designs |     |                                |                                                                    |             |  |

| 4                  | Pow | ver Re                         | eduction Techniques for Carry Skip Adder and Magnitude             | <b>;</b>    |  |

|                    |     | 3.6.4                          | Conclusion About EDS Design in Ultra Low Power Region              | 43          |  |

|                    |     | 3.6.3                          | Problems Encountered with EDS Design at Ultra Low Voltage          |             |  |

|                    |     | 3.6.2                          | Simulations for Different Supply Voltages                          |             |  |

|                    |     | 3.6.1                          | Design and Implementation Details                                  |             |  |

|                    | 3.0 |                                | Resilient Circuit Design for Carry Skip Adder                      |             |  |

|                    | 3.6 |                                |                                                                    |             |  |

|                    |     | 3.5.3                          | Observations                                                       |             |  |

|                    |     | 3.5.2                          | Simulations and Results                                            |             |  |

|                    |     | 3.5.1                          | Motivation and Explanation                                         | 34          |  |

# List of Figures

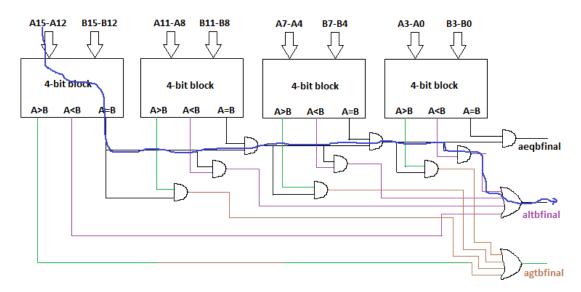

| 2.1  | Gate diagram of a 4-bit comparator block                                    | 12               |

|------|-----------------------------------------------------------------------------|------------------|

| 2.2  | Block diagram of 16-bit comparator                                          | 13               |

| 2.3  | Power gating for a design                                                   | 14               |

| 2.4  | Different power gating configurations for a circuit                         | 15               |

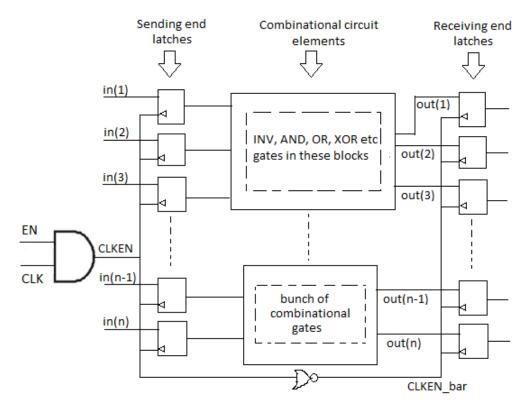

| 2.5  | Clock Gating representation                                                 | 16               |

| 2.6  | Conventional structure of a design                                          | 18               |

| 2.7  | Timing diagram for a conventional design                                    | 18               |

| 2.8  | Gate level EDS circuit design                                               | 19               |

| 2.9  | Structure of EDS design                                                     | 19               |

| 2.10 | Timing diagram showing error detection with an EDS circuit                  | 20               |

| 2.11 | Timing diagram showing no error with an EDS circuit                         | 20               |

| 3.1  | XOR configuration used                                                      | 23               |

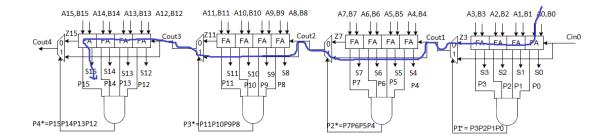

| 3.2  | The structure of a 4-bit CSA representing a stage                           | 26               |

| 3.3  | The 16-bit CSA formed through stages connected using MUXes                  | 20<br>27         |

| 3.4  | Generation of group propogate signal through NAND-NOR gates                 | 27               |

| 3.5  | Condition under which worst case delay occurs for a <i>carry skip adder</i> |                  |

| 3.6  | Different input patterns showing carry generation(g), propogation(p) and    | 20               |

| 0.0  | kill(k) by bit pairs                                                        | 29               |

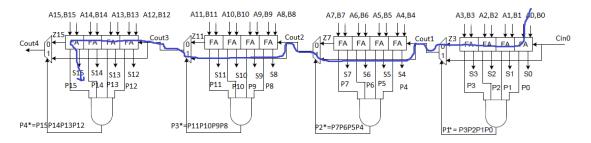

| 3.7  | Worst case delay represented for <i>carry skip adder</i>                    | <b>-</b> 0<br>30 |

| 3.8  | Worst case delay represented for the magnitude comprator                    | 32               |

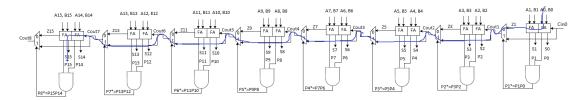

| 3.9  | Worst case delay represented for the CSA with 4 blocks per stage            | 35               |

|      | Worst case delay path for CSA with 2 blocks per stage                       | 35               |

|      |                                                                             |                  |

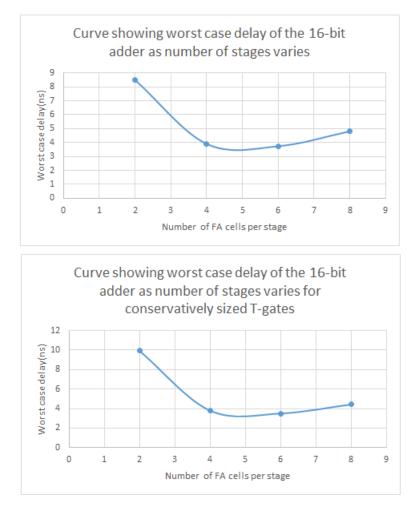

|      | Worst case delay variation with number of blocks                            | 37               |

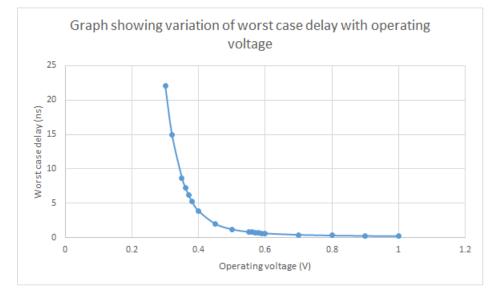

| 3.12 | Worst case delay variation with operating voltage for CSA                   | 40               |

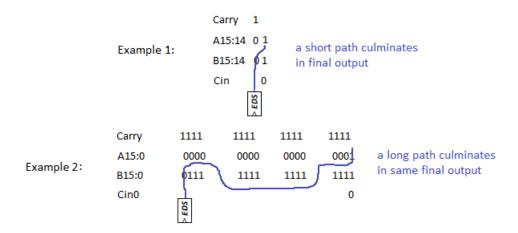

| 3.13 | Example input patterns showing short and long paths culminating in same              |    |

|------|--------------------------------------------------------------------------------------|----|

|      | output having EDS depending on applied inputs                                        | 43 |

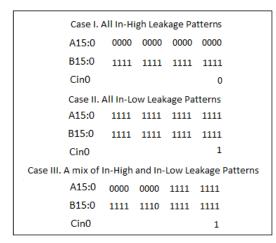

| 4.1  | Input patterns applied to the CSA circuit for leakage power measurement              |    |

|      | and power gating                                                                     | 48 |

| 4.2  | Input patterns applied to the comparator circuit for leakage power mea-              |    |

|      | surement and power gating                                                            | 50 |

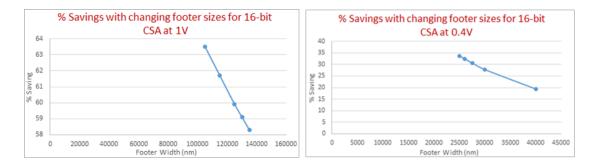

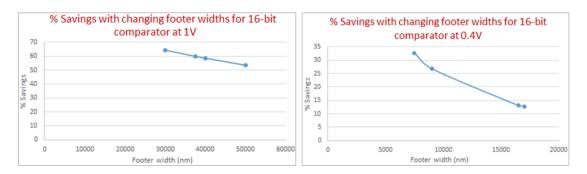

| 4.3  | $\%$ Savings with changing footer sizes for 16-bit CSA $\ldots \ldots \ldots$ .      | 55 |

| 4.4  | $\%$ Savings with changing footer sizes for 16-bit comparator $\ldots \ldots \ldots$ | 58 |

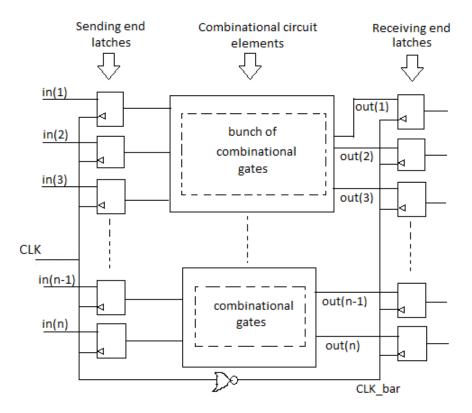

| 4.5  | Combinational circuit transformed into a sequential circuit with help of             |    |

|      | latches                                                                              | 60 |

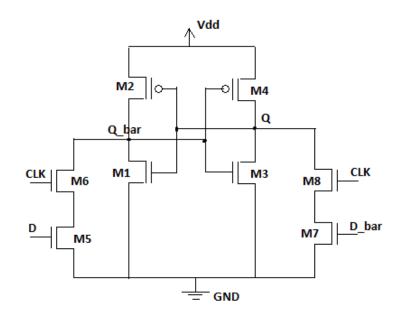

| 4.6  | Latch used for clock gating                                                          | 60 |

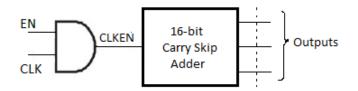

| 4.7  | AND-gate based Clock Gating technique                                                | 62 |

| 4.8  | Clock gating technique for magnitude comparator                                      | 63 |

| 4.9  | Clock gating technique for Carry skip adder                                          | 63 |

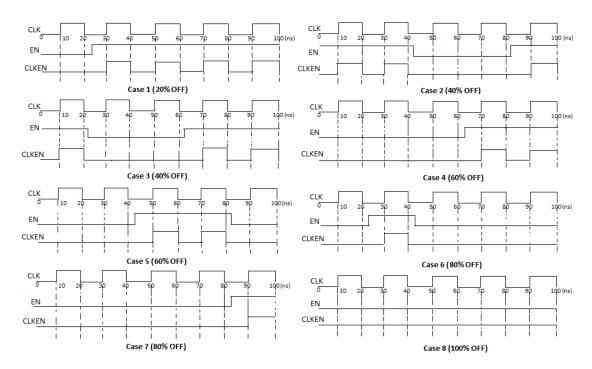

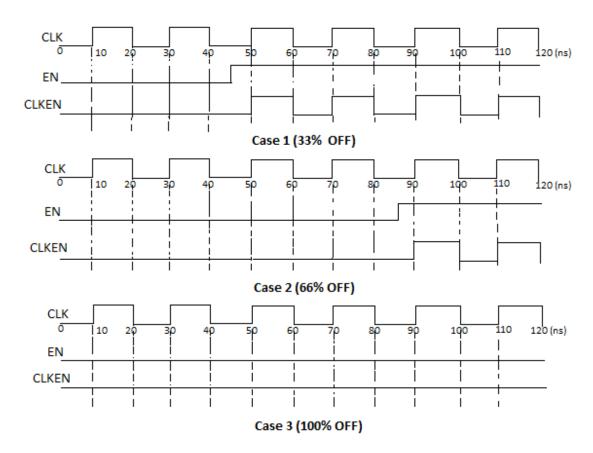

| 4.10 | Input patterns applied to the comparator for switching power measure-                |    |

|      | ment and clock gating                                                                | 64 |

| 4.11 | Input patterns applied to the CSA for switching power measurement and                |    |

|      | clock gating                                                                         | 65 |

| 4.12 | Different cases considered for clock gating for CSA                                  | 65 |

| 4.13 | Different cases considered for clock gating for comparator                           | 66 |

# List of Tables

| 3.1  | Voltages of interest for different model files                                               | 25 |

|------|----------------------------------------------------------------------------------------------|----|

| 3.2  | Power consumption for CSA at voltages of interest                                            | 25 |

| 3.3  | Power consumption for comparator at voltages of interest                                     | 26 |

| 3.4  | Worst case delays for CSA at voltages of interest                                            | 31 |

| 3.5  | Worst case delays for comparator at voltages of interest                                     | 32 |

| 3.6  | Worst case delays for CSA for different number of blocks and stages with                     |    |

|      | T-gate sizes same as those for other transistors                                             | 36 |

| 3.7  | Worst case delays for CSA for different number of blocks and stages with                     |    |

|      | T-gates conservatively sized                                                                 | 36 |

| 3.8  | Worst case delays for CSA at different voltages for EDS                                      | 40 |

| 4.1  | Leakage power measurements for a single FA cell at 0.4V and 1V                               | 48 |

|      |                                                                                              | 40 |

| 4.2  | Leakage power measurements for different cases for the 16-bit CSA for                        |    |

|      | 0.4V and 1V                                                                                  | 49 |

| 4.3  | Leakage power measurements for different cases for a 1-bit comparator                        |    |

|      | cell for 0.4V and 1V $\hdots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 49 |

| 4.4  | Leakage power measurements for different cases for the 16-bit comparator                     |    |

|      | for $0.4V$                                                                                   | 50 |

| 4.5  | Power gating results for 1 bit FA cell at 0.4V                                               | 53 |

| 4.6  | Power gating results for 1 bit FA cell at 1V                                                 | 54 |

| 4.7  | Power gating results for 16 bit CSA at 0.4V                                                  | 54 |

| 4.8  | Power gating results for 16 bit CSA at 1V                                                    | 55 |

| 4.9  | Power gating results for 1 bit comparator at 0.4V                                            | 56 |

| 4.10 | Power gating results for 1 bit comparator at 1V                                              | 57 |

| 4.11 | Power gating results for 16 bit comparator at 0.4V                                           | 57 |

|      |                                                                                              |    |

| 4.12 | Power gating results for 16 bit comparator at 1V         | 58 |

|------|----------------------------------------------------------|----|

| 4.13 | Power savings for comparator with clock gating at $0.4V$ | 67 |

| 4.14 | Power savings for CSA with clock gating at 0.4V          | 67 |

| 4.15 | Power savings for comparator with clock gating at $1V$   | 68 |

| 4.16 | Power savings for CSA with clock gating at 1V            | 68 |

### Chapter 1

# Introduction

Digital integrated circuits, each containing millions or billions of transistors fabricated on it, can function as quite a wide range of components which include memory, microprocessor or even complex design. The main feature of these ICs is to include more functionality on a relatively smaller area with a minimum weight by miniaturizing the electronic equipment [1]. The basic building blocks of integrated circuits are logic gates, which in turn contain transistors, and operate on binary data. The main advantage of integrated circuits is the cost associated with them being very low, which is bound to decrease further as more technological advances result in the generation of larger circuit functions on a single chip [1]. The ubiquitous Moore's Law pertaining to any VLSI circuit predicts that the number of transistors on an IC doubles approximately two years, and that has definitely been making a huge difference in the building of various VLSI designs. VLSI circuits are present in almost every application and hence with an increase in transistor density per a single chip, we have been empowered to accomplish more with the same available area.

### 1.1 Power Consumption Considerations

The number of transistors present on an integrated circuit is one of the most talked about factors by all VLSI engineers and the reasons are many, including but not limited to more area and power consumption, changing the density of an integrated chip and so on. The advantage of having more transistors on a single chip is to accomplish more functionality per the same available area. But, this has an offset associated with it too, in that, if the number of transistors increases, there is an increase in power density as more power is dissipated by the same functioning design. In order to deal with this increased power dissipation, cooling and packaging costs increase, which offsets the increased functionality. It can even lead to permanent failure in the chip, if the amount of heat produced becomes very high. As a result of this, there needs to be a balance between transistor density and power consumption.

Reducing the power consumption of a chip is an increasing area of importance for most of the circuits. One category of applications that focuses on reduced power consumption is one involving mobile/ portable communications and sensor systems [2]. The devices and equipment used especially in medical applications like pacemaker, military applications, security systems have lowering the power consumption as the main criterion as long as the performance is within acceptable limits. Devices like portable phones and handheld devices warrant the operational life to be increased, and this increase should not compromise on the operation or performance of such devices. Hence, designing chips for low power is one of the most important areas of interest in modern times, especially with the technological advancements and more components being embedded into the same chip is concerned. Whenever we are dealing with digital ICs, arithmetic circuits are present in almost all the designs, and hence an adder and a magnitude comparator are two such designs which will be present in any computing application, like in an ALU unit in a computer, microprocessors or any other device dealing with arithmetic operations, address translations etc. So, there is a need to reduce power consumed by these devices so that it presents a starting point to reduce overall power consumption of the designs. This has been studied in our thesis, by means of finding ways to reduce power consumption of adder and magnitude comparator circuits.

Technology scaling is continuing to progress at an alarming rate, and due to this scaling, performance of the designs keeps increasing at almost the same or even slightly lower costs. But, the problem with technology scaling is that as the feature size keeps reducing, it becomes increasingly difficult to fabricate designs, not only due to issues related to sensitivity to different types of variations, but also due to the increased leakage power consumption in such low feature sized devices.

Power in a CMOS circuit can be dynamic, which is mainly contributed due to the presence of capacitors in the design. These capacitors need to be charged and discharged based on the inputs applied, and there is a lot of switching activity associated with this which leads to power consumption. In higher feature sizes, the majority of power consumed is attributed to dynamic power. Another type of power, short circuit power, comes into picture when, momentarily, both NMOS and PMOS transistors involved in a designed can be partially turned on, due to slow rise times of input signals. During this situation, there is a small amount of current flowing directly from the power source to the ground, causing adverse affects to the chip if persistent for longer periods. The last type of power consumption is due to the current drawn by a circuit even when it is off or in idle period. This power is mainly contributed by subthreshold, gate, reverse-biased, and junction leakage currents. This power was not very significant when higher feature sized transistors were employed, but with technology scaling, this component of power has become comparable to dynamic power consumption, though short circuit power consumption is generally less compared to the other two types.

There have been a number of methods that are proposed to reduce the power consumption of circuit designs. Some of them are: dynamic voltage and frequency scaling, reducing the operating voltage of the circuit, using voltage islands and clock gating to reduce the switching/ active power consumption. The techniques to reduce static power consumption include power gating, multi-threshold transistor usage, biasing. Clock gating and power gating are some of the most widely used techniques in the VLSI industry, and are implemented in our designs to check their effectiveness at very low voltages.

## 1.2 Review of Clock Gating and Power Gating in Ultra Low Voltage Region

Leakage power consumption has to be reduced during standby periods, when no processing is occurring, especially in low voltage regions when more transistors cause more leakage power [3]. One of the popular methods of accomplishing power gating in the ultra low voltage region is a hardware controlled approach, in which individual functional units are made to sleep for short amounts of time. While performing power gating in this region, there is a trade off that exists between size of the footer, achievable leakage reduction and performance penalty that is incurred as a result of voltage drop across the footers as presented in [4].

Traditional CMOS circuit power gating has some disadvantages, one of which is the charge being stored on MOSFETs even during idle time, and the other is the overhead due to the switch from active to cut off mode of operation. A new style of power gating structure, Sense Amplifier based Pass Transistor Logic (SAPTL) was presented in [3] owing to its smaller footer size and boot-up capacitance requirement associated with it, and also because it can overcome the disadvantages posed by traditional CMOS gating structures. The work in [4] presents a detailed analysis by observing the behavior with and without cut off structures, and then three different cut off structures, including MTCMOS, DTCMOS were proposed to check leakage reduction that can be achieved. It also establishes that it is necessary to optimize both the footer width and also supply voltage (Vdd) to achieve the minimum leakage energy.

Finally, [5] presents a new power gating technique that can be used in ultra low voltage region to reduce leakage in sleep mode. It states that normal PG structures, such as the one using high-Vth scheme, does not work well in the ultra low power region due to long time to switch between different modes of operation causing voltage fluctuations and degrades frequency of operation. It considers different configurations such as a single low-Vth footer, and series-connected NMOS footers with low-Vth transistors. A new technique was also proposed based on the criticality of paths to show its effectiveness at the ultra low voltage region of operation.

The clock gating technique deals with shutting off the clock to some blocks of the circuit so that switching activity is reduced. This technique is especially useful when there are blocks used intermittently in a design. When the values latched through flip flops do not change values during the current clock period, there is no need to apply the clock to those cells, as the values are held until the next clock edge. [6] presents a novel clock gating cell optimized to use for low power and low voltage applications, and compares it to conventional clock gating cells. It consumes lower power compared to conventional cells and is advantageous. [7] presents a novel sequential selective clock gating method which is effective at ultra low voltages to maximize savings at such low voltages. Simulations were performed on several multiprocessor circuits and results were presented. Finally, [8] proposes different flip-flops that are configured to enable energy recovery from the clock network, resulting in significant energy savings. Most of these clock gating schemes were focused on slightly higher voltages, which presented a good opportunity for us to consider clock gating effects at lower voltages.

### **1.3** Subthreshold Region of Operation

The reduction of operating voltage is one such extremely useful technique as dynamic power is quadratically related to the supply voltage, thus providing a chance to save more power by reducing the voltage. The region in which a transistor operates depends on the supply voltage. When the supply voltage is reduced, the transistor operating mode shifts from strong inversion, to moderate and finally to weak inversion region. But, reducing the voltage too much has adverse effects as the delay associated with the designs increases quadratically as we reduce the voltage below threshold voltage, coupled with an increase of leakage power consumption. This is a problem with the weak inversion region, and is due to the increased sensitivity on PVT variations and also exponential dependence of delay and current on the threshold and supply voltages. Therefore, a balance has to be struck between reducing the operating voltage and performance requirements of the design. In particular, the threshold voltage is non-scalable and also the subthreshold slope presents a lot of limits, which has caused supply voltage scaling to slow down to maintain device performance without increasing leakage power too much [9]. Care has to be taken about the design aspects of circuits in this region of operation to avoid severe performance loss due to variations.

The subthreshold or weak inversion region of operation presents an interesting area of focus for low power applications, but the performance penalty is huge. Ultra low power design can be done in near-threshold region so that performance can be put in check and also operation can be done close to the minimum energy point, which occurs for CMOS logic families in the subthreshold region of operation [10]. Subthreshold digital logic design has grown in popularity ever since. This thesis aims to operate designs as close to this region as possible by focusing primarily on reducing power consumption when performance is within acceptable limits.

#### 1.4 Thesis Organization

The main aim of our thesis was to operate the designs in very low voltage region, which would make them operate either in or as close as possible to the subthreshold region of operation. A very important and interesting question is related to the effectiveness of various power reduction techniques at such low voltages. This chapter gives a brief introduction to the work presented in this thesis, followed by the remaining chapters organized as follows.

Chapter 2 introduces various concepts and presents the background related to this research, including the basic design of circuits considered, power reduction techniques, and EDS design.

Chapter 3 extensively deals with selection of proper operating voltage and model file which would produce a balance between performance and power consumption. CSA and comparator designs are elaborated, followed by analysis of the worst case delay variation with the number of stages in a CSA. Finally, EDS design for CSA is presented toward the end. Also, various simulations performed and observations made are detailed.

Chapter 4 deals with the application of various power reduction techniques like power gating and clock gating for the designs under consideration, at very low voltages. The problems encountered with these methods, if any, are presented, and details about simulations and measurements performed, followed by observations, are given toward the end. Chapter 5 presents conclusion to this thesis and provides any possible future work in this area.

### Chapter 2

# Background

This chapter discusses about background related to ultra low voltage region of operation and also covers topics related to our research work. The motivation for our work has already been presented in the previous chapter. Section 2.1 deals with aspects related to operating the designs in the ultra low voltage region. Section 2.2 presents topics related to various adder configurations with emphasis on carry skip adder which is used for our research work. Section 2.3 deals with design of a magnitude comparator which is also employed in our work, followed by power reduction techniques: power gating in Section 2.4 and clock gating in Section 2.5. This chapter is concluded by giving details about Error Detection Sequential (EDS) circuit in Section 2.6.

### 2.1 Ultra Low Voltage Design

This section deals with details about the ultra low voltage region of operation of CMOS circuits. Digital integrated circuits mostly use CMOS circuits as building blocks. The feature size of CMOS transistors is reducing day by day, and this coupled with increasing chip density where more circuitry is being fit into a smaller space, and higher operating frequencies, are a cause of concern as power consumption increases as a result of these factors. This may lead to even permanent failure of the chip due to increased temperature of the chip. Therefore, power consumption has to be minimized using different possible techniques, and one of such techniques is by operating the design in the

subthreshold region of transistor operation. If speed or performance is not the major factor relating to a design (e.g. for biomedical applications), subthreshold operation provides a very good energy-saving approach to many energy constrained applications [11], where we reduce the supply voltage considerably without worrying too much about performance.

The minimum energy per operation point (MEP) in the case of static CMOS technologies is achieved in the subthreshold region of operation [10] [12]. A device enters into the subthreshold region of operation when its gate to source voltage (Vgs) is less than its threshold voltage (Vth). During this condition of operation, minority carriers present in the inversion channel are not very high, but they do correspond a current flow and hence this region is known as *weak inversion*. When the supply voltage (Vdd) is less than the threshold voltage (Vth), the major component of current is provided by subthreshold current as junction leakage and gate current are smaller when operating in the subthreshold region. The current flow is not due to the creation of inversion channel, but due to diffusion.

In the subthreshold region, subthreshold current is exponentially related to Vdd, Vth and gate to source voltage (Vgs). Our aim was to reduce the supply voltage and operate the circuits in or as close to the subthreshold region of operation as possible and to see if circuits really operate at such low voltages and if they do, can there be further savings that can be achieved by operating in this region.

### 2.2 Adder Configurations

This section gives details about different adder configurations with focus on carry skip adder. The work that was previously done is presented including some analysis about adder delay minimization. Our main aim is to operate the adder in very low voltages.

An adder is one of the most basic and widely used arithmetic component in all computational applications. Different types of adders like ripple carry adder, carry look-ahead adder, carry-select adder have been proposed. Ripple carry adder is very slow as the carry generated must ripple through each and every bit in case of 16-bit adder, thus increasing the delay, especially at low voltages. Carry look-ahead adder is quick, but the design complexity is very high, as it has a lot of gates associated with it for generating propagate and generate signals. Other types of adder consume a lot of power when operating at very low voltages due to the high number of gates associated in the design.

Several full adders were designed to work at very low voltages such as the one presented in [13], but the problem with this design was that it was not functioning well, in that the transition of output signals was not happening completely to logic high level for some of the input patterns applied when we used model files from NCSU and ASU PTM that have been provided in [14] and [15]. As the designs presented in [16] and [17] and others have pass transistor logic involved in the design, all of those circuits suffer from severe threshold loss problem while cascading. Also, the traditional 28-transistor-based CMOS adder presented in [18] was simulated. It was functioning well when the supply voltage was reduced below 0.5V, but even for a single bit adder, the number of transistors required was 28 which is a large number. If we consider a 16-bit cell, the area and power consumption would be very high and hence cannot be used where power is the main criterion. Hence, after considering all these designs, we decided to use carry skip adder as it presents a good balance between area, performance and power.

The carry skip adder we considered for our research was based on [19]. There were a few circuit modifications that we had done to make them operate for different model files and a wide range of operating voltages. Firstly, the XOR gate used in the design consumes slightly more power, and hence we performed simulations on XOR configurations provided in [20] and came up with a design that consumes lesser power than the former. Secondly, an inverter was provided in [19] at the end of each stage which might increase the delay associated with the worst case. So, we used the normal signal originating from a stage and used normal inputs instead of the inverted ones for the next stage inputs. This change was done keeping in mind that the worst case propagation delay is the most important aspect that needs to be concentrated while dealing with a carry skip adder.

The way full adders are grouped together into blocks and the number of levels involved in the design play an important role in determining the worst case propagation delay in a carry skip adder. The work presented in [21] uses dynamic programming algorithms to configure carry skip adder, which does not produce optimum results for actual values of skip and ripple time. A geometric approach was proposed in [22] with an assumption about ratio of skip time and ripple time and hence does not produce accurate results. This idea was extended by [23] for arbitrary skip and ripple time ratios but again bases its results on computer algorithms. An extensive mathematical analysis is presented in [24] to find out the optimal block size in a constant block and also variable block CSA.

The work in [25] presents an optimization strategy only for the case of constant block size, and suggests to use variable block size adder to further improve performance. The authors in [25] provided the relative values of maximum propagation time for deviations from the optimum group size for equal groups, but this was done through mathematical analysis only. Hence, overall, for all different kinds of work already done and proposed, delay minimization by all these previously mentioned papers is based on mathematical analysis or complex computer arithmetic programs but not through simple simulations of the design for different block sizes. This was the motivation for our design to be simulated under different block sizes and number of stages to determine the optimum configuration.

### 2.3 Magnitude Comparator Design

Magnitude comparator (i.e., unsigned) is a very important arithmetic component which is used to compare two positive numbers and is used in almost all computational applications. The comparator circuit is a relatively easier design when compared with CSA as it is not very complex in structure and understanding.

The working of a comparator design can be explained as follows. If we consider a 4-bit comparator, which means it compares two 4-bit numbers, the comparison begins from the MSB bit pair. If one of the bits is a 1 and the other is a 0, it means the former number is greater than the latter straightaway. Same is the case when first bit is less than the other bit. In this case, former is less than the latter and both these cases have very small delay associated with them. When the MSB bit pair have the same bit associated with them, the comparison goes to the next significant bit and so on. Hence,

if we select the bits in such a way that except for the LSB bit pair, all the other bit pairs are the same, and the worst case delay occurs.

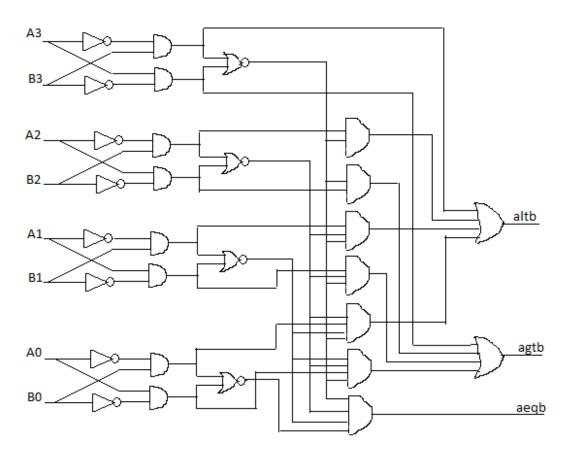

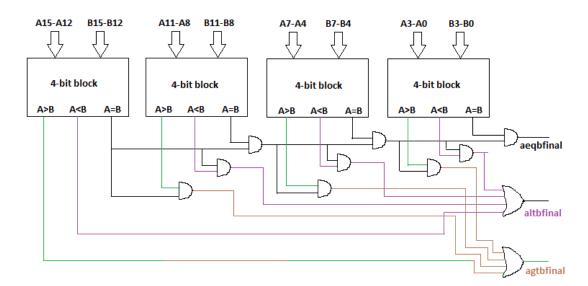

From the above description, we begin by employing inverters on the input signals in a bit pair. The alternating signals between inverted and non inverted inputs of both bits are then AND-ed together, followed by NOR gates. Finally, these are sent through AND and OR gates to get the desired signals indicating whether they are equal or one number is greater/less than the other. Figures 2.1 and 2.2 show the gate diagram of an individual 4-bit block and block diagram of a 16-bit comparator using 4-bit blocks and logic gates.

FIGURE 2.1: Gate diagram of a 4-bit comparator block

FIGURE 2.2: Block diagram of 16-bit comparator

### 2.4 Power Gating

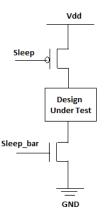

The technique of power gating is discussed in this section, and is one of the most effective and widely used leakage reduction methods. Fig. 2.3 shows a general configuration used for the power gating technique. The crux of this technique lies in disconnecting the logic circuit block from the power rails in standby mode. This is accomplished by employing additional transistors operating as switches which offer a high resistance in the standby mode. This high resistance disconnects the virtual power rails from the global power rails [26]. These additional transistors can be placed either in between the pull-up network and supply voltage (Vdd) terminal, called *header* configuration, or between the pull-down network and ground (GND) terminal, called *footer* transistor. In addition to providing a high resistance in standby mode, these transistors create the stacking effect, which results in an increase in the threshold voltage of the transistors in stack. This combination of resistance and threshold voltage increase is the result of leakage current reduction with this method [26].

The operation of this method can be explained as follows. During active mode or normal operation of the circuit, the sleep transistors are turned on. The transistors in the on condition offer a low resistance and hence the voltage of virtual supply rails is almost the same as that of global supply rails. As a result of this, normal operation of the

FIGURE 2.3: Power gating for a design

circuit is ensured without a significant impact on the circuit performance [27]. During the standby mode, the sleep transistors are turned off by asserting their gate signals low in case of footer transistors. This presents a large resistance between the global and virtual supply rails which ultimately cuts off the supply to the logic block, thus reducing leakage power. The virtual ground terminal voltage should not be too low under this situation which might not produce requisite savings with this method. Hence, the width of footer transistor has to be adjusted in case virtual ground terminal potential is small to make sure savings are achieved.

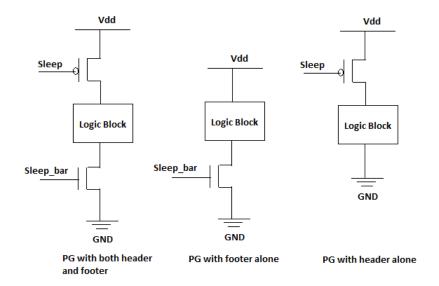

There are several issues that have to be taken into consideration while using this method. The size of a switch affects the circuit delay in active mode and the leakage current in sleep mode, so it should be determined carefully [28]. If the transistors are sized to be very small, the performance is affected as the high-to-low transition delay of the circuit is increased due to the voltage drop on the sleep transistor, decreasing the effective supply voltage of the logic gate [29]. If they are made very large, the result is an area overhead, small leakage power saving, and also increase in dynamic power consumption to turn the transistors on and off [29]. Hence, they have to be sufficiently big but not too big that it has adverse effects on the circuit area. There can be different configurations for power gating: one is employing both header and footer sleep transistors, the second is employing only a footer switch and the last is using only a header switch. Fig. 2.4 shows all the three possible configurations for the power gating technique. We have selected the configuration which employs only a single transistor, the footer transistor as it is sufficient and also smaller in area for the same switching current, resulting in a reduction

of area and active mode voltage drop. In addition to these features, a single big switch is generally used (implemented as multiple switches in parallel) as it is one of the most widely used method in industrial applications [28].

FIGURE 2.4: Different power gating configurations for a circuit

### 2.5 Clock Gating

This section presents a brief introduction to a very well known power reduction technique, clock gating, and is primarily employed when dynamic power consumption of a design has to be minimized. The clock gating technique is widely used when dealing with minimizing switching power of clock signals associated with flip-flops and their related combinational circuits. Switching power comes into picture when a signal is changing values, so energy has to be supplied or lost to charge/discharge load capacitance associated with the gate [30].

The main idea of clock gating is to reduce the switching activity of a design by minimizing the number of unused clock signals that are switching simultaneously, without losing the performance. In other words, it aims to prevent parts of the design from switching at all, by means of disconnecting them when not necessary, provided proper functionality can be achieved. The clock signal employed in sequential circuits switches every cycle and has an activity factor of one, thus consuming a lot of power, due to power contributed by combinatorial blocks, flip flops and clock distribution network, as the clock signal has to travel throughout the design passing through a lot of interconnects. Clock signal does not carry any information and is primarily used for synchronization purposes [31], and hence unnecessary toggling activity can be reduced by employing clock gating in the way as follows.

We can employ a circuitry which can control when a new signal needs to be clocked into the flip flops. This circuitry generates a gated clock signal. When the stored data or state remains unchanged, we do not need the clock signal, which may consume power unnecessarily due to its toggling activity if turned on. So we can disconnect the blocks that are dependent on clock signal during that time through the use of a clock gating circuitry and its associated gated clock output.

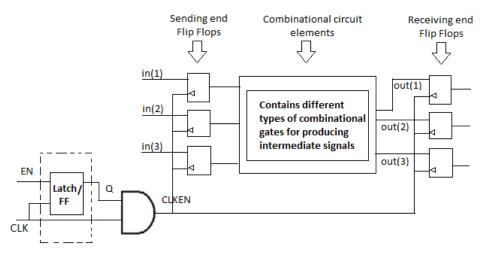

The clock gating circuitry consists of an Enable signal which can be controlled independently and logic gates. The enable signal is applied either through a simple combinatorial gate like AND/ NOR gate or through the use of sequential elements like flip flops or latches, based on the requirement and one such method is represented in Figure 2.5 which contains a latch and an AND gate to generate the gated clock signal.

FIGURE 2.5: Clock Gating representation

The enable signal is controlled in such a way that the gated clock signal produced does not switch continuously and can be turned off to prevent it from reaching some logic modules where the current state is held and not being changed. The most common way to apply the gated clock signal is through the use of a latch and an AND gate. This method saves power well but there is a problem of testability that arises because of this, in the sense the gated clock signal depends extensively on the control input and hence is difficult to control. AND gate based, NOR gate based, Latch-based AND, Latch based NOR, MUX-based are some of the widely used techniques to generate the gated clock signal.

There are some issues that have to be carefully considered while employing clock gating. There should not be glitches occurring in the design due to the enable signal not applied properly. To avoid this, the enable signal is changed only during the low clock phase and not during the high period, as this would cause synchronization problems of the related signals in case of positive edge triggered flip flops.

#### 2.6 EDS

This section gives details about a novel technique of using Error Detection Sequential (EDS) circuits to detect late timing transitions in sequential designs.

One of the most important factors that considerably affects the performance and energy efficiency of VLSI circuits such as microprocessors, servers and other complex designs is the variability in device and circuit parameters. These variabilities in the parameters, also called dynamic parameter variations, arise due to several reasons, either environmental or changes in the workload.

It is of paramount importance to make sure the system operates correctly even in the presence of dynamic variations. This can be achieved by employing a resilient design that contains error detection and recovery circuits. When a timing error has occurred due to a dynamic parameter variation, the resilient circuit detects and corrects the error [32]. One of the most important advantages of using the resilient circuits is that the circuit can be operated at a higher clock frequency or a lower supply voltage than the conventional design.

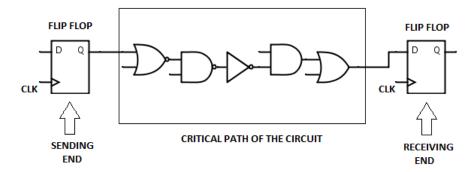

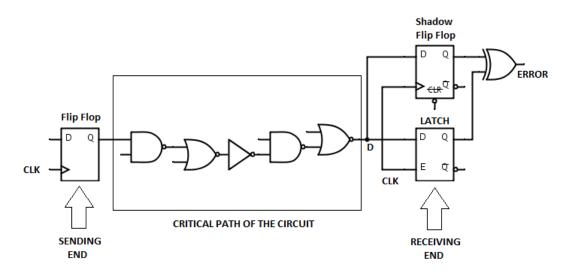

In a conventional design, as shown in Figure 2.6, a critical path is bounded by sending and receiving flip flops. Figure 2.7 shows timing diagrams for a conventional design under normal conditions and during worst case dynamic variations.

FIGURE 2.6: Conventional structure of a design

FIGURE 2.7: Timing diagram for a conventional design

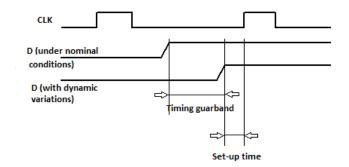

Under nominal conditions of operation, the input at the receiving flip flop, arrives early to the rising edge of the clock. In the presence of dynamic variations in the design, in order to ensure proper functionality of the structure, input to the receiving flip flop should arrive at least a set-up time prior to the rising edge of the clock. If this criterion is not met, a set-up time violation is said to occur, which leads to a wrong value being latched by the flip flop. The difference between the input arrival times in the above mentioned cases is the timing guardband that has to be provided in normal designs to ensure correct behavior under dynamic variations.

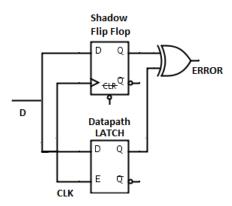

The basic design of an Error Detection Sequential (EDS) circuit as proposed in the Intel 45nm Resilient Microprocessor core is given in Fig. 2.8. The resilient design has a similar structure to the normal design but the major difference between the two is that the receiving flip flop is replaced by an EDS circuit in resilient design. This EDS circuit configuration uses a positive edge triggered latch in the datapath instead of a flip flop and also a shadow flip flop which is triggered by the same input at positive edge of the clock as shown in Fig. 2.9. An XOR logic gate is also employed which compares the outputs of the latch and flip flop and produces a logic high error signal if they differ.

FIGURE 2.8: Gate level EDS circuit design

FIGURE 2.9: Structure of EDS design

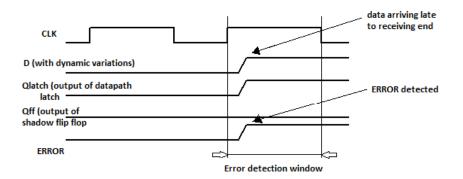

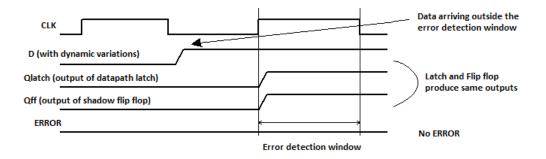

Fig. 2.10 shows the timing diagram for an EDS circuit. In case the input data to the latch arrives late, the shadow flip flop output remains low but the datapath latch, being transparent during the positive clock period, latches on the late changing value. This causes the outputs to be different from the flip flop and latch, causing the ERROR signal to be asserted high as mentioned earlier, thus detecting the error due to late timing transition.

FIGURE 2.10: Timing diagram showing error detection with an EDS circuit

If the same input arrives earlier than when the error detection window begins, the latch and flip flop outputs are the same and hence there is no error. This is represented in the timing diagram Fig. 2.11.

FIGURE 2.11: Timing diagram showing no error with an EDS circuit

The key idea in this technique is that the error due to late timing transitions is detected only during the high clock phase, which is also known as error detection window  $(T_w)$ . There are a set of timing constraints that have to be satisfied by the paths employing EDS circuits as the receiving sequential circuit. The constraint for the maximum delay path in the presence of worst case dynamic variations for EDS is given as

$$T_{max} \le T_{cycle} + T_w - T_{setup,clk} \tag{2.1}$$

$T_{max}$  is the maximum path delay for EDS paths,  $T_{cycle}$  is the clock cycle time,  $T_{setup,clk}$  is the set up time of CLK for the datapath latch based on the rising clock edge.

The minimum path delay timing constraint during worst case dynamic conditions is given as

$$T_{min} \ge T_w + T_{hold,clk} \tag{2.2}$$

$T_{min}$  is minimum path delay for EDS paths,  $T_{hold,clk}$  is hold time of CLK for the latch based on the falling clock edge.

The next few chapters deal with design of circuits, simulations and power reduction techniques applied on the designs considered in our thesis.

### Chapter 3

# Design and Simulation of Carry Skip Adder and Magnitude Comparator Circuits

This chapter deals with the design of *carry skip adder* and *comparator* circuits. The first part deals with design aspects, followed by details about measurements which also cover some implementation concepts for the circuits. Different types of simulations performed on these models are presented next followed by the observations in the end.

### **3.1** Design Aspects of Circuits

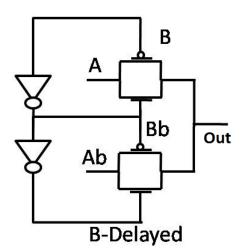

The carry skip adder circuit that we have considered for our thesis is based on the work in [19]. We introduced some modifications in the design which are mentioned here. Instead of the extra inverter that was introduced in the design at the end of each stage as presented in [19], we used the normal carry output from each stage and fed it to the next stage, thus providing a chance to reduce the delay as the inverters would be in the critical path of the design. The second modification was related to the XOR configuration that was presented in [19]. After considering the simulations, delay and power values associated with different types of XOR configurations provided in [20], we

selected the configuration presented in Fig 3.1 as this configuration consumes less power which is our primary requirement, even though the delay is slightly higher and hence features throughout our design.

FIGURE 3.1: XOR configuration used

The *comparator* circuit considered in our thesis is a regular comparator that compares two positive numbers and asserts a signal high based on an operand being greater than, equal to or less than the other operand. It has gates like Inverter, AND, OR, NOR and others to generate signals which indicate if a signal is greater than, less than or equal to the other in 1 stage consisting of 4 bits and is replicated 4 times to generate a 16-bit comparator. The following sections give details about simulations, measurement of power and delay values for both the configurations.

## 3.2 Method of Measurement of Worst Case Delay and Power

The procedure we followed to measure the worst case delay is briefly described here. We used Synopsys HSPICE which is a powerful simulation tool and can be used for a wide range of applications and delay measurement is one such use of the tool. We considered the two signals, (i.e.transition source and transition destination signals) for which the delay has to be measured, overlapped them and selected measurement tool. In this tool, we adjust the options such that we consider the rise/fall transition for respective signals and 50% voltage levels at which the measurement was taken.

For power measurement using HSPICE, we used the built-in measure command provided by the tool which allows us to find out the integral value of a signal over the simulation time which essentially provides the average value of a signal during that time.

### 3.3 Simulation and Measurement Results

After making sure that the CSA and comparator configurations are operating well at various voltages starting from 0.2V or higher based on the model file considered, we had to measure power consumption values and worst case delays at various voltages for all model files using the methods specified earlier. But, considering only a few voltages is sufficient in arriving at a reasonable combination of operating voltage and model file for further analyses which are based on a few factors explained below.

#### 3.3.1 Power Tables

Firstly, since operating the circuit at very low power is our main criterion, we have to make sure the operating voltage is low which has a great impact on reducing power owing to the square dependence of power on operating voltage. These operating voltages have to be chosen in such a way that the least possible values (say 0.2V, 0.3V or 0.4V) for a particular model file are considered, but care has to be taken that they are indeed voltages at which circuits operate well for those models. We represented such voltages as voltages of interest given in Table 3.1, and hence considered power and delay values for these to arrive at the desired pair of voltage and model file.

Secondly, if the operating voltage was greater than 0.5V, we did not consider those even though the circuits were functioning well as they would consume more power, and our primary aim was to achieve very low power and operate in or as close as possible to the subthreshold region of operation.

|            | Thresho | ld Voltages (V) |                          |               |

|------------|---------|-----------------|--------------------------|---------------|

|            |         |                 |                          | Lowest        |

|            |         |                 |                          | Voltages      |

| Model file | NMOS    | PMOS            | Voltages of Interest (V) | resulting in  |

|            |         |                 |                          | subthreshold  |

|            |         |                 |                          | operation (V) |

| ASU PTM    | 0.3423  | -0.23122        | 0.2,0.3,0.4              | 0.2           |

| NCSU VTL   | 0.322   | -0.3021         | 0.3,0.4                  | 0.3           |

| NCSU VTG   | 0.4106  | -0.3842         | $0.3,\!0.4$              | 0.3           |

| NCSU VTH   | 0.6078  | -0.5044         | $0.6(\mathrm{high})$     | -             |

TABLE 3.1: Voltages of interest for different model files

The other factor considered was that the performance of designs had to be within reasonable limits as designs which are extremely slow do not present useful opportunities. Hence, we had to consider the worst case delay values and select a value which is reasonably good and at reasonably low voltage.

Tables 3.2 and 3.3 show the power consumption values for the adder and comparator designs computed at voltages of interest for various model files.

|            | Thresho | ld Voltages (V) |                          |                           |

|------------|---------|-----------------|--------------------------|---------------------------|

| Model file | NMOS    | PMOS            | Voltages of Interest (V) | Power<br>consumed<br>(uW) |

| ASU PTM    | 0.3423  | -0.23122        | 0.2                      | 0.4617                    |

|            |         |                 | 0.3                      | 0.9839                    |

|            |         |                 | 0.4                      | 1.954                     |

| NCSU VTL   | 0.322   | -0.3021         | 0.3                      | 0.8898                    |

|            |         |                 | 0.4                      | 1.687                     |

| NCSU VTG   | 0.4106  | -0.3842         | 0.3                      | 0.4218                    |

|            |         |                 | 0.4                      | 0.7586                    |

| NCSU VTH   | 0.6078  | -0.5044         | 0.6(high)                | 1.529(not<br>considered)  |

TABLE 3.2: Power consumption for CSA at voltages of interest

#### 3.3.2 Explanation of Worst Case Delays

This section provides explanations for the worst case delays of *carry skip adder* and *comparator* configurations along with some example input patterns for showing various cases possible in an Adder. A *carry skip adder* has blocks of full adders forming a stage,

|            | Thresho | ld Voltages (V) |                          |             |

|------------|---------|-----------------|--------------------------|-------------|

|            |         |                 |                          | Power       |

| Model file | NMOS    | PMOS            | Voltages of Interest (V) | consumed    |

|            |         |                 |                          | (uW)        |

| ASU PTM    | 0.3423  | -0.23122        | 0.2                      | 0.3421      |

|            |         |                 | 0.3                      | 0.7201      |

|            |         |                 | 0.4                      | 1.401       |

| NCSU VTL   | 0.322   | -0.3021         | 0.3                      | 0.5519      |

|            |         |                 | 0.4                      | 1.081       |

| NCSU VTG   | 0.4106  | -0.3842         | 0.3                      | 0.15        |

|            |         |                 | 0.4                      | 0.263       |

| NCSU VTH   | 0.6078  | -0.5044         | $0.6(\mathrm{high})$     | 0.4405(not  |

|            | 0.0078  | -0.5044         | 0.0(mgn)                 | considered) |

TABLE 3.3: Power consumption for comparator at voltages of interest

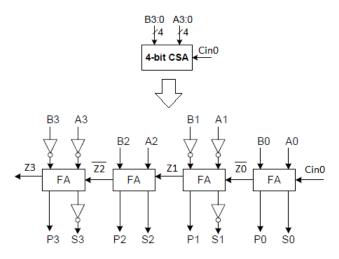

which is linked to the other stage through a multiplexer. This is shown in Figures 3.2 and 3.3 where a 16-bit adder is organized in 4 stages, each stage containing 4 full adder cells.

FIGURE 3.2: The structure of a 4-bit CSA representing a stage

FIGURE 3.3: The 16-bit CSA formed through stages connected using MUXes

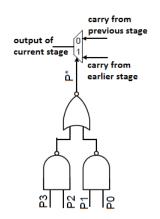

Each stage can either propagate the carry coming from the previous stage or skip it based on a group propagate signal which is calculated as soon as the input bits are available using NAND and NOR gates, as shown in Figure 3.4.

FIGURE 3.4: Generation of group propogate signal through NAND-NOR gates

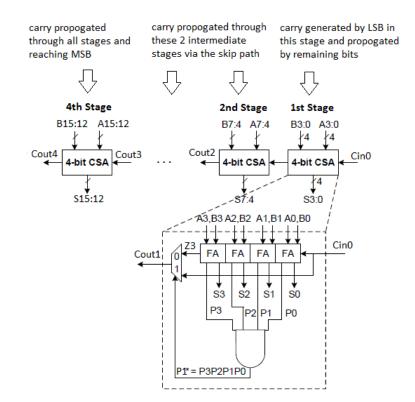

This group propagate signal is used as the select line for the multiplexer provided at the end of each stage. The multiplexer selects from the carry of the previous stage or from earlier stages based on the select line being 0 or 1 respectively. The worst case delay occurs in the CSA when a carry is generated in the least significant bit (LSB) and is propagated through the intermediate stages all the way to the most significant bit (MSB). This means that the intermediate stages have to propagate the carry that is generated by the least significant bit. The condition to be satisfied is shown in Figure 3.5.

FIGURE 3.5: Condition under which worst case delay occurs for a carry skip adder

If an intermediate bit pair in a stage generates its own carry, that means it is not propagating the carry from earlier stages, or the carry generated by the LSB is stopped at this location instead of propagating it further. This does not correspond to the worst case delay as there is a new carry generated which will then proceed toward the MSB, instead of the old one. This is shown in Figure 3.6, and happens when we have bits 11 associated with the inputs.

If an intermediate bit in a stage kills the carry, it means the carry propagation path has ended prematurely as this bit cannot propagate the carry from LSB any further. This condition is also represented in Figure 3.6, and happens when we have bits 00 associated with the inputs.

| Example 1: | Carry<br>A15:0<br>B15:0<br>Cin0 | 1111 11<br>0110<br>1001 | .11(g) 1(g)1<br>1001<br>0111 | 1(g)0(k)<br>1110<br>1010 | 111(g)1<br>0010<br>1111<br>1 |  |

|------------|---------------------------------|-------------------------|------------------------------|--------------------------|------------------------------|--|

| Example 2: | Carry<br>A15:0<br>B15:0<br>Cin0 | 001(g)0<br>1010<br>0011 | 01(g)11(g)<br>0111<br>0101   | 1(g)000<br>1000<br>1110  | 000(k)1<br>0101<br>0000<br>1 |  |

| Example 3: | Carry<br>A15:0<br>B15:0<br>Cin0 | 1111<br>0000<br>0111    | 1111<br>0000<br>1111         | 1111<br>0000<br>1111     | 1111<br>0001<br>1111<br>0    |  |

FIGURE 3.6: Different input patterns showing carry generation(g), propogation(p) and kill(k) by bit pairs

The explanation for some input patterns goes as follows: In Example 1 of Figure 3.6, the LSB generates a carry which has to be propagated to the MSB. But, bit 2 input pair generates a carry of its own, thus beginning a new path for carry, which now starts from 2nd bit instead of the first. This is obviously less than the maximum delay possible. Also, at bit 5, the carry from earlier stages is killed as this bit pair does not propagate the carry. Hence, a new path starts again at bit 6 and ends at bit 8, which starts a new path, again interrupted by bit 9, the carry generated by which continues to the MSB. This delay is way less than the maximum delay due to discontinuity in the carry path from LSB to MSB.

In Example 2 of Figure 3.6, the LSB generates a carry and is killed by the 2nd bit input pair. A new carry is generated by 8th bit pair and is ended at 9th bit owing to a newly generated carry by this input bit pair. But, this ends in bit 11 due to carry generated here which is killed again at bit 12. Bit 14 pair generates an input carry which is not propagated to the MSB at all. In this case too, the delay is not even close to being maximum delay.

This explanation suggests that in order for the intermediate stages to propagate the carry generated by the LSB, the bit-pairs in these stages have to make sure that they neither generate their own carry nor kill the carry. This condition is met when we have 10 associated with the input bits. This condition is also shown in Figure 3.6.

In Example 3 of Figure 3.6, the LSB generates a carry which is not stopped at any other bit location as none of the bit pairs generates or kills the carry coming from lesser order bits.

When 1 and 0 are associated with the input bits, propagate (P) signal which is A(XOR)B is 1, and hence all P's are 1s for these inputs. This results in group propagate signal being asserted high. As a result of this, the intermediate stages skip the carry from the previous stage and propagate the carry associated with the earlier stage instead.

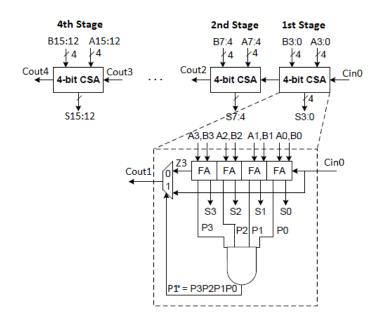

This is the main distinction between a *ripple carry adder* and the CSA in that, since the group propagate signal is readily calculated upon availability of input bits, some blocks can be skipped thus reducing the delay compared to other kind of adders. This way, the worst case delay happens when the LSB generates a carry which ripples through the 1st stage through all the 4 full adder cells, is skipped by the intermediate 2 stages which ensures carry propagation and then ripples through the final 4 full adder cells in the last stage. This path is depicted in Figure 3.7.

FIGURE 3.7: Worst case delay represented for carry skip adder

### 3.3.3 Worst Case Delay Tables

in Table 3.4. These values would be different if there are other elements included in the circuit.

|            | Thresho | ld Voltages (V) |                          |                                                |

|------------|---------|-----------------|--------------------------|------------------------------------------------|

| Model file | NMOS    | PMOS            | Voltages of Interest (V) | Worst case<br>delay (ns)                       |

| ASU PTM    | 0.3423  | -0.23122        | 0.2                      | 6.2469                                         |

|            |         |                 | 0.3                      | 1.3264                                         |

|            |         |                 | 0.4                      | 0.5351                                         |

| NCSU VTL   | 0.322   | -0.3021         | 0.3                      | 3.4295                                         |

|            |         |                 | 0.4                      | 1.04                                           |

| NCSU VTG   | 0.4106  | -0.3842         | 0.3                      | 21.646                                         |

|            |         |                 | 0.4                      | 3.8269                                         |

| NCSU VTH   | 0.6078  | -0.5044         | $0.6(\mathrm{high})$     | -(not<br>considered due<br>to high<br>voltage) |

TABLE 3.4: Worst case delays for CSA at voltages of interest

In the case of a *comparator*, the worst case delay occurs when the least significant bit (LSB) is the one which determines the result of a comparison. If one of the most significant bits (MSB) of the 2 operands is different, it means that it is either less than or greater than the other operand. In this case, there is not much delay in generating the output on application of the inputs. Same is the case for intermediate bits too. The delay will be higher than the previous case but is not the worst case delay.

When we have all the higher stages with the same bits and just the LSB in the last stage with different bits, the computation has to wait until the last set of bits (LSB) to determine the result of the comparison. This situation is shown in Figure 3.8 and corresponds to the worst case delay measured from A15 input to altofinal output.

The worst case delays measured for comparator for the voltages of interest without any flip flops are given in Table 3.5.

### 3.3.4 Selection of Operating Voltage and Model File Pair

Based on the Tables 3.4 and 3.5, we selected the VTG model file and 0.4V as the pair which would be consistent with our requirements of power-delay balance. This pair is

FIGURE 3.8: Worst case delay represented for the magnitude comprator

|            | Thresho | ld Voltages (V) |                          |                                                  |

|------------|---------|-----------------|--------------------------|--------------------------------------------------|

| Model file | NMOS    | PMOS            | Voltages of Interest (V) | Worst case<br>delay (ns)                         |

| ASU PTM    | 0.3423  | -0.23122        | 0.2                      | 4.5623                                           |

|            |         |                 | 0.3                      | 0.7702                                           |

|            |         |                 | 0.4                      | 0.2525                                           |

| NCSU VTL   | 0.322   | -0.3021         | 0.3                      | 1.4864                                           |

|            |         |                 | 0.4                      | 0.4486                                           |

| NCSU VTG   | 0.4106  | -0.3842         | 0.3                      | 9.0791                                           |

|            |         |                 | 0.4                      | 1.5945                                           |

| NCSU VTH   | 0.6078  | -0.5044         | $0.6(\mathrm{high})$     | -(not<br>considered<br>since voltage<br>is high) |

TABLE 3.5: Worst case delays for comparator at voltages of interest

used as the standard for all other operations performed henceforth on the circuits.

# 3.4 Observations

This section presents the observations that we could come up with based on the simulations and analysis performed. Firstly, from the minimum operating voltages at which the circuits operate, we could observe that the circuits operate at very low voltages such as 0.2V as well for ASU PTM model file. But, the delay associated is very high and hence not profitable to use at this voltage. These voltages for VTL, VTG and VTH model files from NCSU were 0.3, 0.3 and 0.6V respectively, but delays or power values were higher in the first 2 cases and the voltage is too high in the last case and hence can consume more power compared to other voltages.

We observed the patterns that were found for different model files as the voltage is varied in comparison to the threshold voltage. Based on Table 3.5, we explain some of the observations in the following discussions.

If the threshold voltage increases at a particular voltage of operation, the delay would increase. When the operating voltage is less than the threshold voltage, the device operates in the subthreshold region of operation. This is the case where we consider operating voltage of 0.2V for ASU\_PTM model file, and 0.3V for NCSU\_VTG model file. For these voltages, since the circuit operates in the subthreshold or weak inversion region, the driving strength of the transistors is not as high as it would be in normal operating conditions, and hence the circuit is slow resulting in higher delay values. When we increase the voltage for the same model files, the design enters normal inversion operation which causes it to speed up, thus reducing the delay.

The worst case delays were as high as 6-7 times in the subthreshold region of operation for both ASU\_PTM (0.2V) and NCSU\_VTG (0.3V) model files, when compared to delays observed when the operating voltage is increased to 0.3V and 0.4V for ASU\_PTM and NCSU\_VTG model files respectively, so that they are very close to or higher than the threshold voltages of the transistors. This result confirms the delay difference for different operating voltages for the designs based on our knowledge.

Secondly, we observed that as the operating voltage increases, power increases and worst case delay decreases even at very low voltages.

Thirdly, we used several different input patterns to check and see if they represent any anomalies as far as the worst case delay is concerned, but none of them gave results that were larger than what we had with the worst case inputs we considered in our simulations. This suggests the procedure and measurement techniques we followed were correct and accurate.

# 3.5 Delay Dependency on Number of Blocks per Stage