## **UNIVERSITY OF CINCINNATI**

Date:\_\_\_\_\_

\_\_\_\_\_

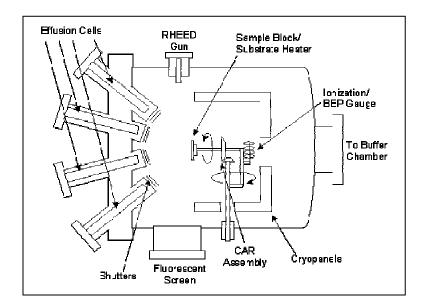

hereby submit this work as part of the requirements for the degree of:

in:

It is entitled:

I,

This work and its defense approved by:

Chair: \_\_\_\_\_

# Spontaneous Spin Polarization due to Lateral Spin-Orbit Coupling in InAs Quantum Point Contacts

A dissertation submitted to the

Division of Research and Advanced Studies of the University of Cincinnati

in partial fulfillment of the requirements for the degree of

### DOCTOR OF PHILOSOPHY (Ph.D.)

**in the Department of Physics** of the College of Arts and Sciences

2007

by

## S.M. Saydur Rahman

M.S., University of Cincinnati, Cincinnati, OH B.Sc. and M.Sc., Dhaka University, Dhaka, Bangladesh

Committee Co-Chair: Prof. Richard Newrock and Prof. Philippe Debray

### Abstract

This dissertation reports the first experimental observation of spontaneous spin polarization due to lateral spin orbit coupling (LSOC) in side- gated (SG) quantum point contacts (QPCs). The QPC devices are fabricated on InAs/InGaAs quantum well structures using e-beam lithography. The low band gap InAs semiconductor was chosen because of its large intrinsic spin-orbit coupling. The side gates are realized by wet etching technique which is optimized to pattern the QPC devices. The width of the QPC is varied from 200 nm to 500 nm, while the length of the QPC is kept in the range 150-200 nm. The gradient in the lateral potential confinement in a side gated (SG) quantum point contact (QPC) causes a spin-orbit coupling (SOC). This LSOC induces a spontaneous spin polarization of opposite nature at the two edges of the QPC in the absence of any applied magnetic field. We have observed an anomalous conductance plateau at  $G \cong 0.5 (2e^2/h)$  (0.5 structure) in the SG QPCs fabricated on InAs/InGaAs QW structures. The 0.5 structure moves up in perpendicular magnetic field and approaches the normal conduction quantization at  $G = (2e^2/h)$  in high magnetic field, whereas in-plane magnetic field has no effect on it. The evolution in magnetic field clearly indicates LSOC is responsible for the 0.5 structure. We believe it is the asymmetry in the confining potential of the QPC that leads to a net spin polarization giving the 0.5 structure. By electrically modulating the asymmetry of the QPC confinement, we have succeeded in making this structure appear and disappear. Such a QPC can conceivably be used as a spin polarizer or detector on demand by tuning the gate voltages. We also have proposed a dual-QPC device to experimentally validate the spin polarization by electrical means.

Dedicated

То

My Parents

### Acknowledgements

I wish to express my sincere gratitude and profound thanks to Professor Richard Newrock and Professor Philippe Debray for giving me the opportunity to work in their group. I am extremely grateful to Professor Newrock for his support and invaluable suggestions. I am very much indebted to Professor Debray for his expert and close supervision, suggestions and encouragement throughout the course of the work.

I am grateful to the members of my PhD committee: Professor Howard Jackson, Professor Michael Ma and Professor Marc Cahay for their suggestions and advice in academic matters.

I want to thank Dr. Steven Herbert (Chair, Department of Physics, Xavier University) for his valuable time and suggestions. I am also grateful to him for giving me the opportunity to use the metal deposition system and AFM. I like to thank Dr. Mark Johnson, Naval Research Lab, Washington D.C., for providing us the preliminary recipe of the wet etching and also for sending us the first set of wafer (NRL wafer). I would like to thank Professor Rohana Wijewardhana for his personal help and guidance. I am very much thankful to John Marcus for his help and technical support throughout all these years. I also want to thank Robert Schrott for his help in the machine shop.

I am deeply thankful to my parents, Lutfur Rahman and Hamida Khatoon, for their endless love and encouragements, without which I would not come so far. I wish to thank all my siblings, specially my sister Lutfe- who inspired me all the time. I wish my heartfelt appreciation to my wife, Dristi, for her encouragement, love, patience, understanding, companionship and assistance required for the completion of this work. I am truly thankful to her for proofreading the thesis. Without her help and inspiration, it would be extremely difficult to complete this work.

Finally, I wish to thank all the faculty and staff of the Physics department at the University of Cincinnati. I am also grateful to all my fellow graduate students. I am in particular grateful to Mustafa Muhammad, an excellent lab mate, for being helpful and nice throughout all these years. I wish to continue my gratitude to my friends Kazi Sayeed, Chetyia Sahabandhu, Hasan Siddique and Amin Kabir for their companionship, support and humorous discussion during my graduate years. I also like to thank Aseem Talukdar, Seema Bahinipati and Venkat Gangilenka for their friendship.

## List of Contents

| Abstract                                                                | iii  |

|-------------------------------------------------------------------------|------|

| Acknowledgements                                                        | vi   |

| List of Contents                                                        | viii |

| List of Figures                                                         | xii  |

| List of Tables                                                          | xix  |

| 1. Overview                                                             | 1    |

| References                                                              | 6    |

| 2. State-of-the-Art                                                     | 8    |

| 2.1. Introduction                                                       | 9    |

| 2.2. Spin Orbit Coupling                                                | 10   |

| I. What is SOC?                                                         | 10   |

| II. Dresselhaus Spin Orbit Coupling                                     | 11   |

| III. Rashba Spin Orbit Coupling                                         | 12   |

| IV. Lateral Spin Orbit Coupling                                         | 15   |

| 2.3. Anomalous Conductance Plateau and Spontaneous Spin Polarization in |      |

| . GaAs QPCs                                                             | 19   |

| References                                                              | 30   |

| 3. | Semiconductor Microstructures and Device Fabrication                | 37 |

|----|---------------------------------------------------------------------|----|

|    | 3.1. Introduction                                                   | 38 |

|    | 3.2. Growth of InAs Quantum Well (QW) Structures                    | 38 |

|    | 3.2.1. MBE Technique                                                | 39 |

|    | 3.2.2. InAs Quantum Well (QW) Structures                            | 42 |

|    | 3.2.3. Two-Dimensional Electron Gas (2DEG) and its Characterization | 45 |

|    | I. Classical Hall Measurement                                       | 46 |

|    | II. Shubnikov- de Hass Measurement                                  | 48 |

|    | 3.3. Device fabrication                                             | 52 |

|    | 3.3.1. Wafer Cleaning                                               | 54 |

|    | 3.3.2. Resist Spinning                                              | 54 |

|    | 3.3.3. Electron Beam Lithography                                    | 57 |

|    | 3.3.4. Development                                                  | 60 |

|    | 3.3.5. Ohmics and Markers: Deposition and Lift-off                  | 60 |

|    | 3.3.6. Etching                                                      | 62 |

|    | I. Isolation Trenches                                               | 63 |

|    | II. Side Gate Etching                                               | 64 |

|    | 3.3.7. AFM                                                          | 66 |

|    | 3.3.8. Annealing                                                    | 67 |

|    | 3.3.9. Scribing, Packaging and Bonding                              | 67 |

|    | 3.4. Nano-Scale QPCs                                                | 68 |

|    | 3.4.1. Single-QPC Device                                            | 69 |

| •  | 3.4.2. Dual-QPC Device                              | 69  |

|----|-----------------------------------------------------|-----|

|    | References                                          | 70  |

| 4. | Experimental Techniques                             | 73  |

|    | 4.1. Introduction                                   | 74  |

|    | 4.2. Dilution Refrigerator                          | 74  |

|    | I. Principle of Dilution Refrigerator               | 75  |

|    | II. Operation                                       | 76  |

|    | 4.3. Experimental Set-up                            | 78  |

|    | 4.4. Measurement Techniques                         | 81  |

|    | I. Device Quality Control                           | 82  |

|    | II. Conductance Measurement                         | 85  |

|    | References                                          | 89  |

| 5. | Experimental Results and Discussion                 | 90  |

|    | 5.1. Introduction                                   | 91  |

|    | 5.2. Conductance Quantization                       | 92  |

|    | 5.3. Magnetic Field Dependence of the 0.5 Structure | 94  |

|    | I. 0.5 Structure in Perpendicular Magnetic Field    | 95  |

|    | II. 0.5 Structure in Parallel Magnetic Field        | 100 |

|    | III. Discussion                                     | 103 |

|    | 5.4. Temperature Dependence of the 0.5 Structure    | 106 |

|    | I. Results                                          | 107 |

|    | II. Discussion                                      | 109 |

|    | 5.5. Effect of Asymmetry on the 0.5 Structure                               | 109 |

|----|-----------------------------------------------------------------------------|-----|

|    | I. Results                                                                  | 110 |

|    | II. Discussion                                                              | 115 |

|    | 5.6. Detection of the Spin Polarization                                     | 117 |

|    | I. Dual-QPC Device                                                          | 118 |

|    | II. Results                                                                 | 119 |

|    | III. Discussion                                                             | 121 |

|    | 5.7. Comparison: Our 0.5 Structure and the 0.7 Structure Observed by Others | 122 |

|    | 5.8. Summary                                                                | 124 |

| Re | ferences                                                                    | 126 |

| 6. | Future Work                                                                 | 128 |

## **List of Figures**

| 2.1 Energy dispersion of Rashba spin-split subbands: (a) 2D case; black arrows        |    |

|---------------------------------------------------------------------------------------|----|

| represent spin eigen states. (b) 1D case; spin-up and spin-down electrons travel with |    |

| different Fermi velocities                                                            | 13 |

| 2.2 (a) Schematic of the 1D Quantum Wire. The blue arrow shows the channel            |    |

| direction, (b) Lateral confinement in 1D                                              | 16 |

| 2.3 (a) Spin-up and spin-down electrons have different effective potential along the  |    |

| two edges (b) Different spin accumulates along the two edges                          | 17 |

| 2.4 (a) Conductance quantization observed in a QPC fabricated on GaAs/AlGaAs          |    |

| Heterostructure in zero magnetic field. (b) The 0.7 Structure observed in a QPC of    |    |

| length 400 nm fabricated on GaAs/AlGaAs hole system in $B = 0$ . The arrow points to  |    |

| the location of the anomalous plateau                                                 | 20 |

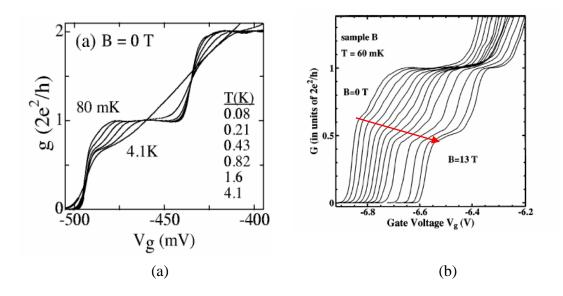

| 2.5 (a) The temperature dependence of the 0.7 Structure in an AlGaAs/GaAs QPC of      |    |

| length 500 nm [51]. (b) Evolution of the 0.7Structure into a $0.5(2e^2/h)$ plateau in |    |

| parallel magnetic field 0-13T                                                         | 21 |

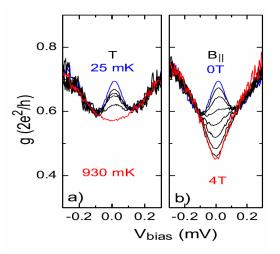

| 2.6 Differential conductance g as a function of source-drain bias voltage observed in |    |

| hole QPCs made on p-type AlGaAs/GaAs heterostructure: (a) at temperatures 25-930      |    |

| mK in zero magnetic field. (b) at 25 mK in parallel magnetic fields 0 - 4 T           | 22 |

| 2.7 Conductance of quantum-wire device as a function of tip bias voltage at 150 mK    |    |

| for different potential landscapes. The green plot is for symmetric potential         |    |

| landscape. The plots have been offset and linearly scaled along x-axis for clarity    | 23 |

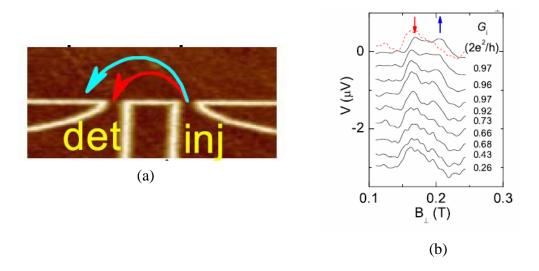

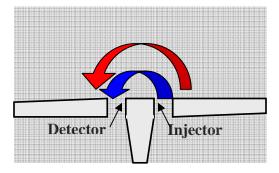

| 2.8 (a) Magnetic focusing geometry showing injector and detector QPCs and the              |    |  |  |  |  |  |

|--------------------------------------------------------------------------------------------|----|--|--|--|--|--|

| schematic trajectories of holes with two spin states. (b) Focusing peak measured at        |    |  |  |  |  |  |

| different injector conductance $G_i$ . The curves are vertically offset by -0.4µV relative |    |  |  |  |  |  |

| to the top one. The G = $0.66(2e^2/h)$ is also plotted without offset (dashed red)         | 28 |  |  |  |  |  |

| 3.1 Schematic of a MBE system                                                              | 39 |  |  |  |  |  |

| 3.2 Growth layer detected by RHEED                                                         | 41 |  |  |  |  |  |

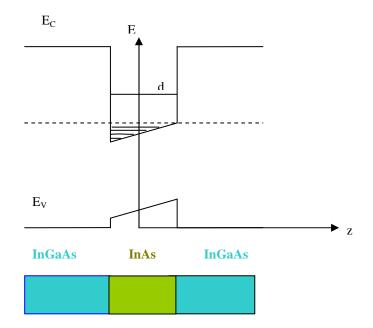

| 3.3 Band Alignment in InAs QW structures                                                   | 42 |  |  |  |  |  |

| 3.4 2DEG density of states                                                                 | 44 |  |  |  |  |  |

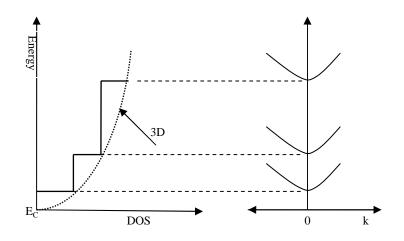

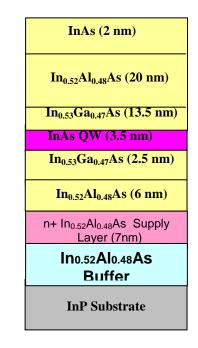

| 3.5 MBE grown InAs/InGaAs QW structure: (a) NRL wafer and (b) Commercially                 |    |  |  |  |  |  |

| bought Cond-1 wafer                                                                        | 45 |  |  |  |  |  |

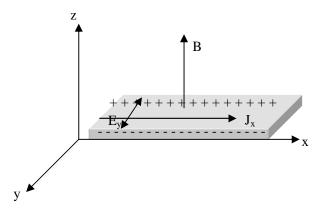

| 3.6 Schematic view of the Hall experiment                                                  |    |  |  |  |  |  |

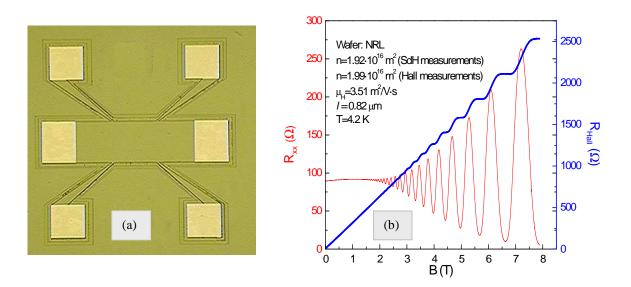

| 3.7 (a) Hall bar device fabricated on InGaAs/InAs QW using the Raith 150 e-beam            |    |  |  |  |  |  |

| lithography. (b) SdH oscillation observed on InGaAs/InAs heterostructures as a             |    |  |  |  |  |  |

| function of Magnetic field at 4.2 K                                                        | 48 |  |  |  |  |  |

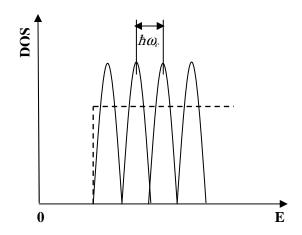

| 3.8 Density of states of 2DEG in the first sub-band in magnetic field. The dashed line     |    |  |  |  |  |  |

| is the DOS in the first sub-band without magnetic field                                    | 50 |  |  |  |  |  |

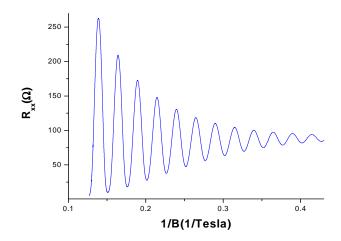

| 3.9 SdH Oscillations are periodic with 1/B                                                 | 50 |  |  |  |  |  |

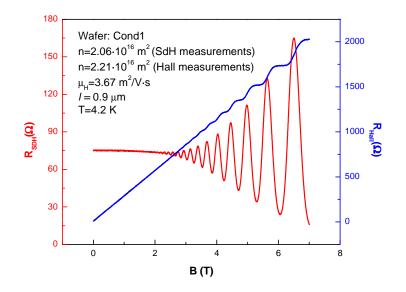

| 3.10 SdH and Hall measurement on Cond.1 wafer                                              | 51 |  |  |  |  |  |

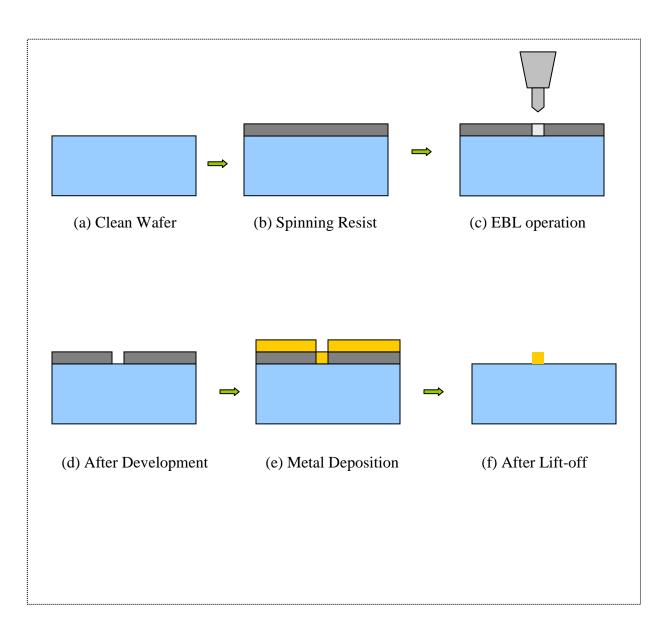

| 3.11 Different processing steps in a typical device fabrication                            | 53 |  |  |  |  |  |

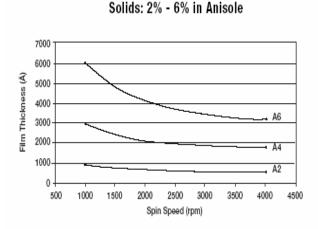

| 3.12 PMMA resist thickness varied with the spin speed as well as with the                  |    |  |  |  |  |  |

| concentration                                                                              | 55 |  |  |  |  |  |

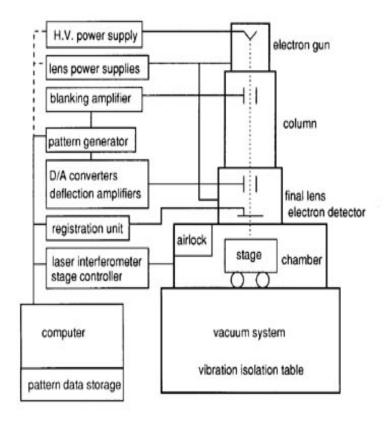

| 3.13 Block Diagram of a typical EBL                                                             | 57 |

|-------------------------------------------------------------------------------------------------|----|

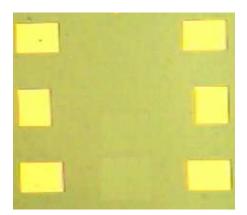

| 3.14 Ohmics after Lift-off                                                                      | 61 |

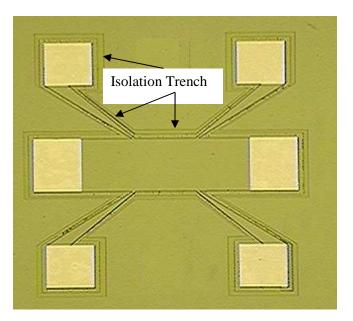

| 3.15 Isolation Trench defines a Hall bar Device                                                 | 63 |

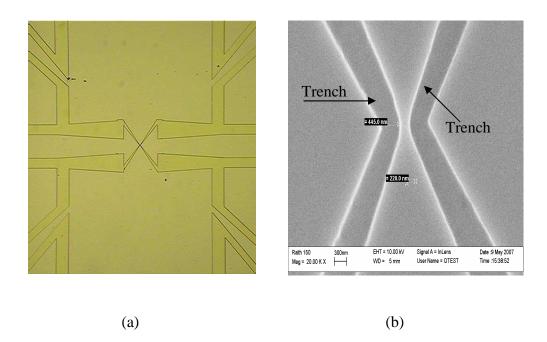

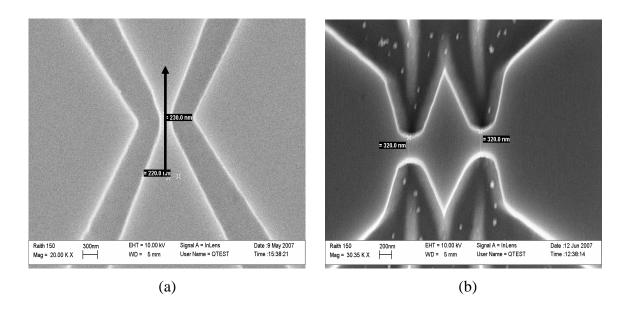

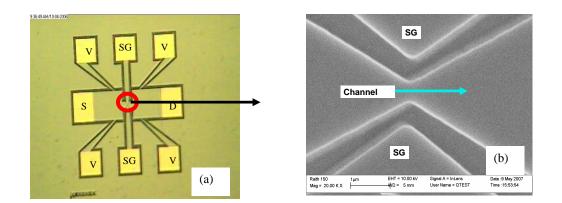

| 3.16 (a) Optical micrograph of trench of a Side Gated (SG) QPC fabricated using the             |    |

| Raith 150 e-beam lithography. (b) SEM image of QPC trench                                       | 65 |

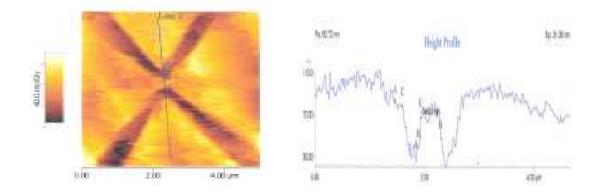

| 3.17 AFM image of a Ring device and depth measured by using the AFM                             | 66 |

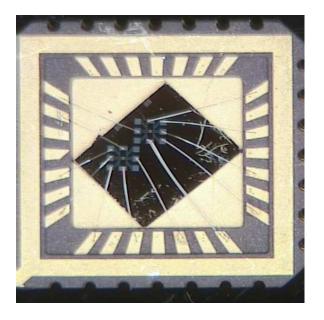

| 3.18 Device glued and bonded in the chip carrier                                                | 67 |

| 3.19 (a) SEM of a Side Gated (SG) single-QPC and (b) SEM of a dual-QPC device                   |    |

| fabricated on InAs/InGaAs QW structures using the Raith 150 e-beam lithography .                | 68 |

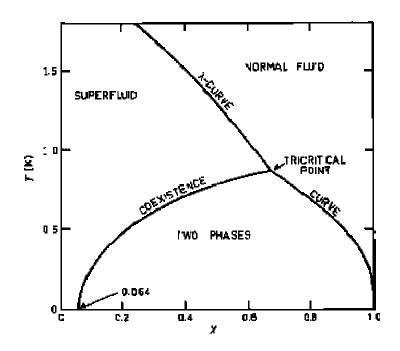

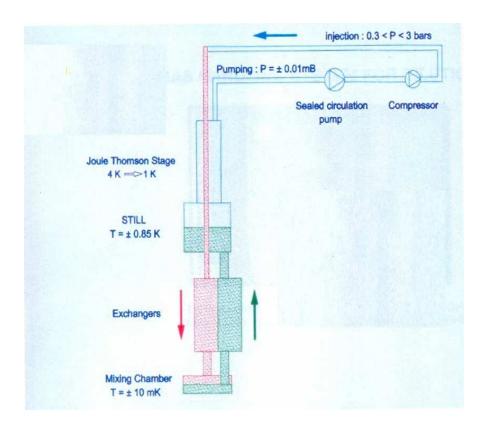

| 4.1 The phase diagram of a liquid helium mixture as a function of the                           |    |

| percentage (x) of <sup>3</sup> He in the mixture. Phase separation takes place when temperature |    |

| is below the tri-critical point ~ 0.86 K                                                        | 75 |

| 4.2 Schematic of a MINDIL-OD70- 30mK dilution refrigerator                                      | 77 |

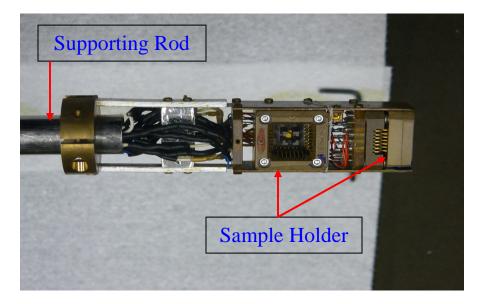

| 4.3 Bottom part of the LHe Insert                                                               | 79 |

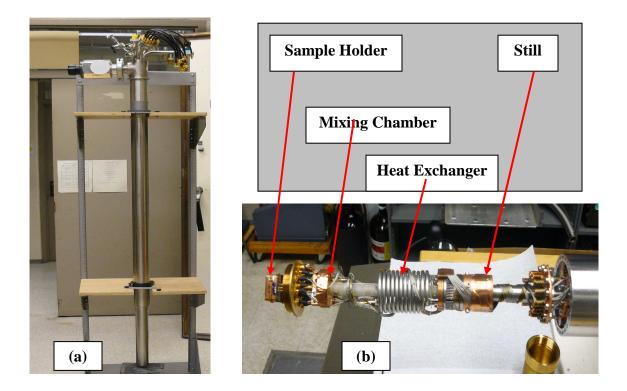

| 4.4 (a) MINDIL-OD70-30mK Insert. (b) Tail of the MINIDIL Insert                                 | 80 |

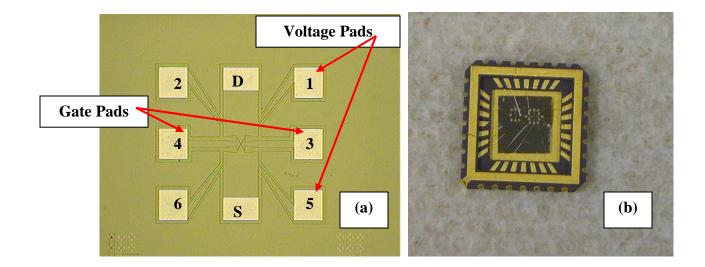

| 4.5 (a) Optical micrograph of a SG QPC device. S/D represents the Source/Drain                  |    |

| pads (b) The QPC device glued and bonded with Chip Carrier                                      | 82 |

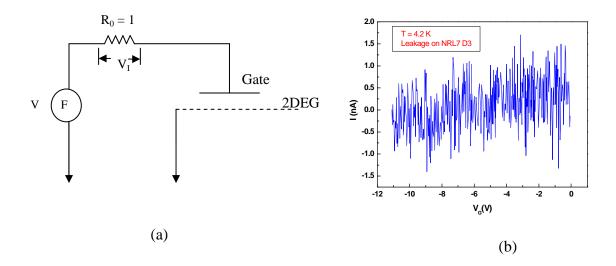

| 4.6 (a) Circuit used for gate leakage current measurement. A function generator, FG,            |    |

| is used as a variable dc source. The 2DEG is connected to the ground via ohmic                  |    |

| contact pads. (b) Leakage current as a function of gate voltage, $V_G$ . The side gates         |    |

| don't leak and completely isolated from the rest of the device                                  | 84 |

| 4.7 (a) Optical micrograph of a SG QPC device. (b) SEM image of the QPC device .               | 85 |

|------------------------------------------------------------------------------------------------|----|

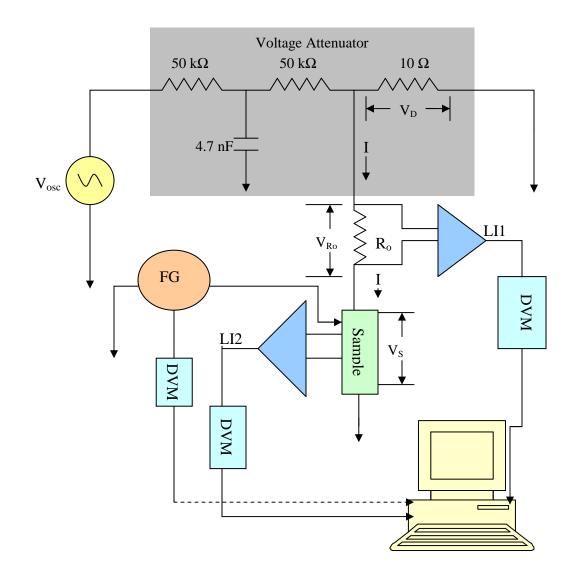

| 4.8 Block diagram of the conductance measurement circuits                                      | 86 |

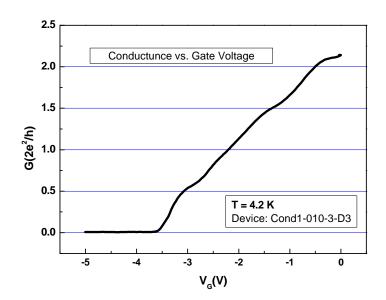

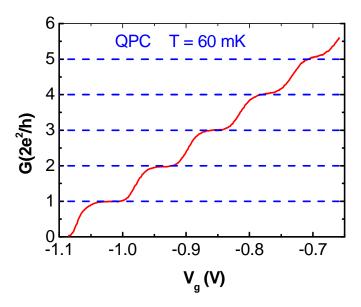

| 4.9 Conductance of the 1D QPC channel as a function of the gate voltage                        | 87 |

| 5.1 Ballistic conductance as a function of gate voltage through a split-gate QPC               |    |

| fabricated on GaAs/AlGaAs heterostructure                                                      | 92 |

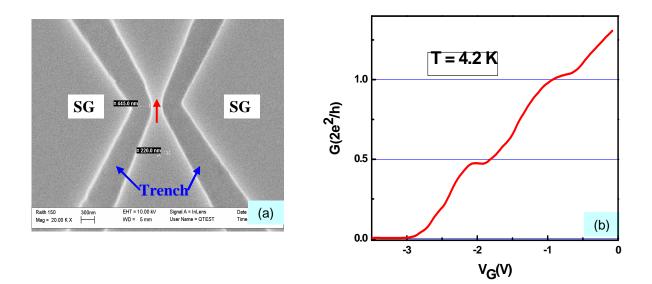

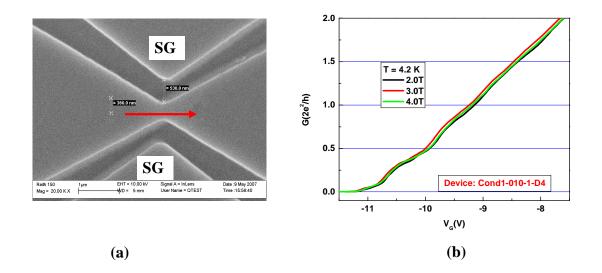

| 5.2 (a) SEM micrograph of a Side Gated QPC. The darker parts, indicated by the blue            |    |

| arrows, are the trench cut by wet etching and the red arrow represent the channel. (b)         |    |

| The 0.5 structure observed on such QPC                                                         | 93 |

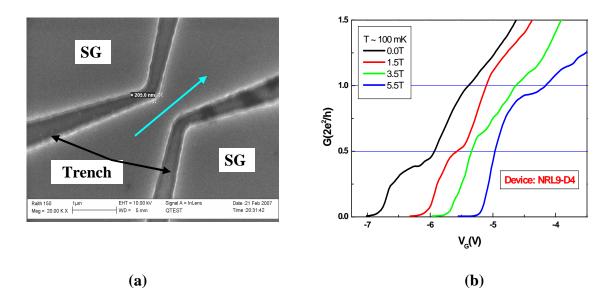

| 5.3 (a) SEM image of the NRL9-D4 device. The blue arrow shows the direction of                 |    |

| the 1D channel. The black arrows show the trenches that define the QPC, (b)                    |    |

| Evolution of 0.5 structure in perpendicular magnetic field. The magnetic field                 |    |

| increases from left to right. The gate voltage axis (x-axis) corresponds to the black          |    |

| curve (zero magnetic field plot). All the plots except the zero magnetic field plot            |    |

| (black curve) have been shifted along the x-axis for clarity                                   | 96 |

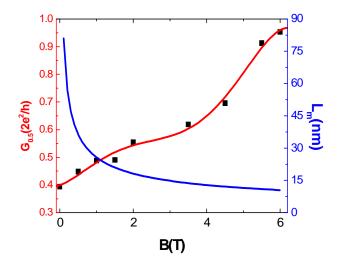

| 5.4 The 0.5 structure moves up in perpendicular magnetic field and approaches to G $\approx$   |    |

| $2e^{2}/h$ . The red line is a guide to the eye. The Blue curve is the plot of magnetic length |    |

| as a function of magnetic field                                                                | 97 |

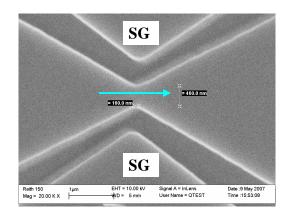

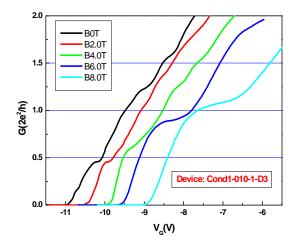

| 5.5 SEM image of the Cond1-010-1-D3 device. The blue arrow shows the direction                 |    |

| of the 1D channel                                                                              | 98 |

| 5.6 The behavior of the 0.5 structure in perpendicular magnetic field is reproduced in         |    |

| Cond1-010-1-D3 QPC device at 4.2 K. The magnetic field increases from left to                  |    |

| right. The x-axis scale corresponds to the black curve. The conductance plots are              |    |

| shifted along the x-axis                                                                       | 99 |

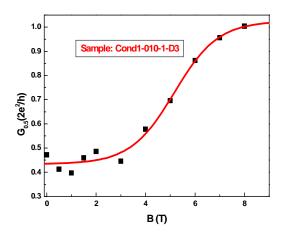

| 5.7 The 0.5 structure moves up in high perpendicular magnetic field. The black            |     |

|-------------------------------------------------------------------------------------------|-----|

| squares are 0.5 structures in different magnetic fields taken from the data shown in      |     |

| Fig. 5.6. The red curve is the guide to the eye                                           | 100 |

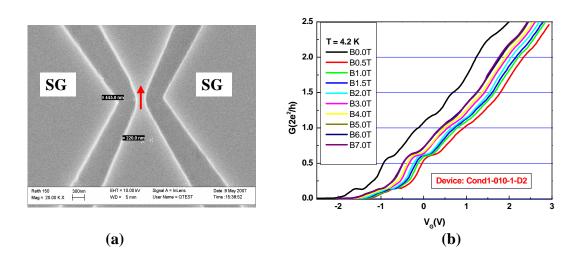

| 5.8 (a) The SEM image of the Cond1-010-1-D2 device. The red arrow shows the               |     |

| direction of the 1D channel. The darker region corresponds to the trenches that define    |     |

| the QPC, (b) the behavior of the 0.5 structure in parallel magnetic field observed in     |     |

| Cond1-010-1-D2 sample at 4.2 K. The field is applied in the current direction. The        |     |

| conductance value of the 0.5 structure remains unchanged in magnetic field 6.13           |     |

| Spin polarization in the lateral confinement                                              | 101 |

| 5.9 (a) The SEM image of the Cond1-010-1-D4 device. The red arrow shows the               |     |

| direction of the 1D channel. The darker region corresponds to the trenches that define    |     |

| the QPC, (b) the behavior of the 0.5 structure in parallel magnetic field observed in     |     |

| Cond1-010-1-D4 sample at 4.2 K. The field is applied in the current direction. The        |     |

| conductance value of the 0.5 structure remains unchanged in in-plane magnetic             |     |

| field                                                                                     | 102 |

| 5.10 The black curve represents the Lateral confinement in the SG QPC. The middle         |     |

| of the strip the potential is flat and rises quickly along the edges. The red curve shows |     |

| the magnetic confinement created when the perpendicular magnetic field is applied to      |     |

| the QPC                                                                                   | 103 |

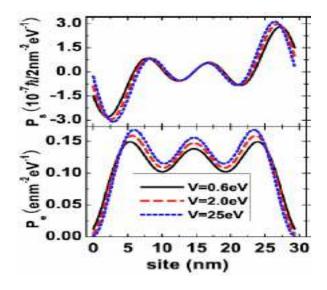

| 5.11 Spin polarization in the lateral confinement [4]. Spin accumulation is plotted       |     |

| with respect to the lateral axis (site) in the top part of the figure. It shows that      |     |

| opposite spin accumulates along the two opposite edges. The bottom part shows the         |     |

| charge accumulation with respect to the lateral coordinate                                | 104 |

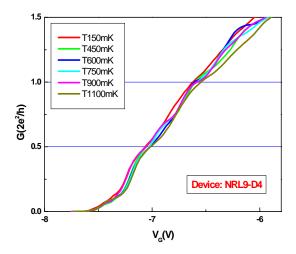

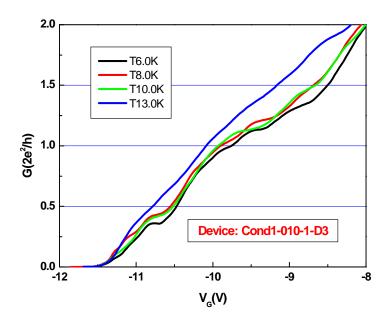

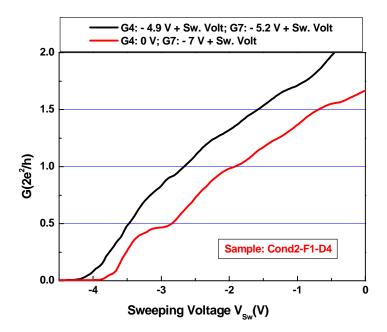

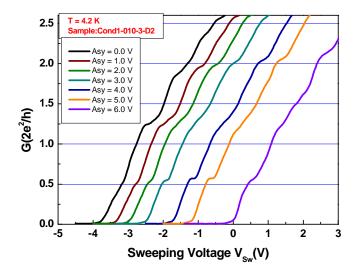

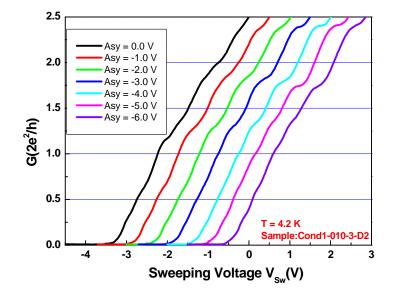

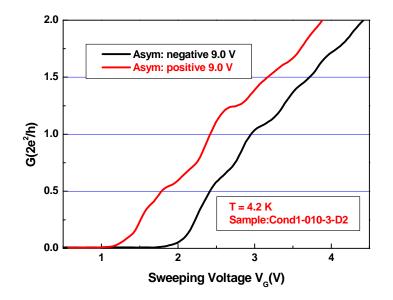

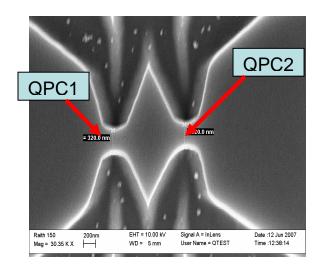

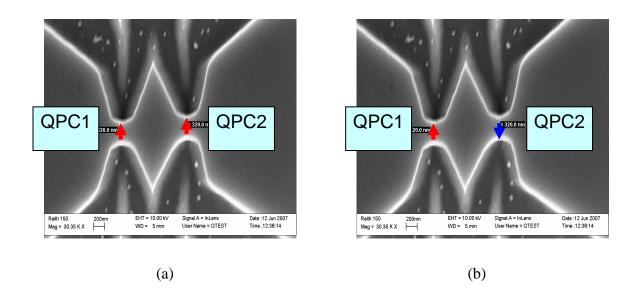

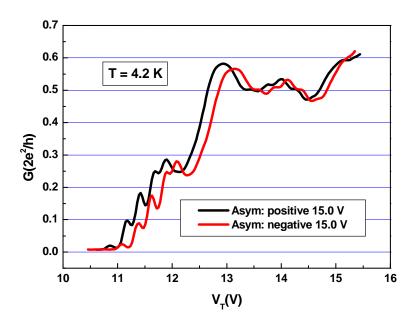

5.12 The conductance plots at different fixed temperature on NRL9-D4 device. The measurements are taken in the temperature range from 150 mK to 1100 mK. The x-axis corresponds to the red curve at 150 mK which deplete at -7.59 V. All the other plots are shifted to the same pinch-off voltage6.19 The conductance quantization as a function of gate voltage at different negative gate asymmetry...... 107 5.13 The 0.5 structure at different higher temperature. Thermal smearing is observed at T  $\sim$  13 K. The x-axis corresponds to the black curve at 6K which deplete at -11.5 V. All the other plots are shifted to have the same pinch-off voltage ..... 108 5.14 Conductance a function of sweeping voltage measured in Cond-2-F1-D4 device. The black trace represents the symmetric gate voltage condition where almost the same voltage is applied to both the gates. The red curve is the conductance when -7.0 applied to gate 7 but 0 V is applied to gate 4 ..... 111 5.15 Conductance plot measured in Cond-1-010-3-D2 device as a function of sweeping gate voltage at various positive gate asymmetries ..... 112 5.16 Conductance as a function of sweeping gate voltage in Cond-1-010-3-D2 device at various negative gate asymmetries. The 0.5 structure is absent in the negative asymmetry range from 0V to 6.0 V ..... 113 5.17 Conductance plot measured in Cond-1-010-3-D2 device as a function of sweeping gate voltage at both positive 9.0 V asymmetry and negative 9.0 V asymmetry. The 0.5 structure is present in both asymmetries ..... 114 5.18 SEM image of a Dual-QPC device fabricated on Cond1 InAs/InGaAs QW structures ..... 117

5.19 Working principle of the dual-QPC device: (a) If QPC1 and QPC2 allow the

| same  | kind    | of    | spins;  | we    | expect    | full | transmission,    | (b)   | If | QPC1 | and | QPC2 | allow |     |

|-------|---------|-------|---------|-------|-----------|------|------------------|-------|----|------|-----|------|-------|-----|

| oppos | ite spi | in tl | here wi | ll be | e no tran | smis | sion in the idea | al ca | se |      |     |      |       | 118 |

| 5.20 Characterization of the QPC2 keeping the channel of the QPC1 open. QPC2 has          |     |

|-------------------------------------------------------------------------------------------|-----|

| two gates: Gate A and Gate B. Conductance of the QPC2 is plotted as a function of         |     |

| the Gate-B voltage                                                                        | 119 |

| 5.21 QPC2 is fixed at ~0.5 ( $2e^2/h$ ) while output conductance is plotted as a function |     |

| of the gate voltage in the QPC1. The black trace corresponds to the conductance at        |     |

| positive 15.0 V asymmetry and the red trace corresponds to the conductance at             |     |

| negative 15.0 V asymmetry                                                                 | 120 |

| 6.1 Schematic of injector and detector QPCs and the trajectories of electrons with        |     |

| two spin states                                                                           | 130 |

## **List of Tables**

| Table 3.1 Carrier concentration, <i>n</i> , mobility, $\mu$ and the mean free path, <i>l</i> of |    |

|-------------------------------------------------------------------------------------------------|----|

| different wafers used in this research work                                                     | 51 |

| Table 3.2 PMMA used in different fabrication process                                            | 56 |

| Table 3.3. Recipe for Metal Deposition                                                          | 62 |

| Table 3.4. Etching recipe for InAs/InGaAs wafer shown in Fig. 3.5                               | 64 |

| Table 4.1. Contact resistance of ohmic pad pairs of the SG QPC device of Fig.                   |    |

| 5.5(a) at 300 K and 4.2 K                                                                       | 83 |

Chapter 1

# Overview

The field of *spintronics* is based on the manipulation of the spin and charge degrees of freedom simultaneously. The field of metallic spintronics has already proven enormously successful, and delivered functional devices such as GMR read heads in hard disks and MRAM of insulator spintronics. Despite the enormous success of metal-based spintronics, the emerging field of *semiconductor spintronics*, compatible with conventional microelectronics, is recognized as the next leap on information technology. It holds promise for the development of all-semiconductor MRAMs, very fast and low-power spin FETs, and spin-based quantum computation [1, 2]. The basic Physics research is currently focused on the fundamental problems in semiconductor spintronics, such as: all-electrical spin control via spin-orbit interactions, transporting spins between different locations within conventional semiconductor environments, coherent manipulation of electron spin at a given location, diluted magnetic semiconductors, and fixed or mobile spin qubits for quantum computing [1, 2, 12].

The controlled creation, detection, and manipulation of spin-polarized currents by *purely electrical means* are the challenges facing semiconductor spintronics [1]. In this context, the spin-orbit coupling (SOC) is envisioned as a possible tool for *all-electrical* spin control in semiconductor devices without ferromagnetic elements or external magnetic fields. SOC in the III-V semiconductor lifts the spin degeneracy and may have different physical origins. The Rashba SOC (RSOC) [3] arises from the asymmetry in the confining potential of a two-dimensional (2D) electron or hole gas. The Lateral SOC (LSOC) [4, 5] arises from an in-plane electric field resulting from the lateral confining potential of a quantum wire. The SOC can polarize the electrons in the semiconductor. The *RSOC* and the *LSOC* can be considered as two ideal tools to achieve this objective

since both can be varied *in situ* by an external gate voltage. In this research work, one of the objectives is to study the influence of the SOC on electron transport in 1D quantum point contact (QPC) made from semiconductor structures with large SOC.

Numbers of theoretical studies have proposed ways to produce spin polarization in semiconductor channels using LSOC. It has been reported in Refs [4] and [5] that due to LSOC opposite spins accumulate along the edges of the lateral confinement. Still there is no experimental evidence of LSOC in a 1D system. Can this spin polarization due to LSOC cause an anomalous conductance plateau in a 1D quantum? We aim to study the spontaneous spin polarization in QPC due to LSOC.

In a ballistic 1D system (e.g. QPC) conduction is quantized in integral multiple of  $2e^2/h$ , where the factor 2 is coming from the spin degeneracy of the electrons. A few years after the discovery of the conductance quantization, an additional plateau was observed at G  $\cong$  0.7 (2e<sup>2</sup>/h) in the absence of any magnetic field in a AlGaAs/GaAs QPC [4]. Since then, this anomalous plateau has been observed in many experiments, both in GaAs electron and hole 1D systems [4,6,13-16], and commonly referred as the ' 0.7 *structure*'. Based on the characteristics of this 0.7 structure (such as, evolution of 0.7 structure in temperature, in parallel magnetic field, formation of the zero bias anomaly), there have been many theoretical attempts to understand its origin. The most intriguing of them are the spin polarization models [6-8] in which static spin polarization of the electrons has been predicted that gives a plateau in the range (0.7-0.5) (2e<sup>2</sup>/h). But, this anomaly is not a universal feature since it is not observed in all devices. Its existence is found to depend on gate voltage adjustments and hence on the details of the lateral confining potential [9, 10]. The intrinsic SOC in the GaAs electron system is very small.

And, therefore, the 0.7 structure observed in the quantum wires or QPCs, fabricated on the GaAs electron systems, cannot be explained in terms of the LSOC.

The SOC in an InAs quantum well (QW) is very large [11]. The side gated (SG) QPC devices fabricated on InAs QW structures offer a strong lateral confinement. Thus, the LSOC in the SG QPC is expected to be enhanced. Moreover, the profile of the confining potential in the SG QPC can be tuned by applying bias voltages to the gates. This gives an opportunity to manipulate the spin polarization in the QPC. Can then the QPC devices, fabricated on InAs QW structure, be used as a spin polarizer by totally electrical means?

We have observed an anomalous conductance plateau observed at  $G \cong 0.5$  ( $2e^2/h$ ) (we will latter call it as '0.5 structure') on SG QPC devices fabricated on InAs/InGaAs QW structures. The origin of the 0.5 structure is the spontaneous spin polarization due to LSOC. The potential profile of the lateral confinement can be manipulated by applying asymmetric gate voltage to the side gates of the SG QPC device. The anomalous 0.5 structure can be made to appear or disappear by adjusting the bias voltages of the gates that create the potential confinement of the SG QPCs. *This is the first experimental observation of the LSOC in semiconductor heterostructures*.

This dissertation is organized as follows: In Chapter 2, we will discuss on the current theoretical and experimental status of the SOCs and anomalous conductance quantization due to spontaneous spin polarization. Chapter 3 will focus on the growth of InAs QW structures and their characterization. In this chapter we will also highlight the different fabrication steps of 1D nano-scale devices. The experimental and measurement techniques will be discussed in the Chapter 4. In Chapter 5, we will underline the

experimental results. We will discuss the experimentally observed 0.5 structure, its behavior in both perpendicular and parallel magnetic fields and the temperature dependence of this anomalous structure. We will discuss how asymmetry in the confining potential affects the 0.5 structure. The new device that is proposed to detect the spin polarization by transport measurements will also be discussed in this chapter. Finally, we will summarize our results and give a brief comparison between our 0.5 structure and the anomalous plateau observed by other groups. In Chapter 6, we will give a brief outlook of future work.

#### References

- 1. Semiconductor Spintronics and Quantum Computation, edited by D. D. Awschalom, D. Loss, and N. S (Springer, Berlin, 2002).

- 2. I. Zutic, J. Fabian, and S. Das Sarma, *Spintronics: Fundamentals and Applications*, Rev. Mod. Phys. **76**, 323 (2004).

- **3.** Yu. A. Bychkov and E. I. Rashba, *Oscillatory effects and the magnetic susceptibility of carriers in inversion layers*, J. Phys. C **17**, 6039 (1984).

- **4.** Yongin Jiang and Liangbin Hu, *Kinetic magnetoelectric effect in a twodimensional semiconductor strip due to boundary-confinement-induced spin-orbit coupling*, Phys. Rev. B **74**, 075302 (2006).

- **5.** Yanxia Xing, Qing-feng Sun, Liang Tang and Jiang Ping Hu, Accumulation of opposite spins on the transverse edges of a two dimensional electron gas in a longitudinal electric field, Phys. Rev. B **74**, 155313 (2006).

- **6.** D. J. Reilly, *Phenomenological model for the 0.7 conductance feature in quantum wires*, Phys. Rev. B **72**, 033309 (2005).

- Anton A. Starikov, Irina I. Yakimenko, and Karl-Fredrik Berggren, *Scenario for the 0.7-conductance anomaly in quantum point contacts*, Phys. Rev. B 67, 235319 (2003).

- 8. P. Havu, M. J. Puska, R. M. Nieminen and V. Havu, *Electron transport through quantum wires and point contacts*, Phys. Rev. B 70, 233308 (2004).

- R. Crook, J. Prance, K. J. Thomas, S. J. Chorley, I. Farrer, D. A. Ritchie, M. Pepper, C. G. Smith, *Conductance Quantization at a Half-Integer Plateau in a Symmetric GaAs Quantum Wire*, Science 312 (2006).

- 10. Yunchul Chung, Sanghyun Jo, Dong-In Chang, Hu-Jong Lee, M. Zaffalon, V. Umansky, and M. Heiblum, *Tunable 0.7 conductance plateau in quantum dots*, Phys. Rev. B 76, 035316 (2007).

- E. A. de Andrada e Silva, G. C. La Rocca, and E. Bassani, *Spin-orbit splitting of electronic states in semiconductor asymmetric quantum wells*, Phys. Rev. B 55, 16293 (1996).

- 12. Sankar D. Sharma, Spintronics- A new class of device based on the quantum of electron spin, rather than on charge, may yield the next generation of microelectronics, American Scientist, 89, 516 (2001).

- 13. R. Danneau, O. Klochan, W. R. Clarke, L. H. Ho, A. P. Micolich, M. Y. Simmons, A. R. Hamilton, M. Pepper, D. A. Ritchie, and U. Zülicke, *Zeeman Splitting in Ballistic Hole Quantum Wires*, Phys. Rev. Lett. 97, 026403 (2006).

- 14. L. P. Rokhinson, L. N. Pfeiffer, and K. W. West, *Spontaneous Spin Polarization in Quantum Point Contacts*, Phys. Rev. Lett. 96, 156602(2006).

- 15. R. Danneau, W. R. Clarke, O. Klochan, A. P. Micolich, A. R. Hamilton, M. Y. Simmons, M. Pepper and D. A. Ritchie, *Conductance quantization and the 0.7×2e<sup>2</sup>/h conductance anomaly in one-dimensional hole systems*, Appl. Phys. Lett. 88, 012107 (2006).

- 16. A. Kristensen, H. Bruus, A. E. Hansen, J. B. Jensen, P. E. Lindelof, C. J. Marckmann, J. Nyga<sup>o</sup>rd, and C. B. Sørensen, *Bias and temperature dependence of the 0.7 conductance anomaly in quantum point contacts*, Phys. Rev. B 62, No. 16 (2000).

# Chapter 2

# **State-of-the-Art**

#### **2.1 Introduction**

Spin electronics or *spintronics* is based on the simultaneous manipulation of the spin and charge degrees of freedom in a multitude of systems and aims to develop electronic devices based on the control of the electron spin. It holds promise for the development of all-semiconductor MRAMs, very fast and low-power spin FETs, and spin-based quantum computation [1, 2].

In III-V semiconductors, spin-orbit coupling (SOC) lifts the spin degeneracy of the conduction band electrons without any external magnetic field. Since, spin transport is strongly affected by coupling of the spin and orbital degrees of freedom, the spin-orbit coupling (SOC) is visualized as a possible tool for *all-electrical* spin control in semiconductor devices without ferromagnetic elements or external magnetic fields. SOC may have different physical origins and can play a vital role in spintronics to realize active spin devices like Spin-filters, Spin-FET etc. In this context, the *Rashba spin-orbit coupling* (RSOC) [3] and recently proposed *lateral spin orbit coupling* (LSOC) [4, 5] offer an interesting possibility since both of these SOCs can be varied by an external electric field in semiconductor heterostructures and quantum wells.

SOC may cause the spontaneous spin polarization in a 1D system such as quantum point contact (QPC). A deeper understanding of different SOCs and spontaneous spin polarization may help to generate future usable devices based on spin transport. In this chapter, we will discuss the current theoretical and experimental status of different kind of SOCs. The current status of the spontaneous spin polarization and the anomalous conductance quantization observed in a 1D quantum point contact (QPC) will also be discussed.

#### **2.2 Spin Orbit Coupling**

Spin orbit coupling (SOC) is a relativistic effect which may arise in a semiconductor and cause spontaneous spin polarization. The SOC may have different physical origins. In the subsequent section SOC and different types of SOCs will be discussed.

#### I. What is SOC?

SOC is a relativistic effect which can be derived from the Dirac equation [6] and expressed as

$$H_{SO} = \lambda \hat{\sigma} \cdot \left( \vec{k} \times \vec{\nabla} V \right), \tag{2.1}$$

where  $\lambda = -\frac{\hbar^2}{4m_o^2 c^2} \approx -3.7 \times 10^{-6} \dot{A}^2$ ,  $m_o$  is the vacuum electron mass,  $k = p/\hbar$ , c is the

speed of the light and  $\sigma$  are the Pauli spin matrices . The potential, *V*, in the semiconductor may arise due to impurities, asymmetry in the confinement well, boundaries and also by external means. In Dirac equation, the positive and negative energy are separated by an energy gap of  $2m_oc^2 \approx 1$  Mev and is known as Dirac gap. For a slow electron (v/c <<1) and a weak electric field (in Eq. (2.1) the field arises due to the voltage gradient), the SOC is very small because of the large Dirac gap. In semiconductor materials and structures with the approximation of a two band model the equations of the band theory are similar to Dirac equation and the Dirac energy gap is replaced by the energy gap between conduction and valence band which is only 1 eV or less in many III-IV semiconductors [7-9]. The SOC in narrow band gap semiconductor thus enhance a lot and thus make the SOC very prominent in semiconductor.

The voltage gradient in Eq. (2.1) gives rise to an electric field which appears as:

$$\vec{E} = \left(\frac{1}{e}\right)\vec{\nabla}V.$$

(2.2)

The electrons, in their reference frame, feel that electric field as an effective magnetic field,

$$\vec{B}_{eff} = 1/c \left( \vec{v} \times \vec{E} \right), \tag{2.3}$$

which causes the spin orbit coupling. Thus, spin degeneracy of the conduction band electrons of a III-V semiconductor can be lifted without any external magnetic field due to SOC. The static electric field that causes the SOC results from different physical origins such as inversion asymmetry of the microscopic crystal potential in the bulk zincblende semiconductor and is known as bulk inversion asymmetry (BIA). The second is the inversion asymmetry of the macroscopic potential that confines the 2DEG and is known as the structure inversion asymmetry (SIA). The voltage gradient along the edges of the lateral confinement also causes a spin orbit coupling which is known as lateral spin orbit coupling (LSOC).

#### **II. Dresselhaus Spin Orbit Coupling**

Bulk inversion asymmetry (BIA) causes a spin orbit coupling which refers to the lack of an inversion center in the III-V zinc-blende semiconductor structures. The inversion symmetry in space and time, change the wave vector  $\mathbf{k}$  into  $-\mathbf{k}$ . In addition, the time inversion also flips the spin. Combining these two symmetry operations one get a twofold degeneracy of the single particle energies as  $E(\mathbf{k},\uparrow) = E(\mathbf{k},\downarrow)$  and is common in group-IV elements such as diamond, Si, Ge. But the III-V zinc blende structure does not

maintain the inversion symmetry and  $E(\mathbf{k},\uparrow) \neq E(\mathbf{k},\downarrow)$ . Thus, BIA lifts the spin degeneracy for a given direction of the wave vector  $\mathbf{k}$ . Dresselhaus first pointed out BIA [10] and the SOC that arises due this BIA is know as Dresselhaus SOC. For a quasi-two dimensional case in a sufficiently narrow quantum well (QW) grown in [001] direction, the Dresselhaus SOC term can be written as [11, 12]

$$H_D = \beta (k_x \sigma_x - k_y \sigma_y), \qquad (2.4)$$

where  $\beta$  is the characteristic parameter that is proportional to  $1/d^2$  with *d* being the width of the QW. For d = 100 Å, it is found that  $\beta$  ranges from  $2 \times 10^{-10}$  to  $2 \times 10^{-9}$  eV cm [8]. The Dresselhaus SOC is experimentally observed in bulk InSb by analyzing the Shubnikov-de Haas (SdH) effect [13] and by an optical method on the GaAs (110) surface [14]. Since the Dresselhaus effect depends strongly on the crystallographic direction, it is possible to find the direction in which this effect is minimum [15]. These optimal directions are, respectively, [1 2 0] and [1 0 0] for GaAs and InAs channels realized from the 2DEGs in quantum wells with [0 0 1] as the growth direction.

#### **III. Rashba Spin Orbit Coupling**

The structural inversion asymmetry (SIA) in the confining potential well of a 2D electron system gives rise to an interface electric field *E* perpendicular to the plane of the well. This inversion asymmetry field causes an enhanced spin-orbit coupling, known as Rashba spin orbit coupling (RSOC). The Hamiltonian that describes the RSOC is given as [3]

$$H_{R} = \alpha \left( \vec{\sigma} \times \vec{k} \right) \hat{z} , \qquad (2.5)$$

where  $\sigma$  are the Pauli matrices, k is the quasi 2D momentum vector and  $\alpha$  is the Rashba parameter that defines the strength of the SOC.

The RSOC causes the spin splitting without any external magnetic field and is finite for a nonzero k. Due to the relativistic effect, the moving electrons feel the interface electric field E as an effective magnetic field ( $B_R = \alpha k / \mu_B$ ). This pseudo magnetic field, known as Rashba magnetic field, lies in the plane of the 2DEG and is perpendicular to the electric field, *E*, and the wave vector, *k*. The spins of the electron moving with the wave vector *k* precess around the direction,  $B_R$ .

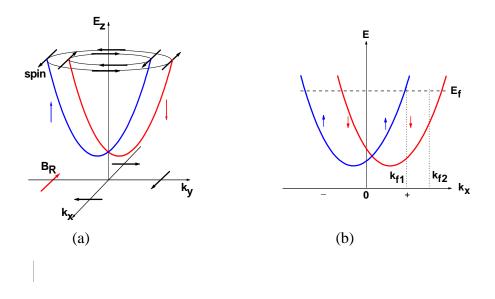

**Fig. 2.1.** Energy dispersion of Rashba spin-split subbands: (a) 2D case: black arrows represent spin eigen states. (b) 1D case: spin-up and spin-down electrons travel with different Fermi velocities.

Due to RSOC the electron density of states split into spin up and spin down subbands with the energy dispersion relation (Fig. 2.1) given by

$$E(k) = \frac{\hbar^2}{2m^*} k^2 \pm \alpha k , \qquad (2.6)$$

where *k* magnitude of the momentum wave vector and  $m^*$  is the electron effective mass. The Rashba parameter  $\alpha$  is defined as,

$$\alpha = \alpha^* |e|E, \qquad (2.7)$$

with  $\alpha^*$  being the SOC parameter. The magnitude of  $\alpha$  depends on the confining potential and can also be controlled by external means (by applying gate voltage).

So, the spin degeneracy of a 2DEG is lifted for  $k \neq 0$  without any external magnetic field. The spin splitting energy is given by  $\Delta_R = 2\alpha k_F$  at  $k \neq 0$ , where  $k_F$  (=  $(2\pi n))^{1/2}$  is the average Fermi wave vector and can be determined from the 2DEG carrier concentration, *n*. The Fermi surface of a 2DEG in the presence of Rashba spin splitting consists of concentric circles with radii  $k_{FI}$  and  $k_{F2}$  (Fig. 2.1 (a)), the Fermi wave vectors of the two spin split energy bands. In 1D, electrons are spin polarized and travel with different velocities in the same direction as shown in Fig. 2.1 (b). These two Fermi wave vectors correspond to two electron gases with slightly different carrier concentration  $n_{\pm}$  and can be observed from the beating pattern in the Shubnikov-de Haas oscillations (SdH) [16, 17]. The nodes in the beating pattern occur at the half integer values of  $\Delta_R / \hbar \omega_c$  [18], where  $\omega_c = eB/m^*$  is the cyclotron frequency. The node index, N, is derived as a function of 1/B as [17],

$$N = \frac{m^* \Delta_R}{e\hbar} \left(\frac{1}{B}\right) + \left(\frac{g^* m^*}{2m_0} + \frac{1}{2}\right),$$

(2.8)

where  $g^*$  is the effective electronic g factor and  $\mu_B$  is the Bohr magneton. By plotting N against 1/B, spin orbit splitting energy  $\Delta_R$  and  $g^*$  can be found. Then knowing the Fermi

energy  $k_F$  from the total concentration in the SdH measurement, the Rashba parameter  $\alpha$  can be determined. Typical values of  $\alpha$  ranged from 10<sup>-9</sup> eV-cm to  $6 \times 10^{-9}$  eV-cm for InAs based QWs [7, 19].

The Rashba spin-orbit coupling and its manipulation by an external electric field in 2DEGs at an asymmetric heterojunction or in an asymmetric quantum well have been well established from experimental studies of the beating pattern in SdH oscillations [17, 20, 21]. Very recently, the evidence of the Rashba spin precession has been reported in strained bulk GaAs and InGaAs using ultrafast optical techniques [22]. However, *so far there has been no unambiguous experimental observation of the Rashba spin precession tuned by electrical means*, the corner stone of the concept of the Datta-Das spin FET [23]. Attempts have been made to observe the Rashba spin precession with inconclusive results in electron channels of widths large enough so that the channels are 2D [24, 25]. The 1D channel offers a unidirectional propagation wave vector  $\mathbf{k}$ , and therefore the *spin quantization axis* defined by the Rashba magnetic field  $B_R$  is well defined [61]. This is not the case in a 2D system since the Fermi surface is a circle. Despite several advantages, 1D or 1D ballistic systems have not been used so far for studying the Rashba spin precession.

#### **IV. Lateral Spin orbit Coupling**

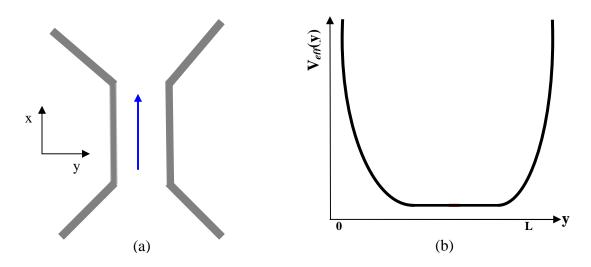

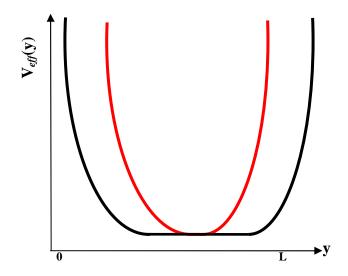

The other kind of SOC, which has been proposed in 2006[4, 5, 26], arises due to the lateral confining potential known as lateral spin orbit coupling (LSOC). Consider a quantum wire with a current flowing in the x direction, y is the lateral direction and 2DEG is lying in the x-y plane (Fig 2.2(a)). The confining potential, V(y), is defined in

the y-direction where it is constant at the center of the quantum wire and rises up along the edges (Fig 2.2(b)). The electrons confined by such a non-uniform lateral potential well are moving with relativistic speed and the spin and orbital degrees of freedom of the electron are coupled together [6].

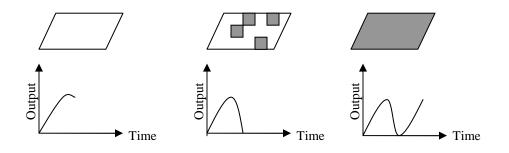

**Fig. 2.2.** (a) Schematic of the 1D Quantum Wire . The blue arrow shows the channel direction, (b) Lateral confinement in 1D.

The SOC due to lateral confinement (LSOC) has the form [6, 27],

$$H_{so} = -\frac{\hbar^2}{4m_{\varrho}^2 c^2} \hat{\sigma} \cdot \left[ \vec{k} \times \vec{\nabla} V(y) \right],$$

(2.9)

where  $\hat{\sigma}$  are the Pauli matrices,  $\vec{k}$  is the wave vectors, and V(y) is the lateral (transverse) confining potential. The voltage gradient along the edges gives rise to an electric field perpendicular to the edge [see Eq. (2.2)]. Due to the relativistic effect, that electric field causes a SOC along the edges with SOC energy [5],

$$V_{so} = -\frac{\hbar^2}{2m^{*2}c^2} \sigma_z k_x \partial V(y) / \partial y, \qquad (2.10)$$

It is clearly seen from Eq. (2.10) that, the effective potential for spin up ( $\sigma_z = +1$ ) and spin down electrons ( $\sigma_z = -1$ ) have different values along the two edges (y = 0 and y = L). When the electrons are moving in the positive  $k_x$  direction at y = 0, the effective potential is lower for spin-down electrons ( $\sigma_z = -1$ ) than for spin-up electrons ( $\sigma_z = 1$ ) (Fig. 2.3(a)). But at y = L the effective potential of spin-up electrons is lower than spindown electrons for positive  $k_x$  (Fig. 2.3(a)). Thus, opposite spins are accumulates along

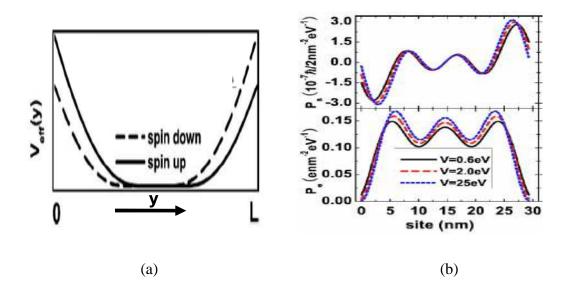

**Fig. 2.3.** (a) Spin-up and spin-down electrons have different effective potential along the two edges, (b) different spin accumulates along the two edges [5].

the two different edges with electrons moving in  $k_x$  direction under longitudinal bias voltage (Fig. 2.3(b)). The sign of spin accumulation is reversed when the electrons are moving with  $-k_x$ . So, LSOC can cause the spin polarization along the edges. The numerical results in Refs. 4 and 5 suggested that spin accumulation can occur in both

square and parabolic confining potential and the spin accumulation density  $P_s(y)$  is zero for V = 0 and  $P_s(y)$  increases as V increases.

The bottom part of Fig. 2.3 (b) shows the charge density  $P_e(y)$  as a function of lateral direction, y. The top part of Fig. 2.3 (b) is the spin accumulation density  $P_s(y)$ which indicates the two opposite spin accumulates along the two opposite transverse edges. It is shown that the spin accumulation in the middle of the channel is small and oscillates which is due to the quantum interference between the spin-up and spin-down components of the electron wave functions. It is also reported that in the presence of random impurity the oscillations of the spin density in the middle of the strip are suppressed strongly [4, 5]. This is because the random impurity scattering destroy the quantum interference of the spin-up and spin-down electron wave functions in the middle of the strip

A number of theoretical studies have proposed ways to produce spin polarization in semiconductor channels using the SOC. The most intriguing among them is the spin Hall effect (SHE) which states that a transverse spin current is created when a charge current is flowing in the longitudinal direction and different types of spins accumulates along the lateral edges of sample due to the transverse spin current [28-31]. This phenomenon is very attractive in semiconductor spintronics as it predicts an effective way of producing spin currents or spin polarization in a semiconductor without using magnetic material or external magnetic field. Two types of SHE are predicted in theory. One of them is *intrinsic* SHE that arises due to intrinsic SOC and occurs even in the absence of any impurity [28, 29]. The other one is *extrinsic* SHE that arises due to extrinsic SOC coming from impurity scattering [31, 32]. The intrinsic SHE discovery has generated a tremendous amount of interest in the research community and there has been a flurry of theoretical work in the area. The subject remains highly controversial. The extrinsic SHE was experimentally observed by Kato *et. al.* in n-doped bulk GaAs [33]. Another work claimed to have experimentally observed intrinsic SHE by measuring the circular polarization of light emitted by p-n junction LED [34]. But the direct observation of SHE is still missing.

The LSOC implies that, under longitudinal bias voltage, different spins accumulate along the two opposite edges of the sample strip. This is very similar to SHE but the spin polarization occurs due to a different mechanism. The experimental result of SHE [33, 34] can be explained using this new theory. In Ref [5], LSOC has predicted the spin density distribution  $P_s \approx 0.3 \times 10^{-6}$  nm<sup>-2</sup> eV<sup>-1</sup> and the spin polarization as  $0.8 \times 10^{-4}$ , which are in good agreement with the experimental results obtained from Ref [33]. In a recent paper Hattori and Okamoto [26] proposed that in cross wires transverse spin separation and spin Hall effect can be observed due to LSOC in the ballistic limit. Still there are no experimental results regarding the LSOC.

# 2.3 Anomalous Conductance Plateau and Spontaneous Spin Polarization in GaAs QPCs

In a 1D ballistic quantum point contact (QPC) the conductance is quantized in unit of  $2e^2/h$  as:

$$G = n(2e^2 / h). (2.11)$$

Here *n* is the number of occupied energy subbands with the subband energy bottom lower than the Fermi energy  $E_F$  and each subband is doubly degenerate [35, 36]. The Fermi

energy can be swept up or down by changing the gate voltage in the QPC. So, as a function of Fermi energy or gate voltage a staircase conductance behavior is observed in

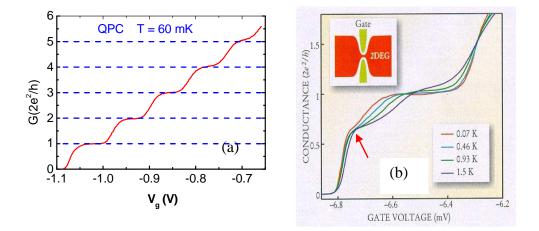

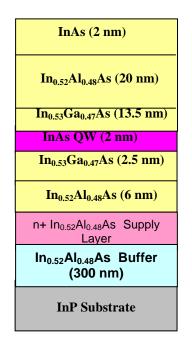

Fig. 2.4. (a) Conductance quantization observed in a QPC fabricated on GaAs/AlGaAs Heterostructure in zero magnetic field [50]. (b) The 0.7 Structure observed in a QPC of length 400 nm fabricated on GaAs/AlGaAs hole system in B = 0 [37]. The arrow points to the location of the anomalous plateau.

1D QPC. Figure 2.4(a) shows the conductance quantization in the absence of magnetic field observed in a quantum point contact (QPC) of length 100 nm made on AlGaAs/GaAs heterostructure [50]. After the discovery of the normal conductance quantization in QPC, an additional conductance plateau is observed at  $G \cong 0.7$  ( $2e^2/h$ ) in 1D systems in many experiments in the absence of magnetic field [37-45]. This anomalous plateau is in general referred as 0.7 structure (Fig 2.4(b)).

This anomalous conductance plateau ('0.7 structure') was first reported in 1996 in a QPC that is realized on GaAs/AlGaAs 2DEG [37]. It is then observed in many GaAs/AlGaAs based short (QPC) and long quantum wires with different geometry and size [38-45]. This 0.7 structure recently appeared in a QPC made on a two dimensional hole gas (2DHG) [46-48]. It is also found in 1D carbon nanotube [49].

**Fig. 2.5.** (a) The temperature dependence of the 0.7 *Structure* in an AlGaAs/GaAs QPC of length 500 nm [51]. (b) Evolution of the 0.7 *Structure* into a  $0.5(2e^2/h)$  plateau in parallel magnetic field 0-13T [37]. The arrow indicates the evolution.

To pin down the origin of this 0.7 structure, the evolution of this anomalous plateau in temperature and magnetic field has been thoroughly studied. The evolution of this 0.7 structure with source-drain bias voltage has also been studied. The behavior of the 0.7 structure at different temperatures, observed in different experiments using various quantum wires of different of lengths and sizes, is qualitatively the same. The evolution of this anomaly with temperature is shown in Fig. 2.4 (b) and Fig. 2.5 (a) in a temperature ranged from 70 mK to 4.1 K. The 0.7 anomaly is weak at low temperatures but fully developed at higher temperature, while the normal quantization plateaus disappear as the temperature is raised. *This clearly indicates that the 0.7 structure is not*

*associated with ballistic transport.* The 0.7 structure shows a strong dependence on the in-plane magnetic field. Figure 2.5 (b) shows the evolution of the 0.7 structure as the in-plane magnetic field is increased. As the parallel magnetic field is increased gradually, the 0.7 structure decreases smoothly to the fully polarized state (Zeeman spin-split state) at 0.5  $(2e^2/h)$  [37, 39-41]. Similar behavior of the 0.7 structure in a parallel magnetic field is also reported in the QPC devices created from 2DHG [46, 47].

**Fig. 2.6.** Differential conductance g as a function of source-drain bias voltage observed in hole QPCs made on p-type AlGaAs/GaAs heterostructure: (a) at temperatures 25-930 mK in zero magnetic field. (b) at 25 mK in parallel magnetic fields 0 - 4 T [47].

An interesting feature of the 0.7 *Structure* is the behavior of its non-linear differential conductance g = dI/dV, where V is the source-drain bias voltage. As shown in Fig. 2.6, a distinct peak is observed around zero source-drain bias voltage at low temperature. The zero bias anomaly (ZBA) decreases as the temperature is increased or related to the disappearance of the 0.7 *Structure* as the temperature is lowered (Figs. 2.4(b) and 2.5 (a)).

In some experimental work, a conductance plateau is observed at G = 0.5 (2e<sup>2</sup>/h) in zero magnetic field [39, 44] on quantum wires fabricated from GaAs/AlGaAs heterostructures with different geometries. The 0.5 (2e<sup>2</sup>/h) plateau was observed in zero magnetic field along with the 0.7 structure in GaAs quantum wires created on AlGaAs/GaAs heterostructures using erasable electrostatic lithography and a positively biased scanning probe tip [44]. Figure 2.7 indicates that the 0.5 plateau is best defined when the potential is most symmetric and in that situation the 0.7 structure moves toward  $2e^2/h$ . The 0.7 structure has the same temperature dependence as discussed above. The 0.5 plateau also survives at higher temperature and increases slightly with increasing temperature from 150 mK to 3.0 K. A magnetic field perpendicular to the plane of the

**Fig. 2.7.** Conductance of quantum-wire device as a function of tip bias voltage at 150 mK for different potential landscapes. The green plot is for symmetric potential landscape. The plots have been offset and linearly scaled along x-axis for clarity [44].

device up to 1.2 T shows no effect on both the 0.5 and 0.7 plateaus. Though in-plane parallel magnetic field has been routinely used to study this anomaly, this is the first time that a perpendicular magnetic field was used.

In a very recent study, a tunable quantum dot has been used to study the 0.7 *Structure* [52]. By adjusting the bias voltages of various gates, that form the quantum dot, it is possible to tune on and off the anomaly or to make it continuously evolve into a normal integral conductance plateau. *A small magnetic field of 0.15T applied perpendicular to the plane of the device suppressed the 0.7 anomaly.*

It is noted that the anomalous conductance plateaus have been observed in the range (0.7- 0.5) ( $2e^2/h$ ) depending on the device. In the same device the anomalous feature also depends on the gate bias voltages. In addition, the 0.7 Structure is not a regular feature of the ballistic conductance of QPCs or 1D quantum wires. There are many cases where it is absent.

The experimental observations of the 0.7 structure show the following main features:

(1) The 0.7 structure is feeble at low temperature but becomes prominent at higher temperature (Figs. 2.4 (a) and 2.5(b)). The 0.7 structure exists at temperatures when the normal conductance plateaus disappear due to thermal smearing and indicates *that this anomaly is not related with the ballistic transport*,

(2) In a parallel magnetic field this anomalous plateau smoothly evolved to the Zeeman spin-split plateau at  $G = 0.5(2e^2/h)$  (Fig. 2.5 (b)),

(3) The formation of a zero-bias anomaly (ZBA) in the non-linear differential conductance. The ZBA disappears with an increase of temperature in zero magnetic field and also disappears with an increase in applied parallel magnetic field (Fig.2.6), and

(4) These anomalous plateaus do not appear on all devices and very much depend on the bias gate voltages of the device. Hence, this 0.7 structure strongly depends on the details of the lateral confining potential [44, 47, 52]

These experimentally observed features of the 0.7 structure inspired many theoretical models to explain the origin of this anomalous structure. The 0.7 structure disappears with the appearance of the zero bias anomaly (ZBA) peak, which suggests a relation between the appearance of the ZBA and the 0.7 structure. The formation of ZBA and its disappearance as the temperature is raised and in parallel magnetic field are the characteristics of the Kondo effect in quantum dots [53, 54]. The Kondo model is based on local moments or localized spins. But it is hard to understand how this localized spin can form in the open QPC device. Based on the spin-density functional theory (SDFT), it has been shown that a 'dynamical' local moment with a net of one spin forms in the vicinity of the QPC barrier [55]. The Kondo resonance gives rise to a dynamic unpaired spin and should result in *dynamic* spin polarization that cannot lead to static spin polarization that can be detected in low-frequency conductance measurements.

In attempt to explain the 0.7 structure, a semi-empirical model was proposed [56] that considers a spin gap opening up as the electron density in the QPC is increased by adjusting the gate bias voltages. This results in a static spin polarization and a feature near 0.5  $(2e^2/h)$  at low temperature is predicted. This model also shows that as the temperature is increased this feature moves smoothly and settles around 0.7  $(2e^2/h)$ . This explains the temperature behavior of the 0.7 structure. This spin-polarization model was later adopted by others and put on microscopic theoretical grounds using DFT [57]. In this theoretical work [57], two models were considered: (a) with exchange only and (b)

with exchange and correlations. The exchange only model predicts a feature at  $0.5 (2e^2/h)$  and suggests a fully spin-polarized ground state. But, in the exchange and correlations model, a metastable state is predicted as soon as the correlation is introduced. This weakens the polarization and as a consequence the conductance rises from 0.5  $(2e^2/h)$  toward the normal conduction quantization and manifests the 0.7 structure. As the temperature is raised, the metastable states become thermally activated, and as a consequence, the conductance decreases for a given voltage. This explains the temperature dependence of the 0.7 anomaly. A Green's function technique within DFT has also been used and gives spontaneous spin polarization [58]. The spin polarization models, nevertheless, fail to explain the zero-bias anomaly. Moreover, the well-known theory of Lieb and Mattis [59] forbids spin polarization in the ground state of a 1D system in the absence of magnetic field.

Based on strictly one-dimensional Luttinger liquid (LL) state, a *Wigner-crystal model* has also been proposed to explain the 0.7 structure and its temperature dependence [60]. In a 1D system the Coulomb interaction becomes prominent with decreasing electron density *n*. In the low density regime, the Coulomb energy dominates over the kinetic energy of the electron and electrons occupy equidistant position in 1D to minimize the Coulomb repulsion. This is known as a 1D Wigner crystal. Therefore, the ground state of a strictly 1D system with low electron density and strong electronelectron interaction is a Wigner crystal. The electrons occupy fixed positions on the Wigner lattice and are antiferromagnetically coupled. The ground state is not thus spinpolarized and is therefore in agreement with the Lieb and Mattis theorem. The low energy properties of the system are described by the Luttinger liquid (LL) theory. The resistance of the 1D quantum wire is determined by the charge and the spin excitations of the system,  $R = R_{\rho} + R_{\sigma}$ , where  $R_{\rho}$  is the resistance due to charge and  $R_{\sigma}$  is the resistance due to the spin excitations. At low temperature the contribution of the charge mode is always  $R_{\rho} = h/2e^2$ . At very low temperatures when T <<J, the exchange energy, the spin contribution to resistance vanishes so that the conductance is  $G = (2e^2/h)$ . At higher temperatures due to thermal activation  $R_{\sigma}$  grows and at T>>J, it saturates at  $R_{\sigma} = h/2e^2$ . This theory predicts the conductance anomaly at 0.5  $(2e^2/h)$  but fails to explain the anomaly at 0.7  $(2e^2/h)$ . The thermal length,  $L_T$ , is inversely proportional to temperature  $(L_T \propto \hbar v_F/KT)$ . Therefore, for a QPC or a short wire the device length, L, is smaller than the thermal length  $(L <<L_T)$  for low temperatures. So, it is difficult to understand how LL theory can be applied to a QPC or a short quantum wire, especially at low temperatures when the thermal length can considerably exceed the device length.

From the above discussion it can be concluded that as of now there has been no satisfactory explanation of the origin of the 0.7 *Structure* or other anomalous conductance plateaus. A complete understanding of the existence of these anomalous conductance plateaus remains elusive.

The spin-polarization model does, however, deserve a special attention. As it has been stated earlier that, a QPC or a short quantum wire is very likely not a strictly 1D system; hence the theorem of Lieb and Mattis may not be applicable to them. Moreover, a static spin polarization has been experimentally found to be associated with the 0.7 anomaly in a hole QPC [47]. In this work, the authors made use of the large spin-orbit interaction (SOI) in a hole gas. The SOI causes spin splitting of the 1D subband along the direction of the *k* propagation vector. As a result, carriers with opposite spin travel with different Fermi momenta and have different cyclotron orbits in external perpendicular magnetic

**Fig. 2.8.** (a) Magnetic focusing geometry showing injector and detector QPCs and the schematic trajectories of holes with two spin states. (b) Focusing peak measured at different injector conductance  $G_i$ . The curves are vertically offset by -0.4µV relative to the top one. The  $G = 0.66(2e^2/h)$  is also plotted without offset (dashed red) [47].

field. The experiment used two QPCs: QPC1 as the injector and QPC2 as the detector of electrons in a magnetic focusing geometry (Fig. 2.8(a)). A current was injected through QPC1 and the voltage drop was measured across QPC2. The transmission of both the QPCs, QPC1 and QPC2, were set at the conductance value of  $G = (2e^2/h)$ and two voltage peaks were observed at two different focusing magnetic fields corresponding to the two spin. One of the peaks slowly disappeared as the transmission of QPC1 was lowered and is shown in Fig. 2.8(b). This allowed a measurement of the polarization of the injected current. A polarization of  $40\pm15\%$ was measured for  $G<0.9G_0$ . It should be noted that the appearance of the anomalous 0.7 plateau and other similar anomalous plateaus requires an energy spin splitting of the two spin bands comparable to or larger than the energy level broadening. In cases where this condition is not met, the anomalous plateaus cannot be observed. *The origin of the spin splitting that causes the spontaneous spin polarization remains an unanswered, open question.* Since the anomalous 0.7 structure and other similar anomalous plateaus in the range (0.5-0.7) (2e<sup>2</sup>/h) can be tuned to appear or disappear by adjusting the bias voltages of the gates that create the potential confinement of the QPCs, it seems likely that *the profile of this confinement plays a crucial role* in this phenomenon.

# References

- 1. Semiconductor Spintronics and Quantum Computation, edited by D. D. Awschalom, D. Loss, and N. S (Springer, Berlin, 2002).

- 2. I. Zutic, J. Fabian, and S. Das Sarma, *Spintronics: Fundamentals and Applications*, Rev. Mod. Phys. **76**, 323 (2004).

- **3.** Yu. A. Bychkov and E. I. Rashba, *Oscillatory effects and the magnetic susceptibility of carriers in inversion layers*, J. Phys. C **17**, 6039 (1984).

- **4.** Yongin Jiang and Liangbin Hu, *Kinetic magnetoelectric effect in a twodimensional semiconductor strip due to boundary-confinement-induced spin-orbit coupling*, Phys. Rev. B **74**, 075302 (2006).

- **5.** Yanxia Xing, Qing-feng Sun, Liang Tang and Jiang Ping Hu, Accumulation of opposite spins on the transverse edges of a two dimensional electron gas in a longitudinal electric field, Phys. Rev. B **74**, 155313 (2006).

- 6. J.D. Bjorken and S.D. Drell, *Relativistic Quantum Mechanics* (McGraw-Hill, New York, 1965).

- 7. John Schliemann, Spin Hall Effect, Int. J. Mod. Phys. B 20, 1015 (2006).

- E. I. Rashba, *Electron spin operation by electric fields: spin dynamics and spin injection*, Physica E 20 189-195 (2004).

- **9.** V. G. Kantser, *Materials and structures for semiconductor spintronics*, Journal of Optoelectronics and advanced materials, **Vol. 8**, No. 2, 425-438 (2006).

- 10. G. Dresselhaus, Spin-OrbitCoupling Effects in Zinc Blende Structures, Phys. Rev.

100, 580 (1955).

- 11. M. I. Dyakonov and V. Y. Kachorovoskii, Sov. Phys. Semicond. 20, 110 (1986).

- **12.** G. Bastard and R. Ferreira, *Spin-flip scattering times in semiconductor quantum wells*, Surf. Science **267**, 335 (1992).

- **13.** D. G. Seiler, B. D. Bajaj, A. E. Stephens, *Inversion-asymmetry splitting of the conduction band in InSb*, Phys. Rev. B **16** (6), 2822-2833 (1977).

- 14. H. Riechert, S. F. Alvarado, A. N. Titkov, V. I. Safarov, Precession of the Spin Polarization of Photoexcited Conduction Electrons in the Band-Bending Region of GaAs (110), Phys. Rev. Lett. 52 (25), 2297-2300 (1984).

- **15.** A. Lusakowski, J. Wrobel, T. Dietl, *Effect of bulk inversion asymmetry on the Datta-Das transistor*, Phys. Rev. B **68**, 081201 (2003).

- 16. H. L. Stormer, Z. Schlesinger, A. Chang, D. C. Tsui, A.C. Gossard and W. Wiegmann, *Energy Structure and Quantized Hall Effect of Two-Dimensional Holes*, Phys. Rev. Lett. 51, 126 (1983).

- **17.** Th. Schapers, G. Engels, J. Lange, Th. Klocke, M. Hollfelder, and H. Lüth, *Effect* of the heterointerface on the spin splitting in modulation doped  $In_xGa_{1-x}As/InP$  quantum wells for  $B \rightarrow 0$ , J. Appl. Phys. **83**, 4324 (1998).

- 18. B. Das, D. C. Miller, S. Datta, R. Reifenberger, W. P. Hong, P. K. Bhattacharya, J. Singh, and M. Jaffe, *Evidence for spin-splitting in In<sub>x</sub>Ga<sub>1-x</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As heterostructures as B→0*, Phys. Rev. B 39, 1411 (1989).

- 19. L. J. Cui, Y. P. Zeng, B. Q. Wang, Z. P. Zhu, L. Y. Lin, C. P. Jiang, S. I. Guo, J. H. Chu, Zero-field spin splitting in In<sub>0.52</sub>Al<sub>0.48</sub>As/In<sub>x</sub>Ga<sub>1-x</sub>As metamorphic high-electron-mobility-transistor structures on GaAs substrates using Shubnikov-de Haas measurements, Appl. Phys. Lett. 80, 3132 (2002).

- 20. Luo, H. Munekata, F. F. Fang, and P. J. Stiles, *Effects of inversion asymmetry on electron energy band structures in GaSb/InAs/GaSb quantum wells*, Phys. Rev. B 41, 7685 (1990).

- 21. C. M. Hu, J. Nitta, T. Akazaki, H. Takayanagi, J. Osaka, P. Pfeffer, and W. Zawadzki, Zero-field spin splitting in an inverted In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As heterostructures:Band nonparabolicity influence and the subband difference, Phys. Rev. B 60, 7736 (1999).

- 22. Y. Kato, R. C. Myers, A. C. Gossard, and D. D. Awschalom, *Coherent spin manipulation without magnetic fields in strained semiconductors*, Nature, 427, 50 (2004).

- 23. S. Datta and B. Das, *Electronic analog of the electro-optic modulator*, Appl. Phys. Lett. 56, 665 (1990).

- 24. P. R. Hammar and Mark Johnson, *Detection of Spin-Polarized Electrons Injected into a Two-Dimensional Electron Gas*, Phys. Rev. Lett. **88**, 066806 (2002).

- **25.** G. Meier et, T. Matsuyama, and U. Merkt, *Field effect in InAs/permalloy hybrid transistors*, Phys. Rev. B **65**, 125327 (2002).

- 26. Kiminori Hattori and Hiroaki Okamoto, Spin separation and spin-Hall effect in quantum wires due to lateral-confinement-induced spin-orbit coupling, Phys. Rev. B 74, 155321 (2006).

- **27.** R. Winkler, *Spin-Orbit Coupling Effects in Two Dimensional Electron and Hole Systems* (Springer, Berlin 2003).

- 28. S. Murakami, N. Nagaosa, and S. -C. Zhang, *Dissipationless quantum spin current at room temperature*, Science 301, 1348 (2003).

- 29. J. Sinova, D. Culcer, Q. Niu, N. A. Sinitsyn, T. Jungwirth, and A. MacDonald, Universal Spin Hall Effect, Phys. Rev. Lett. 92, 126603 (2004).

- **30.** S. Zhang, Spin Hall effect in the presence of spin diffusion, Phys. Rev. Lett. **85**, 393 (2000).

- 31. J. E. Hirsch, Spin Hall effect, Phys. Rev. Lett. 83, 1834 (1999).

- **32.** I. D'yakonov and V. I. Perel, *Current-induced spin orientation of electrons in semiconductors*, Physics Letters **35A**, 459 (1971).

- **33.** Y. K. kato, R. C. Myers, A. C. Gossard, and D. D. Awschlom, *Observation of the Spin Hall Effect in Semiconductors*, Science **306**, 5703 (2004).

- 34. J. Wunderlich, B. Kastner, J. Sinova, and T. Jungwirth, *Experimental discovery of the spin-Hall effect in Rashba spin-orbit coupled semiconductor systems*, Phys. Rev. Lett. 94, 047204 (2005)

- **35.** B. J. van Wees, H. van Houten, C. W. J. Beenakker, J. G. Williamson, L. P. Kouwenhoven, D. van der Marel. And C. T. Foxon, *Quantized conductance of point contacts in a two-dimensional electron gas*, Phys. Rev. Lett. **60**, 848 (1988).

- 36. D. A. Wharam, T. J. Thornton, R. Newbury, M. Pepper, H. Ahmed, J. E. F. Frost,

D. G. Hasko, D. C. Peacock, D. A. Rictchie, and G. A. C. Jones, *One-dimensional* transport and the quantisation of the ballistic resistance, J. Phys. C 21, L209 (1988).

- 37. K. J. Thomas, J. T. Nicholls, M. Y. Simmons, M. Pepper, D. R. Mace, and D. A. Ritchie, *Possible Spin Polarization in a One-Dimensional Electron Gas*, Phys. Rev. Lett., 77, 135 (1996).

- 38. A. Kristensen, H. Bruus, A. E. Hansen, J. B. Jensen, P. E. Lindelof, C. J. Marckmann, J. Nyga°rd, and C. B. Sørensen, *Bias and temperature dependence of the 0.7 conductance anomaly in quantum point contacts*, Phys. Rev. B 62, No. 16 (2000).

- 39. K. J. Thomas, J. T. Nicholls, M. Pepper, W. R. Tribe, M. Y. Simmons, and D. A. Ritchie, *Spin properties of low-density one-dimensional wires*, Phys. Rev. B 61, R 13365 (2000).

- 40. D. J. Reilly, G. R. Facer, A. S. Dzurak, B. E. Kane, R. G. Clark, P. J. Stiles, R. G. Clark, A. R. Hamilton, J. L. O'Brien, N. E. Lumpkin, L. N. Pfeiffer and K. W. West, *Many-body spin-related phenomena in ultra low-disorder quantum wires*, Phys. Rev. B 63, 121311 (2001).

- 41. A.C. Graham, K.J. Thomas, M. Pepper, M.Y. Simmons1, D.A. Ritchie, 0.7 Structure in quantum wires observed at crossings of spin-polarised 1D subbands, Physica E 22, 264-267, (2004).

- **42.** R. de Picciotto, L. N. Pfeiffer, K. W. Baldwin, and K. W. West, *Temperaturedependent 0.7 structure in the conductance of cleaved-edge-overgrowth onedimensional wires*, Phys. Rev. B 72, 033319 (2005).

- **43.** O. Gunawan, B. Habib, E. P. De Poortere, and M. Shayegan, *Quantized conductance in an AlAs two-dimensional electron system quantum point contact*, Phys. Rev. B 74, 155436 (2006).

- **44.** R. Crook, J. Prance, K. J. Thomas, S. J. Chorley, I. Farrer, D. A. Ritchie, M. Pepper, C. G. Smith, *Conductance Quantization at a Half-Integer Plateau in a Symmetric GaAs Quantum Wire*, Science **312** (2006).

- 45. Th. Schäpers, V. A. Guzenko, and H. Hardtdegen, Zeeman splitting in ballistic GaInAs/InP split-gate quantum point contacts, Appl. Phys. Lett., 90. 122107 (2007).

- 46. R. Danneau, O. Klochan, W. R. Clarke, L. H. Ho, A. P. Micolich, M. Y. Simmons, A. R. Hamilton, M. Pepper, D. A. Ritchie, and U. Zülicke, *Zeeman Splitting in Ballistic Hole Quantum Wires*, Phys. Rev. Lett. 97, 026403 (2006).

- 47. L. P. Rokhinson, L. N. Pfeiffer, and K. W. West, *Spontaneous Spin Polarization in Quantum Point Contacts*, Phys. Rev. Lett. 96, 156602(2006).

- 48. R. Danneau, W. R. Clarke, O. Klochan, A. P. Micolich, A. R. Hamilton, M. Y. Simmons, M. Pepper and D. A. Ritchie, *Conductance quantization and the 0.7×2e<sup>2</sup>/h conductance anomaly in one-dimensional hole systems*, Appl. Phys. Lett. 88, 012107 (2006).

- 49. M. J. Biercuk, N. Mason, J. Martin, A. Yacoby, and C. M. Marcus, *Anomalous Conductance Quantization in Carbon Nanotubes*, Phys. Rev. Lett. 94, 026801(2005).

- 50. P. Debray, unpublished (1999).

- 51. S. M. Cronenwett, H. J. Lynch,1 D. Goldhaber-Gordon, L. P. Kouwenhoven, C. M. Marcus, K. Hirose, N. S. Wingreen,5 and V. Umansky, Low-Temperature Fate of the 0.7 Structure in a Point Contact: A Kondo-like Correlated State in an Open System, Phys. Rev. Lett. 88, 226805 (2002).

- 52. Yunchul Chung, Sanghyun Jo, Dong-In Chang, Hu-Jong Lee, M. Zaffalon, V. Umansky, and M. Heiblum, *Tunable 0.7 conductance plateau in quantum dots*, Phys. Rev. B 76, 035316 (2007).

- **53.** L. Kouwenhoven and L. Glazman, *Revival of the Kondo effect*, Physics World, January 2001.

- **54.** R. M. Potok, I. G. Rau, Hadas Shtrikman, Yuval Oreg and D. Goldhaber-Gordon, Observation of the two-channel Kondo effect, Nature **446**, 167 (2007).

- **55.** Kenji Hirose, Yigal Meir, and Ned S.Wingreen, Local *Moment Formation in Quantum Point Contacts*, Phys. Rev. Lett. **90**, 026804 (2003).

- **56.** D. J. Reilly, *Phenomenological model for the 0.7 conductance feature in quantum wires*, Phys. Rev. B **72**, 033309 (2005).