# **UNIVERSITY OF CINCINNATI**

Date:\_Nov 10, 2005\_\_\_\_\_

I, \_Shuguang Wu\_\_\_\_\_\_, hereby submit this work as part of the requirements for the degree of:

Master of Science

in:

Computer Engineering

It is entitled:

FPGA Implementation of the FDTD Algorithm Using

Local SRAM

This work and its defense approved by:

Chair: \_Dr. Karen A. Tomko\_\_\_\_\_ \_Dr. Harold W. Carter\_\_\_\_\_ \_Dr. Wen-Ben Jone\_\_\_\_\_

# **FPGA Implementation of the FDTD Algorithm**

# **Using Local SRAM**

A thesis submitted to the

Division of Research and Advanced Studies of The University of Cincinnati

in partial fulfillment of requirements for the degree of

## **Master of Science**

in the

Department of Electrical & Computer Engineering and Computer Science of The College of Engineering

November 2005

by

#### **Shuguang Wu**

B.E., Beijing University of Posts and Telecommunications, 1996 M.E., Beijing University of Posts and Telecommunications, 1999

Thesis Advisor and Committee Chair: Dr. Karen A. Tomko

# Abstract

The Finite-Difference Time-Domain (FDTD) algorithm is a powerful tool to model electromagnetic phenomena. It is computation-intensive. Plenty of work has been done to implement this algorithm on FPGA and to improve the implementation performance.

This thesis presents an implementation of the FDTD algorithm on FPGA in two reconfigurable computing systems in order to explore the implementation feasibility and to improve the implementation performance. The two reconfigurable computing systems used in this thesis are a prototyping system in the ACL Lab at University of Cincinnati and a Cray XD1 system available at the Ohio Supercomputer Center. There are three major functional units in the FPGA: update engines calculating three equations in the FDTD algorithm, interface to host system, interface to local SRAMs. The local SRAMs are used to store input and output data for the FDTD algorithm. The purpose to use the local SRAMs is to reduce the data transfer between the host system and the FPGA. Host applications are developed to verify the FPGA implementation.

# Acknowledgement

I'm extremely grateful to my advisor Dr. Karen A. Tomko for her precious guidance and encouragement during the work on my thesis. It is really great honor for me to work with her. And I'm very thankful for her kindness, support and co-operation.

I'm thankful to Dr. Harold W. Carter and Dr. Wen-Ben Jone for participating in my thesis committee.

SynplifyPro used in this project is provided by Synplicity through their University Program, Xilinx ISE is provided by Xilinx through Xilinx's University Program (XUP), and Modelsim is donated from Mentor Graphics as part of their Higher Education Program (HEP).

I would like to thank the members in our group for their help. They are: Sachin Gandhi, Robert Cully, Ashish Desai. It is great pleasure to work with them.

And I express my great gratitude to my parents and my sisters. Their love, encouragement and support accompany me forever.

# **Table of Contents**

| 1 | Intro | duction                                                           |

|---|-------|-------------------------------------------------------------------|

|   | 1.1   | Overview 1                                                        |

|   | 1.2   | Related Work 4                                                    |

|   |       | 1.2.1 Reconfigurable Computing System                             |

|   |       | 1.2.2 FPGA Implementation of Floating Point Algorithm5            |

|   |       | 1.2.3 FPGA Implementation of FDTD Algorithm7                      |

|   | 1.3   | Thesis Organization                                               |

| 2 | Finit | e-Difference Time-Domain Algorithm for Electromagnetic Simulation |

|   |       |                                                                   |

| 3 | FPG   | A-Based Reconfigurable Computing Systems                          |

|   | 3.1   | Laboratory Prototype System14                                     |

|   |       | 3.1.1 System Architecture14                                       |

|   |       | 3.1.2 Simulation Environment                                      |

|   |       | 3.1.3 Host Programming Environment                                |

|   | 3.2   | Cray XD1 System                                                   |

|   |       | 3.2.1 System Architecture                                         |

|   |       | 3.2.1.1 Cray XD1 Chassis                                          |

|   |       | 3.2.1.2 RapidArray Interconnect                                   |

|   |       | 3.2.2 Simulation Environment                                      |

|   |       | 3.2.3 Host Programming Environment                                |

| 4 | FDT   | D FPGA Implementation using Local SRAM                            |

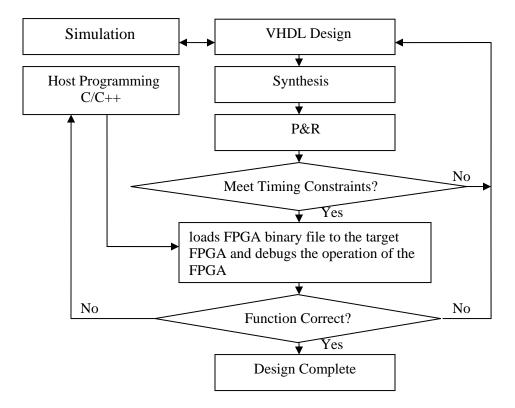

|   | 4.11 | FPGA Implementation Flow                           | 3 |

|---|------|----------------------------------------------------|---|

|   | 4.21 | FPGA Implementation in the ACL Prototype System 28 | } |

|   |      | 4.2.1 VHDL Design                                  | } |

|   |      | 4.2.1.1 FPGA Function                              | 3 |

|   |      | 4.2.1.2 FPGA Architecture                          | 0 |

|   |      | 4.2.1.3 Data Organization in Local Memories        | 2 |

|   |      | 4.2.1.4 Components and Processes                   | 3 |

|   |      | 4.2.2 Simulation                                   | 1 |

|   |      | 4.2.3 Synthesis                                    | 1 |

|   |      | 4.2.4 P&R                                          | 2 |

|   |      | 4.2.5 Host Programming 4                           | 2 |

|   | 4.31 | FPGA Implementation in the Cray XD1 System         | 3 |

|   |      | 4.3.1 VHDL Design                                  | 3 |

|   |      | 4.3.1.1 FPGA Function                              | 1 |

|   |      | 4.3.1.2 FPGA Architecture4                         | 5 |

|   |      | 4.3.1.3 Data Organization in Local Memories        | 6 |

|   |      | 4.3.1.4 Components and Processes                   | 8 |

|   |      | 4.3.2 Simulation                                   | 7 |

|   |      | 4.3.3 Synthesis                                    | 8 |

|   |      | 4.3.4 P&R                                          | 9 |

|   |      | 4.3.5 Host Programming                             | 9 |

| 5 | Theo | pretical Performance Analysis and Future Work      | 1 |

|   | 5.1  | Performance Analysis in the Prototype System       | 2 |

| 5.2 Perf     | formance Analysis in the Cray XD1 System 6 | 33 |

|--------------|--------------------------------------------|----|

| 5.3 Perf     | formance Comparison6                       | 5  |

| 5.4 Futu     | ure Work in the Cray XD1 System            | 6  |

| Bibliography |                                            | 39 |

# List of Figures

| Figure 3-1 :  | Reconfigurable Computing System                              |

|---------------|--------------------------------------------------------------|

| Figure 3-2 :  | FIREBIRD <sup>™</sup> /PCI block diagram                     |

| Figure 3-3 :  | Cray XD1 chassis                                             |

| Figure 3-4 :  | Expansion Module                                             |

| Figure 4-1 :  | FPGA Implementation Flow                                     |

| Figure 4-2 :  | FPGA Architecture in the Prototype System                    |

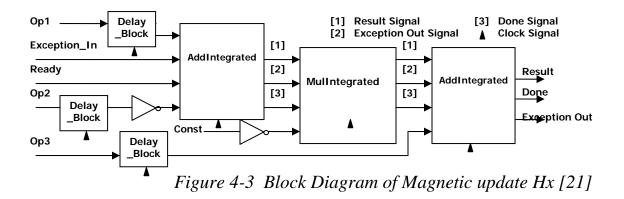

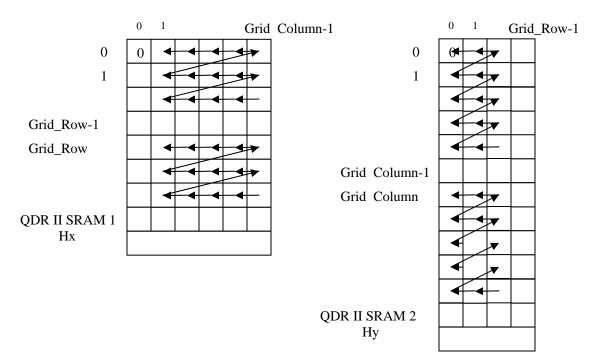

| Figure 4-3 :  | Block Diagram of Magnetic update Hx                          |

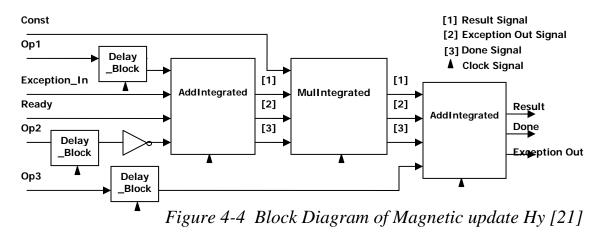

| Figure 4-4 :  | Block Diagram of Magnetic update Hy                          |

| Figure 4-5 :  | Block Diagram of Electric update                             |

| Figure 4-6 :  | Structure of the Test Bench in the Prototype System41        |

| Figure 4-7 :  | FPGA Architecture in the Cray XD1 System                     |

| Figure 4-8 :  | Parameters in Register FPGA_reg51                            |

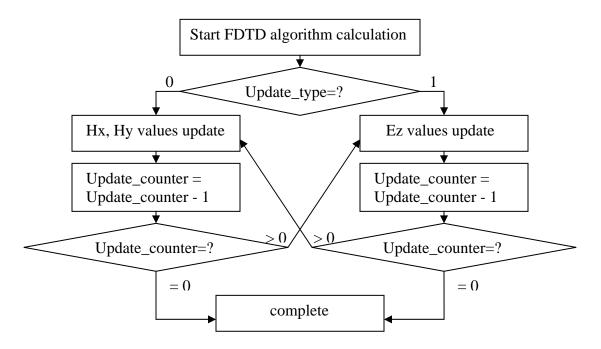

| Figure 4-9 :  | Procedure for FDTD algorithm calculation                     |

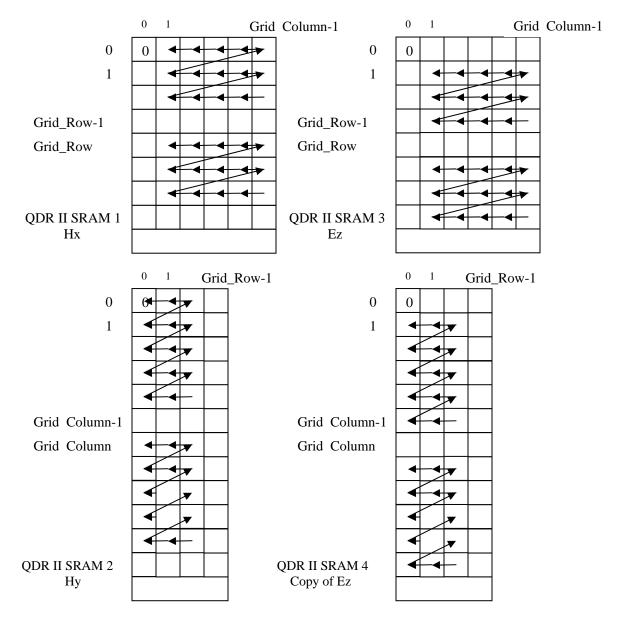

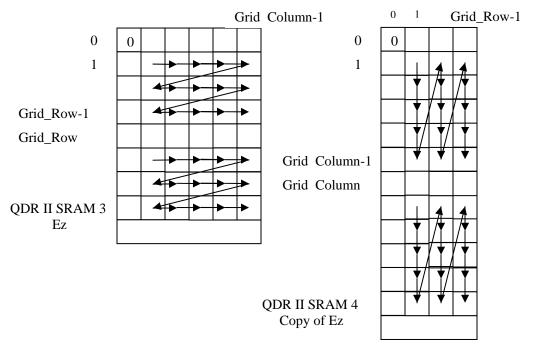

| Figure 4-10 : | Read Addresses Generation Order for Hx, Hy values update 54  |

| Figure 4-11 : | Write Addresses Generation Order for Hx, Hy values update 55 |

| Figure 4-12 : | Read Addresses Generation Order for Ez values update 56      |

| Figure 4-13 : | Write Addresses Generation Order for Ez values update 57     |

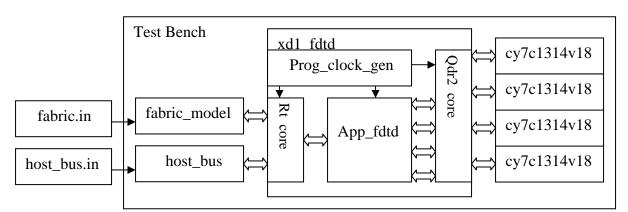

| Figure 4-14 : | Structure of the Test Bench in the Cray XD158                |

#### Chapter 1

#### Introduction

#### 1.1 Overview

This thesis presents an implementation of the Finite-Difference Time-Domain (FDTD) algorithm on FPGA in two reconfigurable computing systems. Local SRAMs are used to store input and output data for the FDTD algorithm. Host applications are developed to verify the implementation and to evaluate performance of the implementation.

The work done in this thesis is based on the work done by Gandhi. Gandhi implemented the FDTD algorithm in a reconfigurable computing system named Heterogeneous HPC computer (HHPC) [21]. His work focuses on speedup of three equations in the FDTD algorithm. In his thesis, three update engines are implemented to calculate three equations in the FDTD algorithm, and parallelism and pipelining are utilized to speed up these update engines. Input and output data are stored in host system memories. For each iteration of FDTD algorithm calculation, input and output data must be transferred between the host system and the FPGA. This slow data communications is performance bottleneck and greatly degrades the performance of the whole system.

In this thesis, the implementation focuses on speedup of the whole process to complete the FDTD algorithm. The whole process includes input and output data transfer between the host system and the FPGA and data update by the update engines. In order to realize this goal, the implementation is done in two reconfigurable computing systems different from the HHPC system. Local SRAMs attached to the FPGA are used to store input and output data to reduce data transfer between the host system and the FPGA.

The two reconfigurable computing systems used in this thesis are a prototyping system in the ACL Lab at University of Cincinnati which is referred to as the Prototype System throughout this thesis and a Cray XD1 system available at the Ohio Supercomputer Center. The Prototype system consists of a PC and a reconfigurable computing board. In the Prototype system, FPGA and local SRAMs are located on the reconfigurable computing board, host applications run on the host PC. The Cray XD1 system consists of a number of Cray chassis connected by a switch fabric. Each chassis consists of one management processor and six compute blades. In the Cray XD1 system, host processors are located on the compute blades and host applications run on the host processors. FPGAs and local SRAMs are attached to the compute blades.

There are three major functional units in the FPGA: update engines calculating three equations in the FDTD algorithm, interface to the host system, interface to the local SRAMs. The update engines are implemented using floating point units. Two update engines are used to update magnetic field values, one is used to update electric field values. These update engines are pipelined. Furthermore, in the Cray XD1 system, the two update engines used to update magnetic field values are processed in parallel. Due to the pipelining and the parallelism, throughput and speed of the implementation improve. Interface to the host system interacts with the host system. The host system issues commands such as read and write to the FPGA through this interface. The FPGA processes the received commands and gives response to the host system through this interface, too. Interface to the local SRAMs is used for the FPGA to read and write the local SRAMs.

In order to reduce the data transfer between the host system and the FPGA, input and output data for the FDTD algorithm are stored in the local SRAMs. In the Prototype system, local SRAMs are single-port memories. They can't be read and written simultaneously. Three local SRAMs are used to store input data and two are used to store output data for the FDTD algorithm. Input data should be transferred from the host system to the input SRAMs before the calculation of the FDTD algorithm begins. When one iteration of calculation completes, the results will be stored in the output SRAMs and the host system should read the results back from the output SRAMs. In the Cray XD1 system, there are four dual-port SRAMs. They can be read and written at the same time as long as the read address and the write address are not the same. These SRAMs are organized as ping-pong SRAMs. This ping-pong mechanism enables the FPGA to execute many iterations of calculation with little communication with the host system. Reduction of data transfer between the host system and the FPGA during intervals between calculation iterations greatly improves the performance of the whole system.

In this thesis, the main purpose of developing the host application is to verify the FPGA implementation. Though the FPGA design is already simulated and debugged after VHDL design completes, the FPGA design still needs to be verified to run correctly in the actual system. So host application needs to be developed to verify the function of the FPGA implementation. The host application loads the FPGA binary file into the FPGA, writes data to and reads data from the registers in the FPGA or the local SRAMs through the FPGA. It also starts the internal update engines in the FPGA and monitors the status

of the update engines. By this method, all the functional units of the FPGA can be verified.

The host application can also be augmented to evaluate the performance of the FPGA implementation. The experimental evaluation is the work of another member in our group. In this thesis, only theoretical analysis and evaluation of performance of the FPGA implementation is done.

#### **1.2 Related Work**

### **1.2.1 Reconfigurable Computing System**

FPGA was first introduced in early 1990s. Since then, a lot of reconfigurable computing systems have been developed. C.E. Cox et al. developed a reconfigurable computing system named GANGLION [1]. GANGLION was a fast digital connectionist classifier. Its architecture was realized using a FPGA array on a VME card attached to a workstation. M. Wazlowski et al developed PRISM II [2]. PRISM II was a general purpose hardware platform. It mainly consisted of PRISM host processor and reconfigurable hardware platform. The compiler for PRISM II accepted a host application as input and produced hardware image and software image. The hardware image was used for programming the hardware platform. The Splash 2 system was developed by D. Buell et al. [3]. It consisted of a Sun workstation, an interface board, and Splash array boards. FPGAs on each array board were arranged in a linear array and were connected via a crossbar switch. The Splash 2 system was effective on applications such as text searching, sequence analysis and image processing. T.Tsutsui et al. developed YARDS [4]. YARDS comprised three cards: the main card, the MPU card, and the FPGA card.

There were a FPGA array mounted on the FPGA card. Several telecommunication applications were developed in the YARDS system.

Miyazaki, T categorized reconfigurable computing systems into three types: attached processors, coprocessors and special purpose machines [5]. He also investigated typical applications suitable for reconfigurable computing systems. Smith, M.C. et al. investigated the hardware architecture and configuration of reconfigurable computing system [6]. Software architecture of reconfigurable computing system was discussed, too. Fidanci, O.D. et al. overviewed hardware architecture and programming model of SRC-6E<sup>TM</sup> reconfigurable computers [7]. The SRC-6E could outperform a generalpurpose microprocessor for computationally intensive algorithms whether or not the overhead due to configuration and data transfer was included. The paper presented by El-Araby, E. et al. was also based on the SRC-6E<sup>TM</sup> reconfigurable computers [8]. They put their concern on the DMA transfer between the host system and the FPGA. Theoretical model was built and analyzed for this performance bottleneck. Experimental work was done to verify the theoretical analysis.

The reconfigurable computing systems used in this thesis include the Prototype system and the Cray XD1 system. Based on the paper presented by Miyazaki, T [5], the Prototype system can be categorized into attached processors, the Cray XD1 system can be categorized into coprocessors.

#### **1.2.2 FPGA Implementation of Floating Point Algorithm**

The most commonly used format for floating point numbers is described in IEEE Std 754 [9]. Until the late 1990s, the resource and speed of FPGA was restricted and it was difficult to implement floating point arithmetic on FPGA. Many people explored and analyzed the feasibility and performance of implementation of floating point algorithm on FPGA during this period. B. Fagin et al. implemented floating point adder and multiplier using FPGA and discussed the tradeoff between performance and area requirement [10]. N. Shirazi et al. designed and optimized floating point adder/subtracter, multiplier and divider to maximize speed and to minimize area [11]. L. Louca et al. implemented floating point adder and multiplier and investigated the area-speed tradeoff [12]. W. B. Ligon III et al. presented implementation of floating point addition and multiplication functional units and discussed the performance and device utilization of these units [13].

From the beginning of 2000s, the resource and speed of FPGA increases greatly and area is no longer the overriding concern for implementation of floating point algorithm. More efforts are focused on performance and optimization of the implementation during this period. A. Jaenicke et al. presented an approach for developing and optimizing parameterized floating point units [14]. These units could be customized to meet user constraints by varying the precision, rounding modes, or the number of pipeline stages. Jian Liang et al. presented a floating point unit generation tool for FPGAs [17]. This tool could be used to create a variety of floating point units based on throughput, latency, and area requirements. Pavle Belanovic also presented a parameterized floating point library for use with reconfigurable hardware [15][16]. This library was fully parameterized for format control, arithmetic operations and conversion to and from any fixed-point format.

6

The floating point library presented by Pavle Belanovic is chosen for the FPGA implementation of FDTD Algorithm in my thesis.

#### **1.2.3 FPGA Implementation of FDTD Algorithm**

The first paper about FPGA implementation of FDTD algorithm was presented by Schneider et al. [18]. In his paper, one-dimensional FDTD algorithm was implemented on FPGA using a pipelined bit-serial arithmetic architecture. And the implementation used integer calculation. A one-dimensional resonator was used to verify the implementation and to explore the hardware speed and costs. Durbano et al. presented the first FPGA implementation of three-dimensional FDTD algorithm using floating point arithmetic units [19]. In his paper, system architecture for the FPGA implementation was introduced and functionality of each module in the system architecture was described. The speed of the implementation was more than 5 times slower than software implementation at that time. Chen et al. implemented two-dimensional FDTD algorithm on FPGA using fixed point arithmetic [20]. In the implementation, magnetic field updating algorithm along the x-coordinate and along the y-coordinate were processed in parallel, and magnetic field updating algorithms and electric field updating algorithm were partially paralleled. The components implementing the magnetic field updating algorithms and the electric field updating algorithm were designed as pipelines. The on-board memories stored the magnetic field values and the electric field values and were organized in a swapping mechanism. Another implementation of two-dimensional FDTD algorithm on FPGA was done by Gandhi [21]. In his master thesis, floating point arithmetic was used, three update engines magnetic update Hx, magnetic update Hy and

7

electric update were implemented to realize the magnetic field updating algorithms and the electric field updating algorithm, and parallelism and pipelining were utilized to speed up the implementation. The electric field values and the magnetic field values were stored in host system memories. The slow data communications between the host system and the FPGA degraded the performance of the whole system.

In my thesis, the update engines designed by Gandhi are used, local SRAMs are used to store the electric field values and the magnetic field values.

#### **1.3 Thesis Organization**

Chapter 1 introduces the work I have done. In summary, I have improved the FPGA implementation in [21] by utilizing SRAMs attached to the FPGA to reduce host-FPGA communications. Also introduced is related work done in the field of reconfigurable computing, on FPGA implementation of floating point algorithm and on FPGA implementation of FDTD Algorithm. Chapter 2 introduces the Finite-Difference Time-Domain (FDTD) algorithm. The method to derive FDTD algorithm from Maxwell's equations is also explained in this chapter. Chapter 3 describes the reconfigurable computing systems used in this thesis: the Prototype system and the Cray XD1 system. The architecture of each system is introduced, the simulation environment and the host programming environment provided by each system are described. Chapter 4 presents in detail the FPGA implementation of FDTD algorithm in the Prototype system and the Cray XD1 system. The FPGA implementation is divided into five stages: VHDL design, simulation, synthesis, P&R, host programming. The work done on each stage is explained in detail. Chapter 5 analyzes results and performance of the FPGA implementation done in this thesis and proposes some suggestions for the future work.

## Chapter 2

Finite-Difference Time-Domain Algorithm for Electromagnetic Simulation

The Finite-Difference Time-Domain (FDTD) algorithm is a very powerful tool for the modeling of electromagnetic phenomena. This algorithm is a set of discretized finite difference equations derived from Maxwell's equations. It was first presented by Kane S. Yee.

Maxwell's equations in an isotropic medium are [22]:

| $\partial B/\partial t + \nabla \times E = 0$ | (1a) |

|-----------------------------------------------|------|

| $\partial D/\partial t - \nabla \times H = J$ | (1b) |

| $B = \mu H$                                   | (1c) |

| $D = \varepsilon E$                           | (1d) |

The definitions for the symbols in the equations (1a)--(1d) are:

B - Magnetic flux density E - Electric field D - Electric flux density H - Magnetic field  $\mu - Magnetic permittivity$  $\varepsilon - Electric permittivity$  Maxwell's equations are very powerful in solving electromagnetic problems, but are not suitable for processing by computer. In 1966, Kane S. Yee successfully presented a method to discretize Maxwell's equations and to derive the FDTD algorithm [23].

There are two assumptions for the derivation. One is that the boundary condition should be appropriate for a perfectly conducting surface. This assumption implies that the tangential components of the electric field vanish and the normal component of the magnetic field vanishes on the surface. The other assumption is that the space grid size must be such that over one increment the electromagnetic field does not change significantly [23].

Based on these two assumptions, Kane S. Yee discretized both the physical region and the time interval of the Maxwell's equations on uniform grids. Then he derived the finite difference equations for two modes of electromagnetic waves: Transverse electric wave (TE) and Transverse magnetic wave (TM). Later these equations are named as Finite-Difference Time-Domain (FDTD) algorithm. Here only FDTD algorithm for the TM is presented [23]:

$$H_x^{n+1/2}(i,j+\frac{1}{2}) = H_x^{n-1/2}(i,j+\frac{1}{2}) - \frac{1}{Z}\frac{\Delta r}{\Delta y}[E_z^n(i,j+1) - E_z^n(i,j)]$$

(2a)

$$H_{y}^{n+1/2}(i+\frac{1}{2},j) = H_{y}^{n-1/2}(i+\frac{1}{2},j) + \frac{1}{Z}\frac{\Delta r}{\Delta x}[E_{z}^{n}(i+1,j) - E_{z}^{n}(i,j)]$$

(2b)

$$E_{z}^{n+1}(i,j) = E_{z}^{n}(i,j) + Z \frac{\Delta r}{\Delta x} [H_{y}^{n+1/2}(i+\frac{1}{2},j) - H_{y}^{n+1/2}(i-\frac{1}{2},j)] - Z \frac{\Delta r}{\Delta y} [H_{x}^{n+1/2}(i,j+\frac{1}{2}) - H_{x}^{n+1/2}(i,j-\frac{1}{2})]$$

(2c)

FDTD Algorithm for TM waves

The electromagnetic field values in the equations (2a)--(2c) are updated  $\frac{1}{2}$  time step by  $\frac{1}{2}$  time step from two parts: field values calculated in previous  $\frac{1}{2}$  time step and field values in adjacent space cells. This characteristic makes it possible to implement the FDTD algorithm on parallel computers because only nearest-neighbor interactions are involved.

There are many methods to implement FDTD algorithm on parallel computers. Commonly in these methods, the discretized physical space is partitioned into regions and distributed to multiple processors. Data on the boundaries between regions is exchanged between processors, the electric field values are updated and stored in memory using previously stored magnetic field values, and then the magnetic field values are updated and stored in memory using the electric field values just calculated.

#### Chapter 3

#### **FPGA-Based Reconfigurable Computing Systems**

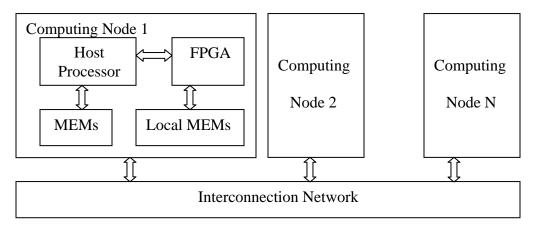

A reconfigurable computing system consists of a number of computing nodes connected by an interconnection network. Host processors and reconfigurable computing elements (FPGAs and CPLDs) are associated with some or all of the computing nodes. The general diagram of a reconfigurable computing system is depicted in figure 3-1:

Figure 3-1 : Reconfigurable Computing System

In a reconfigurable computing system, a host application runs on one or several host processors, and some tasks in the host application are assigned to the FPGAs. The host processors and the FPGAs cooperate to execute the host application. Reconfigurable computing system is a good choice for host applications with intensive computation and parallelism.

In this thesis, FDTD algorithm is implemented in two reconfigurable computing systems: the Prototype system in the ACL Lab at University of Cincinnati and the Cray XD1 system. The Cray XD1 system has higher bandwidth, lower latency and more powerful memory architecture than the Prototype system.

## 3.1 Laboratory Prototype System

#### 3.1.1 System Architecture

The Prototype system is an integration of a PC with a reconfigurable computing board inserted into one of its PCI slots. This system is built for reconfigurable computing research. The specification for the PC is:

- Intel<sup>®</sup> Xeon<sup>TM</sup> CPU 1.70 GHz

- 512 MB of RAM

- 28 GB IDE disk

- 3Com® Fast Ethernet Controller

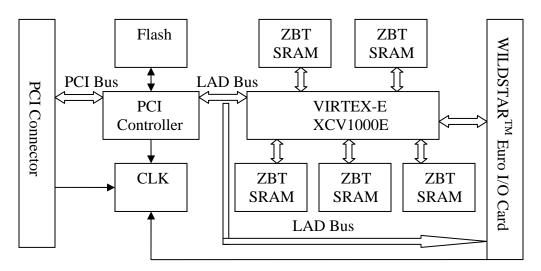

The reconfigurable computing board in the Prototype system is an Annapolis Micro FIREBIRD<sup>TM</sup>/PCI board. The FIREBIRD<sup>TM</sup>/PCI features include [24]:

- one Processing Element PE0 that is a Xilinx VIRTEX-E FPGA

- PE0 can optionally be programmed from flash on power up

- Processing clocks up to 150MHz

- Five memory banks, containing 9 to 36 Mbytes of synchronous ZBT SRAM

- 5.4Gbytes/sec of memory bandwidth

- 66MHz/64bit PCI transactions (3.3V PCI signaling only)

The block diagram for the FIREBIRD<sup>TM</sup>/PCI board is depicted in figure 3-2.

The local address data (LAD) bus in figure 3-2 is a single master, 64-bit, shared

address/data bus used for communications between the FPGA and the host processor.

Every cycle on the LAD bus is initiated by the PCI Controller.

The user's design in the FPGA communicates with the host processor via the LAD bus. Any memory reads/writes by the host also go through the LAD bus and the FPGA. The FPGA directly accesses the ZBT SRAM.

*Figure 3-2 : FIREBIRD<sup>TM</sup>/PCI block diagram* [24]

## 3.1.2 Simulation Environment

The simulation environment includes VHDL models for the host system and the FIREBIRD<sup>TM</sup>/PCI board. These VHDL models are provided by Annapolis Micro Systems, Inc. to give the designer an accurate test bed for the completed Processing Element (PE) design and to enable the designer to validate the PE design before the synthesis, placement, and routing steps [24].

The VHDL model for the host system is used to access the PE resources of the FIREBIRD<sup>TM</sup>/PCI board via the PCI Controller. It can also be used to initialize and analyze the contents of any memory device on the FIREBIRD<sup>TM</sup>/PCI board. This VHDL model is similar to the actual host system and it provides VHDL functions similar to the actual software Application Programming Interface (API) functions.

The VHDL model for the host system includes the following functions [24]:

- WS\_Open : Sets up initial board configuration

- WS\_ReadPeReg/WS\_WritePeReg: Reads/writes register locations in the PE Register Space

- WS\_ReadPeReg64/WS\_WritePeReg64: Reads/writes register locations in the PE Register Space

- WS\_DMARead/WS\_DMAWrite: Reads/writes the PE Space using DMA

- WS\_MClkSetConfig/WS\_UClkSetConfig: Sets the configuration of the memory and PE/user clocks

- WS\_WaitOnInterrupt : Waits for PE interrupt signal

- WS\_QueryInterruptStatus : Returns current interrupt status of all PEs

- WS\_ResetInterrupt : Clears pending interrupts

The VHDL model for the FIREBIRD<sup>TM</sup>/PCI board includes [24]:

- PCI Controller Model

- On-board Memory Model

- I/O Card Model

The PCI controller model provides functions to handle LAD bus transactions, to configure the clocks, and to handle PE interrupts. These functions can all be accessed from the functions provided by the VHDL model for the host system.

The on-board memory model is used to inspect the memory contents from the VHDL simulator tool. This model can be configured to an "empty" architecture if no memories on the board are needed by the PE.

The I/O card model is empty. This model tri-states all of its signals to the FIREBIRD<sup>TM</sup>/PCI board.

#### **3.1.3 Host Programming Environment**

The Host Programming environment consists of three layers [25]:

- User's host application

- WILDSTAR<sup>TM</sup> Application Programming Interface (API)

- WILDSTAR<sup>TM</sup> Device Driver

User's host application is programmed with 'C' language and runs on the host PC. Its essential function is to load the embedded PE application (provided as an FPGA binary file) into the PE on the FIREBIRD<sup>TM</sup>/PCI board and to maintain the operating environment of the embedded PE application.

The overall host application is bound by the WILDSTAR<sup>™</sup> API. To develop host application, at least one library and several include files must be included. Under Windows<sup>®</sup> NT<sup>™</sup> and UNIX, a single library--the WILDSTAR<sup>™</sup> API is included. The include files contain constants, data types, and prototypes necessary to interface to the WILDSTAR<sup>™</sup> API.

The WILDSTAR<sup>™</sup> API centralizes specific knowledge of the underlying system. It presents a generalized view of the hardware resources and control operations in the system.

The WILDSTAR<sup>™</sup> API routines are organized to provide high-level operations by performing combinations of low-level WILDSTAR<sup>™</sup> device driver functions. The routines are provided to accomplish clock control, PE control, register interfaces

17

read/write, DMA Operations, Interrupt Operations, Temperature/Power Monitoring Operations, LED Display Operations. The subset of the API functions available to the host application programmer and used for the work presented in this thesis is [25]:

- WS\_Open : Open a FIREBIRD<sup>TM</sup>/PCI board

- WS\_Close : Close a FIREBIRD<sup>TM</sup>/PCI board

- WS\_GetPhysicalConfig : Get the configuration information from the ID PROM(s)

- WS\_ProgramPe : Program a particular PE

- WS\_DeProgramPe : Deprogram a particular PE

- WS\_MClkSetConfig : Set the source and frequency for M clock

- WS\_UClkSetConfig : Set the source and frequency for P clock

- WS\_ReadPeReg : Read from PE register space

- WS\_WritePeReg : Write to PE register space

- WS\_DmaRead : Read a buffer using DMA

- WS\_DmaWrite : Write a buffer using DMA

- WS\_ResetInterrupt : Reset the specified interrupt sources on the board

- WS\_QueryInterruptStatus : Check the status of pending interrupts on the board

The WILDSTAR<sup>TM</sup> device driver provides a low-level interface to the

FIREBIRD<sup>TM</sup>/PCI board's register space and a central location for all of the system's global resources. It performs all necessary steps to initialize, to access and to maintain the hardware.

#### 3.2 Cray XD1 System

#### 3.2.1 System Architecture

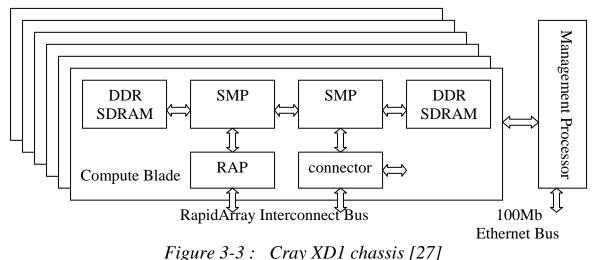

The Cray XD1 system is designed specifically for high performance computing. It consists of many Cray XD1 chassis interconnected with one high-speed switch fabric called the RapidArray Interconnect.

# 3.2.1.1 Cray XD1 Chassis

The Cray XD1 chassis contains a management processor and six compute blades.

Each compute blade includes the following components [27]:

- Two 64-bit AMD Opteron processors—configured as one two-way symmetric multiprocessors (SMP) that runs Linux operating system.

- Up to 16GB of DDR SDRAM per SMP

- one RapidArray processor (RAP)—provide high-bandwidth, low-latency interface to the RapidArray Interconnect

- A connector for an expansion module

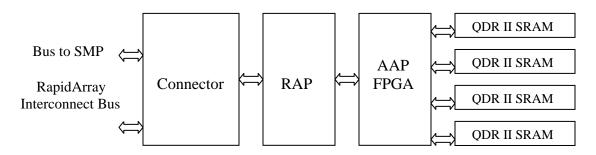

The expansion module is an optional board that attaches to a compute blade. Each expansion module contains the following components [27]:

- An application acceleration processor (AAP FPGA)

- An RAP which provides two additional RapidArray links per compute blade

- Four quad-data-rate (QDR) II SRAMs for the AAP FPGA

- A programmable clock source for the AAP FPGA

The block diagram for the expansion module is as follows [27]:

*Figure 3-4 : Expansion Module [27]*

The AAP FPGA belongs to the Xilinx Virtex-II Pro series. The resources in the AAP FPGA include 2 PowerPC processor blocks, 23616 logic slices, 232 18×18 bit multiplier blocks, 232 18 Kb Block RAMs.

The RAP connects the AAP FPGA to the local SMP and the RapidArray Interconnect. The QDR II SRAM provides local high-speed storage for the AAP FPGA. Each of the four QDR II SRAM circuits operates independently. The programmable clock sets the speed of the AAP FPGA for each design.

#### 3.2.1.2 RapidArray Interconnect

The RapidArray Interconnect is a central communications construct in the Cray XD1 system. It connects processors and memories within a chassis and between chassis. This interconnect enables the system to avoid PCI-X bus bottlenecks and shared-resource contention.

"The RapidArray Interconnect is a 96-GB-per-second (maximum per chassis) nonblocking, embedded crossbar-switch fabric that connects the RAPs. Each chassis has either one or two RapidArray switch fabrics, each of which consists of RapidArray links and a 24-port internal switch." [27]

#### 3.2.2 Simulation Environment

The elements in the simulation environment are [31]:

- A VHDL test bench

- VHDL model for the RapidArray fabric

- VHDL model for the QDR II SRAM

- The stimulus file

The test bench instantiates the AAP FPGA, the fabric model and the QDR II SRAM model.

In the simulation, the fabric model processes commands such as read request and write request from a stimulus file. It will also process read and write requests generated by the AAP FPGA.

The QDR II SRAM model simulates a dual-port, 36-bit wide QDR II SRAM. This SRAM is synchronous and can be read and written at the same time.

The stimulus file is a text file containing stimulus commands which are inputs to the fabric model. The commands includes: [31]

- I: Initialize Link

- P <Text to print>: display messages on the simulation console

- D <delay value> : insert a time delay between requests

- R <addr> <expected data> <byte mask> <byte request> <size> : Read Request

- W <addr> <write data> <byte mask> <byte request> <size> : Write Request

- B <data> <byte mask> : Burst Request

where:

<Text to print> = Message for console <delay value> = delay in user clock cycles <addr> = 40 bits address in hex <data> = 64 bits data in hex <byte mask> = 8 bits data mask in hex (1 = enable, 0 = disable) <byte request> = 4 bits in hex (1 = byte req, 0 = dw request) <size> = size of read/write access in double words (32 bits) in hex

## 3.2.3 Host Programming Environment

The Host Programming environment consists of three layers [28]:

- host application on the SMP

- FPGA Application Programming Interface (API)

- RT core bus transactions

To communicate with the AAP FPGA, the host application first opens the AAP FPGA to get a file descriptor. Then using the file descriptor, the host application loads the converted logic file (provided as an FPGA binary file) into the AAP FPGA. After this, the host application can read and write registers in the AAP FPGA, read data from or write data to the QDR II SRAMs through the AAP FPGA. At last, the host application can reset the AAP FPGA and close the file descriptor.

The FPGA API provides the functions that the host application needs to use an AAP FPGA. These functions include [28]:

- fpga\_open : Opening an FPGA

- fpga\_load : Loading the converted logic file into the FPGA

- fpga\_reset : Resetting an FPGA

- fpga\_start : Releasing an FPGA from reset state

- fpga\_memmap : Accessing FPGA locations from the host application

- fpga\_mem\_sync : Synchronizing accesses to FPGA locations

- fpga\_wrt\_appif\_val : Writing individual FPGA locations

- fpga\_rd\_appif\_val : Reading individual FPGA locations

- fpga\_set\_ftrmem : Accessing host application memory from an FPGA

- fpga\_status : Checking the status of an FPGA

- fpga\_is\_loaded : Checking the programming state of an FPGA

- fpga\_unload : Erasing an FPGA

- fpga\_close : Closing an FPGA

There is a component referred to as the Rt\_core (see 4.3.1.4) in the AAP FPGA. The FPGA API functions initiate appropriate RT core bus transactions to this component. The user logic in the AAP FPGA processes the bus transactions and responds appropriately. If user logic in the AAP FPGA needs to access the SMP memory through Rt\_core, it sends a bus transaction to Rt\_core, then the bus transaction is forwarded to hardware on the SMP, where it becomes a read or write transaction to the SMP DRAM.

#### Chapter 4

#### FDTD FPGA Implementation using Local SRAM

FPGA implementation of the FDTD algorithm has been done for each of the systems described in the previous chapter: the Prototype system and the Cray XD1 system. The design goal in the Prototype system is to explore implementation feasibility, while the goal in the Cray XD1 system is to improve implementation performance.

In both systems, floating point units are used to implement the update engines and the update engines are pipelined, input and output data for the FDTD algorithm are stored in the local SRAMs to reduce the data transfer between the host system and the FPGA.

In the Prototype system, the two magnetic update engines are processed serially, each SRAM is single-port with random delay, and only one iteration of FDTD algorithm calculation can be supported. While in the Cray XD1 system, the two magnetic update engines are processed in parallel, each SRAM is dual-port with fixed delay, the data in the SRAMs in the Cray XD1 system are organized as ping-pong buffers, and specified number of iterations of FDTD algorithm calculation can be supported. So the design in the Cray XD1 system has higher throughput, higher memory access speed, and less data flow between the host system and the FPGA.

The FPGA implementation flow in the Prototype system is almost the same as that in the Cray XD1 system. But the detailed steps are different in these two systems. In this thesis, the FPGA implementation flow and the detailed steps in the flow are explained for both systems.

#### 4.1 FPGA Implementation Flow

The FPGA implementation flow in this thesis has the following five basic steps:

- VHDL Design—Create VHDL source code for the target FPGA

- Simulation—Simulate the VHDL source code

- Synthesis—Translate the VHDL source code into a gate-level netlist

- P&R—Place and route the gate-level netlist on the target FPGA

- Host Programming—Program host application, C/C++ with API calls

The FPGA implementation flow is depicted in figure 4-1:

Figure 4-1 : FPGA Implementation Flow

VHDL can specify a hardware design in terms of familiar programming constructs such as conditional statements, loops, and function calls. It provides a flexible and powerful way to generate efficient logic. VHDL code can be written with many text editors. The target FPGA in the Prototype system is the Processing Element PE0 located on the FIREBIRD<sup>TM</sup>/PCI board (see 3.1.1), and the target FPGA in the Cray XD1 system is AAP FPGA located on the expansion module board (see 3.2.1.1).

The simulation is done in the simulation environment described in chapter 3 (see 3.1.2 and 3.2.2). In the simulation, VHDL source code and the VHDL models provided in the simulation environment that manipulate the design inputs and monitor the outputs are combined and compiled by the simulation tool. Then the simulation process starts, waveforms for all the signals in the VHDL source code and the VHDL models are derived, checked and verified. The simulation tool used is ModelSim VHDL simulator.

The synthesis process translates the VHDL source code into gate-level elements such as AND gates, OR gates, and flip-flops. The output of the synthesis process is a gate-level netlist. In the Prototype system, the synthesis tool used is Synplify Pro. In the XD1 Cray system, the synthesis tool used is Xilinx XST.

P&R is the process of translating, mapping, placing, routing, and generating an FPGA binary file for the VHDL source code. It assigns logic in the gate-level netlist to specific physical resources of the target FPGA. A set of user-determined timing and placement constraints guides the P&R process. These constraints are in the user constraint file (UCF). The target FPGA type is Xilinx VIRTEX-E XCV1000E in the Prototype system and Xilinx Virtex-II Pro XC2VP50 in the Cray XD1 system. The P&R tool used is part of the Xilinx ISE design suite.

The host application is programmed using the APIs provided in the host programming environment described in chapter 3 (see 3.1.3 and 3.2.3). It loads the FPGA binary file to the target FPGA and debugs the operation of the FPGA.

27

## 4.2 FPGA Implementation in the ACL Prototype System

#### 4.2.1 VHDL Design

In this section, the function of the VHDL source code for the FPGA is explained and the FPGA architecture for the VHDL source code is drawn. Next data organization in local memories is explained. At last components and processes in the VHDL source code are described in detail.

### 4.2.1.1 FPGA Function

The FPGA can be used as a bridge to take data from the host system and to write it to local memories, to read data from local memories and to write it to the host system. It can also be used as FDTD algorithm update engines.

If the FPGA is used as a bridge, configuration data should be written into internal registers in the FPGA first. The configuration data indicates the local memories access type (read or write), the start address of the accessed local memories and the length of the data. Then data transfer between the host system and the local memories starts. Data are transferred through the FPGA in DMA mode.

If the FPGA is used as FDTD algorithm update engines, it can only complete one iteration of FDTD algorithm calculation. The host system must write input data to the local memories before each iteration of calculation and read output data back from the local memories after each iteration of calculation. The FPGA can be configured to operate in two modes: UpdateHxHy mode and UpdateEz mode. In UpdateHxHy mode, update engine magnetic update Hx and magnetic update Hy are enabled to execute one iteration of calculation. In UpdateEz mode, update engine electric update is enabled to execute one iteration of calculation.

The operation sequence in UpdateHxHy mode is as follows:

- Hx<sub>t-1</sub> values are read from local memory MEM0; Hy<sub>t-1</sub> values are read from local memory MEM1; Ez values are read from local memory MEM2. These read operations are done in parallel

- Hx<sub>t-1</sub> values, Hy<sub>t-1</sub> values, Ez values are fed to internal FIFOs in the FPGA in parallel

- Hx<sub>t-1</sub> values, and Ez values in internal FIFOs are fed to the enabled update engine magnetic update Hx; Hy<sub>t-1</sub> values, and Ez values in internal FIFOs are fed to the enabled update engine magnetic update Hy.

- 4) When the result data Hxt values and Hyt values from update engine magnetic update Hx and magnetic update Hy are ready, they are pushed into another two FIFOs in the FPGA

- 5) Hxt values are pulled out of the FIFO and written to local memory MEM3, Hyt values are pulled out of the FIFO and written to local memory MEM4.

Similarly, the operation sequence in UpdateEz mode is as follows:

- Hx values are read from local memory MEM0; Hy values are read from local memory MEM1; Ez<sub>t-1</sub> values are read from local memory MEM2. These read operations are done in parallel

- Hx values, Hy values and Ez<sub>t-1</sub> values are fed to internal FIFOs in the FPGA in parallel

- Hx values, Hy values and Ez<sub>t-1</sub> values in internal FIFOs are fed to the enabled update engine electric update

- When the result data Ez<sub>t</sub> values from update engine electric update are ready, they are pushed into another FIFO in the FPGA

- 5) Ezt values are pulled out of the FIFO and written to local memory MEM3

#### 4.2.1.2 FPGA Architecture

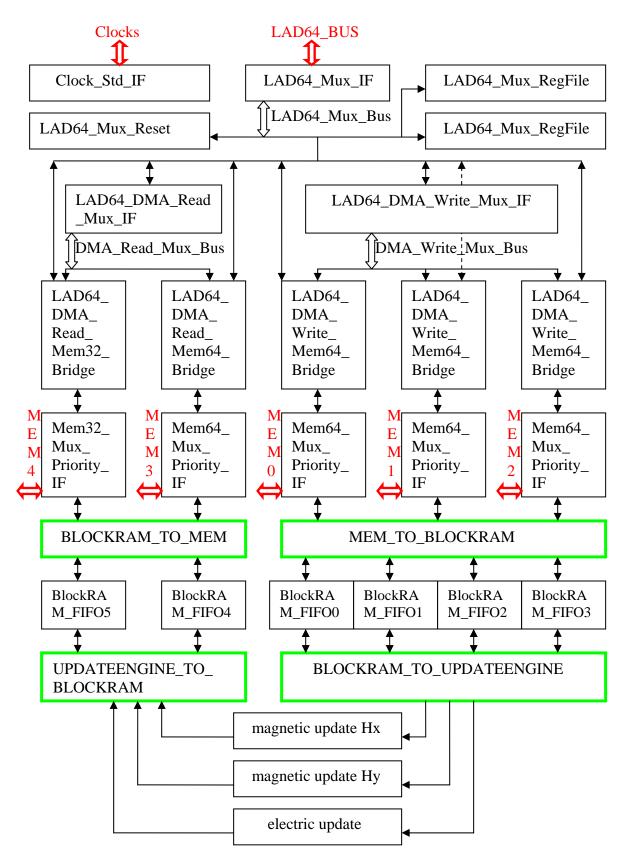

FPGA architecture is drawn in Figure 4-2. Definitions for the symbols used in figure 4-2 are:

external interface

internal bus

internal signal

component in the VHDL source code

process in the VHDL source code

In the FPGA architecture, components with prefix "LAD" are related to the LAD bus. The host system communicates with the FPGA through these components. With the aid of these components, the host system can access internal registers in the FPGA and the local memories.

The memory interface in the FPGA consists of components with prefix "Mem". This memory interface multiplexes the read/write requests from the host system and the update engines in the FPGA. The host system and the update engines can't access the same memory at the same time.

Figure 4-2 : FPGA Architecture in the Prototype System

Three update engines are used for FDTD algorithm calculation. Four processes are used for the update engines to access the local memories.

Because the local memories have random delay, internal FIFOs are used when the update engines access the local memories. This increases the complexity and decreases the performance of the FPGA design.

#### **4.2.1.3 Data Organization in Local Memories**

There are five independent local memories on the FIREBIRD<sup>TM</sup>/PCI board (see 3.1.1). MEM0 to MEM3 are 64-bit wide, MEM4 is 32-bit wide. MEM0 to MEM2 are used to store source data, MEM3 to MEM4 are used to store destination data. In detail, MEM0 stores  $Hx_{t-1}$  values, MEM1 stores  $Hy_{t-1}$  values, MEM2 stores  $Ez_{t-1}$  values, MEM3 stores  $Hx_t$  values or  $Ez_t$  values, MEM4 stores  $Hy_t$  values.

Assume the electromagnetic field processed by the FPGA is a Grid\_Row×Grid\_Column matrix. Then Hx values, Hy values and Ez values in this matrix can be organized as two-dimensional data arrays. The range for Hx values is from Hx[0][0] to Hx[Grid\_Row–1][ Grid\_Column–1], the range for Hy values is from Hy[0][0] to Hy[Grid\_Row–1][ Grid\_Column–1], the range for Ez values is from Ez[0][0] to Ez[Grid\_Row–1][ Grid\_Column–1].

$Hx_{t-1}[i][j]$  in the electromagnetic field matrix is stored in MEM0 at address i×Grid\_Column+j, Hy<sub>t-1</sub>[i][j] is stored in MEM1 at address i×Grid\_Column+j, Ez<sub>t-1</sub>[i][j] is stored in MEM2 at address (i–1)×Grid\_Column+(j–1), Hx<sub>t</sub>[i][j] is stored in MEM3 at address i×Grid\_Column+j, Hy<sub>t</sub>[i][j] is stored in MEM4 at address i×Grid\_Column+j, Ez<sub>t</sub>[i][j] is stored in MEM3 at address (i–1)×Grid\_Column+(j–1).

### 4.2.1.4 Components and Processes

Components in the FPGA architecture can be divided into four groups:

- update engines

- components related to LAD bus

- components related to memory interface

- internal FIFO

Processes in the FPGA architecture include:

- MEM\_TO\_BLOCKRAM

- BLOCKRAM\_TO\_UPDATEENGINE

- UPDATEENGINE\_TO\_BLOCKRAM

- BLOCKRAM\_TO\_MEM

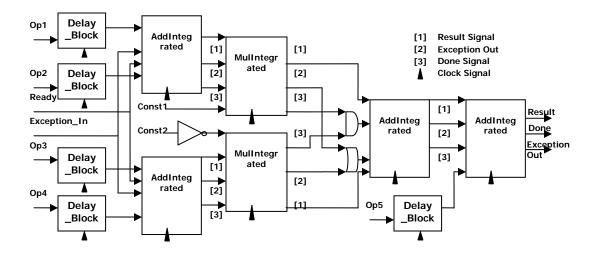

There are three update engines in the FPGA. They are used to update magnetic field and electric field values. To improve speed, these update engines are fully pipelined.

• magnetic update Hx : updates magnetic field values along the x-coordinate. It

implements the following equation:

$$Hx_{t}[i][j] = Hx_{t-1}[i][j] - dtmudy \times (Ez[i+1][j+1] - Ez[i+1][j])$$

(3a)

This equation is transformation of equation (2a) in the FDTD algorithm in chapter 2.

$Hx_t$ : the magnetic field value along the x-coordinate  $Hx_{t-1}$ : the magnetic field value along the x-coordinate from the previous time step Ez: the electric field value along the z-coordinate

dtmudy : constant that includes time step, grid spacing, and magnetic permeability

• magnetic update Hy : updates magnetic field values along the y-coordinate. It

implements the following equation:

$$Hy_{t}[i][j] = Hy_{t-1}[i][j] + dtmudx \times (Ez[i+1][j+1] - Ez[i][j+1])$$

(3b)

This equation is transformation of equation (2b) in the FDTD algorithm in chapter 2.

• *electric update* : updates electric field values along the z-coordinate. It implements the following equation:

$$Ez_{t}[i][j] = Ez_{t-1}[i][j] + dtepsdx \times (Hy[i][j-1] - Hy[i-1][j-1]) - dtepsdy \times (Hx[i-1][j] - Hx[i-1][j-1])$$

(3c)

Figure 4-5 Block Diagram of Electric update [21]

The FPGA communicates with the host system through the LAD bus. Components related to LAD bus in the FPGA include [24]:

LAD64\_Mux\_IF : connects internal components in PE0 to the PCI Controller on the FIREBIRD<sup>TM</sup>/PCI board. It has master port LAD64\_BUS and clients port LAD64\_Mux\_Bus. LAD64\_BUS is a local address data (LAD) bus. It is a single master, 64-bit, shared address/data bus. Every cycle on it is initiated by the PCI Controller and may last from four to hundreds of clock cycles. LAD64\_Mux\_Bus is clients bus, the internal components in PE0 such as LAD64\_Mux\_Reset and LAD64\_Mux\_RegFile are connected to it

• *LAD64\_Mux\_Reset* : provides an LAD accessible reset unit for PE0. It encapsulates a VIRTEX\_STARTUP block. When the host application writes a '1' to its control address, it will generate a reset pulse on the global reset line of PE0

• *LAD64\_Mux\_RegFile* : provides an LAD accessible register file on PE0. Each register in the file is 64-bits. Configuration data such as version number and update type are written into the register file in this component

• LAD64\_DMA\_Read\_Mux\_IF : used with component

LAD64\_DMA\_Read\_Mem64\_Bridge and LAD64\_DMA\_Read\_Mem32\_Bridge to read data from the local memory on the FIREBIRD<sup>TM</sup>/PCI board. It receives DMA data from LAD64\_DMA\_Read\_Mem64\_Bridge and LAD64\_DMA\_Read\_Mem32\_Bridge and transmits the received DMA data on the LAD bus which is connected to the host system. It also controls the DMA read status

• LAD64\_DMA\_Write\_Mux\_IF : used with component

LAD64\_DMA\_Write\_Mem64\_Bridge to write data to the local memory. It receives data from the LAD bus which is connected to the host system, then it transmits the received data on DMA bus which is connected to LAD64\_DMA\_Write\_Mem64\_Bridge. It also controls the DMA write status

• LAD64\_DMA\_Read\_Mem64\_Bridge : acts as a pre-fetch unit for the

LAD64\_DMA\_Read\_Mux\_IF. It reads data from the 64-bit Mem bus which is connected to the Mem64\_Mux\_Priority\_IF and transmits the received data to the DMA bus which is connected to the LAD64\_DMA\_Read\_Mux\_IF. It has ports LAD, Mem and DMA. Port LAD is connected to the LAD64\_Mux\_IF and receives control data from the host system. LAD64\_DMA\_Read\_Mem64\_Bridge contains a register file CRegfile which is used to control the start and stop memory addresses. It also contains a status record which can be used to determine if a DMA read is being performed and what percentage of the DMA read has been completed

• LAD64\_DMA\_Read\_Mem32\_Bridge : acts as a pre-fetch unit for the

LAD64\_DMA\_Read\_Mux\_IF. It reads data from the 32-bit Mem bus which is connected to the Mem32\_Mux\_Priority\_IF and transmits the received data to the DMA bus which is connected to the LAD64\_DMA\_Read\_Mux\_IF. It has ports LAD, Mem and DMA. Port LAD is connected to the LAD64\_Mux\_IF and receives control data from the host system. LAD64\_DMA\_Read\_Mem32\_Bridge contains a register file CRegfile which is used to control the start and stop memory addresses. It also contains a status record which can be used to determine if a DMA read is being performed and what percentage of the DMA read has been completed

• *LAD64\_DMA\_Write\_Mem64\_Bridge* : used with LAD64\_DMA\_Write\_Mux\_IF to take data from the host system and write it to the 64-bit local memory. It reads data from DMA bus connected to LAD64\_DMA\_Write\_Mux\_IF and transmits the received data to the Mem bus connected to Mem64\_Mux\_Priority\_IF. It has ports LAD, Mem and DMA. Port LAD is connected to the LAD64\_Mux\_IF and receives control data from the host system. LAD64\_DMA\_Write\_Mem64\_Bridge contains a register file CRegfile which is used to control the start and stop memory addresses. It also contains a status record which can be used to determine if a DMA write is being performed and what percentage of the DMA write has been completed

The FPGA accesses the local memories through a 64-bit Memory Standard Interface and a 32-bit Memory Standard Interface. Components related to these memory interfaces in the FPGA include [24]:

• *Mem64\_Mux\_Priority\_IF* : a 64-bit memory server in the PE0. It multiplexes memory ports among different components that are clients contained in the PE0 and is

capable of providing 64-bit memory access to these clients. For example, for the local memory MEM0 in figure 4-2, Mem64\_Mux\_Priority\_IF provides memory access to clients LAD64\_DMA\_Write\_Mem64\_Bridge and MEM\_TO\_BLOCKRAM. Each client must be assigned a unique element of the client vector in order to be connected to the 64-bit memory server

• *Mem32\_Mux\_Priority\_IF* : a 32-bit memory server in the PE0. It multiplexes memory ports among different components that are clients contained in the PE0 and is capable of providing 32-bit memory access to these clients

Internal FIFO used in the FPGA is component *BlockRAM\_FIFO*. This is a 256x32 FIFO. 32-bit data can be pushed into it and pulled out of it. If the FIFO is almost full, Full Flag is set. If the FIFO is almost empty, then Empty Flag is set.

There are four processes in the FPGA. These processes control the memory access of the update engines.

• *MEM\_TO\_BLOCKRAM* : reads data from three 64-bit local memories (MEM0 to MEM2) and feeds the data to four BLOCKRAM\_FIFOs (BLOCKRAM\_FIFO0 to BLOCKRAM\_FIFO3). Local memory MEM0 is connected to BLOCKRAM\_FIFO0, Local memory MEM1 is connected to BLOCKRAM\_FIFO1, Local memory MEM2 is connected to BLOCKRAM\_FIFO2 and BLOCKRAM\_FIFO3. If PE0 is in UpdateHxHy mode or UpdateEz mode and the four BLOCKRAM\_FIFOs have spare space, read requests are issued to the three local memories. When the output data from the three local memories are ready, they are pushed into the four BLOCKRAM\_FIFOs. If PE0 is in UpdateHxHy mode, the pseudo-code to generate read addresses to the three local memories is:

for update engine magnetic update Hx:

for i from 0 to Grid\_Row-1

for j from 1 to Grid\_Column-1

| generate read address | i×Grid_Column +j –1             | for MEM0 |

|-----------------------|---------------------------------|----------|

| generate read address | $i \times Grid\_Column + j - 1$ | for MEM2 |

| generate read address | i×Grid_Column +j                | for MEM2 |

for update engine magnetic update Hy:

for i from 1 to Grid\_Row-1

for j from 0 to Grid\_Column-1

| generate read address | $(i-1) \times Grid\_Column + j$ | for MEM1 |

|-----------------------|---------------------------------|----------|

| generate read address | $(i-1) \times Grid\_Column + j$ | for MEM2 |

| generate read address | i×Grid_Column +j                | for MEM2 |

If PE0 is in UpdateEz mode, the pseudo-code to generate read addresses to the three local memories is:

for update engine electric update

for i from 1 to Grid\_Row-1

for j from 1 to Grid\_Column-1

| generate read address | $(i-1) \times Grid\_Column + j - 1$ | for MEM0 |

|-----------------------|-------------------------------------|----------|

| generate read address | $(i-1) \times Grid\_Column + j$     | for MEM0 |

| generate read address | $(i-1) \times Grid\_Column + j - 1$ | for MEM1 |

| generate read address | $i \times Grid\_Column + j - 1$     | for MEM1 |

| generate read address | $(i-1) \times Grid\_Column + j - 1$ | for MEM2 |

• *BLOCKRAM\_TO\_UPDATEENGINE* : reads data from four BLOCKRAM\_FIFOs (BLOCKRAM\_FIFO0 to BLOCKRAM\_FIFO3) and feed the data to update engines. It monitors the status of the four BLOCKRAM\_FIFOs and read data from them. Then it enables update engines magnetic update Hx and magnetic update Hy and feeds data to them if PE0 is in UpdateHxHy mode or enables update engine electric update and feeds data to it if PE0 is in UpdateEz mode.

• UPDATEENGINE\_TO\_BLOCKRAM : reads data from update engines and writes it to BlockRAM\_FIFOs (BLOCKRAM\_FIFO4 to BLOCKRAM\_FIFO5). If PE0 is in UpdateHxHy mode, result of update engine magnetic update Hx is pushed to BlockRAM\_FIFO4 and result of update engine magnetic update Hy is pushed to BlockRAM\_FIFO5. If PE0 is in UpdateEz mode, result of update engine electric update is pushed to BlockRAM\_FIFO4.

• *BLOCKRAM\_TO\_MEM* : reads data from BlockRAM\_FIFOs (BLOCKRAM\_FIFO4 to BLOCKRAM\_FIFO5) and writes the data into two local memories (MEM3, MEM4). If PE0 is in UpdateHxHy mode, data from BLOCKRAM\_FIFO4 is written to MEM3 and data from BLOCKRAM\_FIFO5 is written to MEM4. If PE0 is in UpdateEz mode, data from BLOCKRAM\_FIFO4 is written to MEM3. If PE0 is in UpdateHxHy mode, the pseudo-code to generate write addresses to the two local memories is:

for i from 0 to Grid\_Row-1

for j from 1 to Grid\_Column–1

generate write address  $i \times Grid\_Column + j - 1$  for MEM3

for i from 1 to Grid\_Row-1

for j from 0 to Grid\_Column-1

generate write address  $(i - 1) \times Grid\_Column + j$  for MEM4

If PE0 is in UpdateEz mode, the pseudo-code to generate write addresses to the three local memories is:

for i from 1 to Grid\_Row–1 for j from 1 to Grid\_Column–1 generate write address  $(i - 1) \times \text{Grid}_\text{Column} + j - 1$  for MEM3

## 4.2.2 Simulation

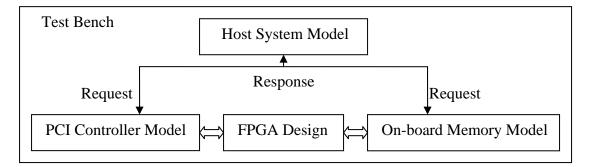

The simulation is done in the simulation environment described in chapter 3 (see 3.1.2). The test bench includes and instantiates the FPGA, VHDL model for the host system and the FIREBIRD<sup>TM</sup>/PCI board. The operation sequence in the test bench is the same as the operation sequence in the host application described in 4.2.5.

Structure of the test bench is depicted in figure 4-6.

Figure 4-6 Structure of the Test Bench in the Prototype System

## 4.2.3 Synthesis

The VHDL source code for the FPGA is synthesized with Synplify Pro. The output of synthesis is an EDIF file.

#### 4.2.4 P&R

The EDIF file is placed and routed on the target FPGA Xilinx VIRTEX-E XCV1000E. The output file is a FPGA binary file for the VHDL source code.

### 4.2.5 Host Programming

The host application is programmed with 'C' language in the host programming environment described in chapter 3 (see 3.1.3). In order to interact with PE0, it calls WILDSTAR<sup>™</sup> API functions.

The operation sequence in the host application is as follows:

- 1) Open the FIREBIRD<sup>TM</sup>/PCI board and check configuration information

- 2) Configure the clocks on the board

- 3) Download FPGA binary file into XCV1000E

- 4) Reset FPGA, update engines and interrupt signal

- 5) Write  $Hx_{t-1}$  values in DMA mode to local memory MEM0

- 6) Write  $Hy_{t-1}$  values in DMA mode to local memory MEM1

- 7) Write Ez values in DMA mode to local memory MEM2

- 8) Enable update engines magnetic update Hx and magnetic update Hy

- 9) Check interrupt signal. If interrupt signal is set, the update process ends

- 10) Read Hxt values in DMA mode from local memory MEM3

- 11) Read Hy<sub>t</sub> values in DMA mode from local memory MEM3

- 12) Write Hx values in DMA mode to local memory MEM0

- 13) Write Hy values in DMA mode to local memory MEM1

- 14) Write Ez<sub>t-1</sub> values in DMA mode to local memory MEM2

15) Enable update engines electric update

16) Check interrupt signal. If interrupt signal is set, the update process ends

17) Read Ez<sub>t</sub> values in DMA mode from local memory MEM3

- 18) Unload FPGA binary file from XCV1000E

- 19) Close the FIREBIRD<sup>TM</sup>/PCI board

The Prototype System is very simple. There are only one host processor and one FPGA in the system. So thread-level parallelism in the FDTD algorithm can't be exploited. Local SRAMs attached to the FPGA are single-port with random delay and low speed. These low-performance SRAMs can't support parallelism among the update engines and can only support one iteration of FDTD algorithm calculation.

#### **4.3 FPGA Implementation in the Cray XD1 System**

In order to overcome the limitations of the Prototype System and to improve the performance, the FPGA implementation is done in another reconfigurable system named Cray XD1 System. In the Cray XD1 system, there are lots of host processors and FPGAs. The FDTD algorithm can be partitioned and distributed to the host processors and the FPGAs, thus thread-level parallelism can be exploited. Furthermore, local SRAMs in the Cray XD1 system are dual-port with fixed delay and high speed. These SRAMs can support parallelism among the update engines and specified number of iterations of FDTD algorithm calculation. So performance of the FPGA design in the Cray XD1 system improves greatly compared with that in the Prototype system.

#### 4.3.1 VHDL Design

In the Cray XD1 system, the FPGA which is referred to as the AAP FPGA is located on the expansion module board (see 3.2.1.1). In this section, the function of the VHDL source code for the FPGA is explained and the FPGA architecture for the VHDL source code is drawn. Then data organization in local memories is explained. At last components and processes in the VHDL source code are described in detail.

#### **4.3.1.1 FPGA Function**

The FPGA can be used as a bridge to take data from the host system and to write it to local memories, to read data from local memories and to write it to the host system. It can also be used for the FDTD algorithm update engines.

If the FPGA is used as a bridge, local memories QDR II SRAM 1 to QDR II SRAM 4 are mapped to the address space of the host system. Read commands from this address space and write commands to this address space will be delivered to the FPGA. The FPGA then reads data from the local memories and forwards them to the host system or write the received data to the local memories.

If the FPGA is used for the FDTD algorithm update engines, it must be initialized first. The initialization data are stored in two internal registers FPGA\_reg and Update\_counter. These registers are described in 4.3.1.4. After configuration the FPGA will execute specified number of iterations of FDTD algorithm calculation. Throughout this thesis, "one iteration of FDTD algorithm calculation" means magnetic field values update by magnetic update Hx and magnetic update Hy at one time step, or electric field update by electric update at one time step. The exact operation sequence is described in 4.3.1.4 (see component Qdr\_fdtd in 4.3.1.4).

## 4.3.1.2 FPGA Architecture

Fabric

User

Request

Interface

Request

Interface

Transmit

Data Bus

Receive

Data Bus

Processor

Interface

Clock

Signals

Rt

core

Host

QDR 1

ODR 2

QDR 3

QDR 4

Interface

Interface

Mux

Interface

Interface

QDR II SRAM 1

ODR II SRAM 2

ODR II SRAM 3

QDR II SRAM 4

nterface

nterface

nterface

Qdr2

core

App\_fdtd

FPGA architecture which supports both memory bridge and FDTD operation is

Definitions for the symbols in figure 4-7 are as follows:

Rt\_client

Qdr\_fdtd

: external interface >: internal bus : internal signal : component in the VHDL source code

: process in the VHDL source code

The FPGA interacts with the host system using the component Rt\_core. The Rt\_core delivers requests from the host system to component Rt\_client, it also delivers response from Rt\_client to the host system.

In the FPGA architecture, the Rt\_client acts as an agent for the host system to access the local memories and to control component Qdr\_fdtd.

Qdr\_fdtd contains three update engines. If enabled, Qdr\_fdtd can execute a specified number of iterations of FDTD algorithm calculation without interference from the host system. The magnetic update Hx and the magnetic update Hy in Qdr\_fdtd run in parallel. One Hx result and one Hy result can be produced per clock cycle. During the calculation, Qdr\_fdtd accesses the local memories exclusively. It reads input data from the local memories and stores intermediate results and output data to the local memories.

Qdr2\_core is used for the FPGA to access the local memories. Memory access requests from Rt\_client and from Qdr\_fdtd are multiplexed by component Mux. These requests are then processed by Qdr2\_core. Rt\_client and Qdr\_fdtd can't access the same SRAM at the same time.

The local memories have fixed delay, so no internal FIFOs are needed for the FPGA to access the local memories. This simplifies the FPGA design and improves the memory access speed.

#### **4.3.1.3 Data Organization in Local Memories**

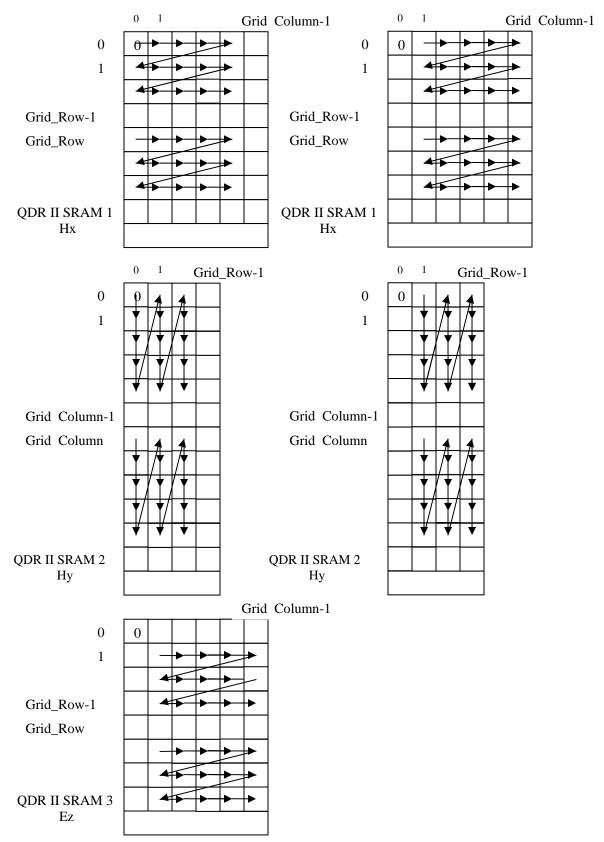

There are four independent local memories (QDR II SRAM 1 to QDR II SRAM 4) on the expansion module board (see 3.2.1.1). The QDR II SRAMs are 36-bit wide high speed, low latency memories. Each QDR II SRAM has 2 ports hence is capable of sustaining simultaneous, single clock, read and write accesses at clock speeds of up to 199 MHz [31]. QDR II SRAM 1 is used to store Hx<sub>t-1</sub> values and Hx<sub>t</sub> values, QDR II SRAM 2 is used to store  $Hy_{t-1}$  values and  $Hy_t$  values, QDR II SRAM 3 and 4 are used to store  $Ez_{t-1}$  values and  $Ez_t$  values.

The QDR II SRAMs are dual-port and the data stored in them is organized as ping-pong buffers. The ping-pong mechanism works like this: for cycle N, if the input data are stored in the lower (upper) parts of the SRAMs, then output data are stored in the upper (lower) parts of the SRAMs. Then during the next cycle N+1, the input data are read from the upper (lower) parts of the SRAMs and the output data are stored in the lower (upper) parts of the SRAMs. This process can continue until the specified number of calculation iterations is reached. This ping-pong mechanism enables the FPGA to execute many iterations of calculation with little communication with the host system. Reduction of data transfer between the host system and the FPGA during intervals between calculation iterations greatly improves the performance of the whole system.

The Hx<sub>t-1</sub> values and Hx<sub>t</sub> values are stored in QDR II SRAM 1 in row major order, The Hy<sub>t-1</sub> values and Hy<sub>t</sub> values are stored in QDR II SRAM 2 in column major order, the Ez<sub>t-1</sub> values and Ez<sub>t</sub> values are stored in QDR II SRAM 3 in row major order and stored in QDR II SRAM 4 in column major order. Assume the electromagnetic field processed by the FPGA is a Grid\_Row×Grid\_Column matrix, the row major order means value V[i][j] in the matrix is stored at the address i×Grid\_Column+j or Grid\_Row×Grid\_Column+ i×Grid\_Column+j in the QDR II SRAM, the column major order means value V[i][j] in the matrix is stored at the address j×Grid\_Row+i or Grid\_Row×Grid\_Column+ j×Grid\_Row+i in the QDR II SRAM.

The row major order and the column order are adopted so that Qdr\_fdtd can utilize these orders to improve throughput of the update engines. Utilizing these orders and

parallelism between magnetic update Hx and magnetic update Hy, Qdr\_fdtd can produce one Hx result and one Hy result per clock cycle or one Ez result every two clock cycles.

#### **4.3.1.4** Components and Processes

The components in the FPGA architecture include:

- Prog\_clock\_gen

- Rt\_core

- Qdr2\_core

- Rt\_client

- Qdr\_fdtd

- Mux

Component Prog\_clock\_gen generates the programmable global clocks.

Component Rt\_core is provided by Cray Inc. It connects internal components in the FPGA to external devices such as SMPs and other AAP FPGAs connected to the RapidArray Interconnect (see 3.2.1.2) in the Cray XD1 system. It allows internal components to access the external devices, and it also allows the external devices to access internal registers and local memories of the FPGA.

Component Rt\_core is connected to the external devices through ports Transmit Data Bus, Receive Data Bus, Host Processor Interface, Clock Signals, and it provides Fabric Request Interface and User Request Interface to internal components in the FPGA. Ports Transmit Data Bus and Receive Data Bus are used to transfer data between Rt-core and the external devices. The host Processor Interface is provide to the external devices to set the frequency of the programmable global clocks and to reset the FPGA. The

Fabric Request Interface is used by Rt\_core to forward the received remote memory access requests from the external devices to Rt\_client. It is also used to accept responses from Rt\_client, then the responses are forwarded by Rt\_core to the external devices. The User Request Interface can be used to accept memory access requests from internal components in the FPGA. Then these requests are forwarded by Rt\_core to the external devices to the external devices. It also can deliver the received responses from the external devices to the internal components. But in the current FPGA design, the User Request Interface is not used.

Component Qdr2\_core is provided by Cray Inc. It provides an interface for the FPGA to access the four external 36 bit wide QDR II SRAMs. It allows the internal components in the FPGA to simultaneously read and write the external QDR II SRAMs at a clock speeds from 130 MHz up to 199 MHz. Qdr2\_core is made up of four fully independent RAM interface blocks, each connected to an external QDR II SRAM. The four RAM interfaces blocks provide full control of the QDR II SRAMs including address, read data, write data, read and write enables. This allows the four QDR II SRAMs to be arranged in many different bank configurations [30].

Component Mux multiplexes memory access buses from Rt\_client and Qdr\_fdtd. After FPGA reset, memory access bus from Rt\_client is connected to the qdr2\_core and the four QDR II SRAMs can only be accessed by the external devices connected to the RapidArray Interconnect. If update engines in Qdr\_fdtd is enabled, then memory access bus from Qdr\_fdtd is connected to the qdr2\_core. When the update process completes, the qdr2\_core is switched back to Rt\_client.

Component Rt\_client acts as an agent for the host system to access the local memories and to control component Qdr\_fdtd. It processes requests from the external devices and gives response through the Fabric Request Interface, it also monitors the status of Qdr\_fdtd and controls the operation of Qdr\_fdtd. When it receives requests from the Fabric Request Interface, it checks if the request are read requests or write requests, it also checks the request addresses to tell if the requests should be directed to the internal registers or the external QDR II SRAMs. If the requests are read requests to the internal registers, then data stored in the internal registers are sent as response to the Fabric Request Interface. If the requests are write requests to the internal registers, then data from the Fabric Request Interface are stored into the internal registers and no response is given to the Fabric Request Interface. If the requests are read requests to the external QDR II SRAMs, Rt\_client issues memory read requests to component Mux and waits for response from the external QDR II SRAMs. When Rt\_client receives the response from Mux, it will forward the response to the Fabric Request Interface. If the requests are write requests to the external QDR II SRAMs, Rt\_client issues memory write requests to Mux and completes the requests without waiting for the response.

Component Rt\_client contains two internal registers: Update\_counter and FPGA\_reg. These two registers are used to control the operation of Qdr\_fdtd and to monitor the status of Qdr\_fdtd. Update\_counter is a 32-bit wide register. It specifies the iteration number of the FDTD algorithm calculation Qdr\_fdtd should complete. FPGA\_reg is a 64-bit wide register used by the host to specify parameters and initiate execution of the Qdr\_fdtd engine. The parameters in FPGA\_reg are shown in figure 4-8 and described below:

| bit 63-48          | 47-32       |                | 31          | 30          | 29                   |  |

|--------------------|-------------|----------------|-------------|-------------|----------------------|--|

| Grid_Row           | Grid_Column |                | Access_type | Update_type | HxHy_Source_Location |  |

| 28 27-2            |             | 27-2           | 1           | 2           |                      |  |

| Ez_Source_Location |             | Update_starter | Update_end  |             |                      |  |

Figure 4-8 : Parameters in Register FPGA\_reg

- Grid\_Row : the number of rows of the electromagnetic field matrix

- Grid\_Column : the number of columns of the electromagnetic field matrix

- Access\_type : if this bit is set to '0', then memory access bus from Rt\_client is connected to Qdr2\_core enabling the host to access the QDR II SRAMs; if this bit is set to '1', then memory access bus from Qdr\_fdtd is connected to Qdr2\_core and the update engines has access to the QDR II SRAMs

- Update\_type : if this bit is set to '0', then in the first iteration of the FDTD algorithm calculation, update engines magnetic update Hx and magnetic update Hy are enabled; if this bit is set to '1', then in the first iteration of the FDTD algorithm calculation, update engine electric update is enabled

- HxHy\_Source\_Location : this bit determines which ping-pong buffer to read for Hx and Hy data. If this bit is set to '0', then in the first iteration of the FDTD algorithm calculation, source data value Hx<sub>t-1</sub>[i][j] is stored in QDR II SRAM 1 at address i×Grid\_Column+j, source data value Hy<sub>t-1</sub>[i][j] is stored in QDR II SRAM 2 at address j×Grid\_Row+i; If this bit is set to '1', then in the first iteration of the FDTD algorithm calculation, source data value Hx<sub>t-1</sub>[i][j] is stored in QDR II SRAM 1 at address Grid\_Row+i; If this bit is set to '1', then in the first iteration of the FDTD algorithm calculation, source data value Hx<sub>t-1</sub>[i][j] is stored in QDR II SRAM 1 at address Grid\_Row×Grid\_Column+i×Grid\_Column+j, source data value Hy<sub>t-1</sub>[i][j] is stored in QDR II SRAM 1 at address Grid\_Row×Grid\_Column+i×Grid\_Column+j, source data value

Grid\_Row×Grid\_Column+j×Grid\_Row+i

- Ez\_Source\_Location : this bit determines which ping-pong buffer to read for Ez data. If this bit is set to '0', then in the first iteration of the FDTD algorithm calculation, source data value Ez<sub>t-1</sub>[i][j] is stored in QDR II SRAM 3 at address i×Grid\_Column+j and in QDR II SRAM 4 at address j×Grid\_Row+i; If this bit is set to '1', then in the first iteration of the FDTD algorithm calculation, source data value Ez<sub>t-1</sub>[i][j] is stored in QDR II SRAM 3 at address Grid\_Row×Grid\_Column+i×Grid\_Column+j and in QDR II SRAM 4 at address Grid\_Row×Grid\_Column+j×Grid\_Row+i

- Update\_starter : when this bit toggles, update engines in Qdr\_fdtd start FDTD algorithm calculation