# Compensation and Calibration Techniques for High Performance Current-Steering

DACs

# DISSERTATION

Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Samantha M. McDonnell, B.S.E.E., M.S.

Graduate Program in Electrical and Computer Engineering

The Ohio State University

2016

Dissertation Committee: Dr. Waleed Khalil, Advisor Dr. Joel Johnson Dr. Steven Bibyk Copyrighted by

Samantha M. McDonnell

2016

# Abstract

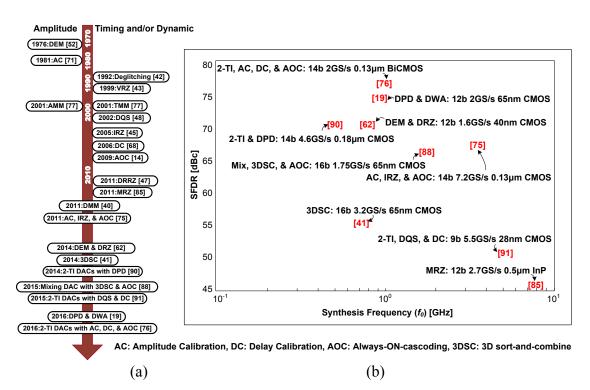

A myriad of research efforts, covering architectural, circuit and technological aspects, have been made towards improving the performance of digital-to-analog converters (DACs). However, the quest to achieve stringent dynamic linearity requirements (> 70dBc SFDR) over many gigahertz of bandwidth presents grand challenges to circuit designers and high-yield manufacturers. In light of these challenges, various calibration and compensation techniques have evolved over the past two decades to overcome design and process technology limitations.

In this work, the sources of nonlinearity in current-steering DACs are described and common circuit techniques, along with device technologies, which enable a high-performance baseline DAC, are detailed. The effect these non-idealities are investigated using a new modeling paradigm which accurately predicts the SFDR of the DAC in the presence of statistical process mismatch. This model offers a total speedup of ~330x per frequency point compared with Monte Carlo-based simulation methods. The model is useful in evaluating and developing calibration circuits, which is the focus of this work.

To highlight prior art, a historical overview of compensation and calibration techniques is presented, outlining the shift from amplitude to timing and dynamic correction. Furthermore, several techniques are simulated using the DAC model to compare their efficacy. In addition, current and emerging architectures are described, which help extend the synthesizable bandwidth of the DAC. As operating frequency increases beyond several MHz, timing errors are detrimental to DAC performance, yet few timing calibration techniques have been developed and verified on chip. This highlights the need for a novel timing calibration technique.

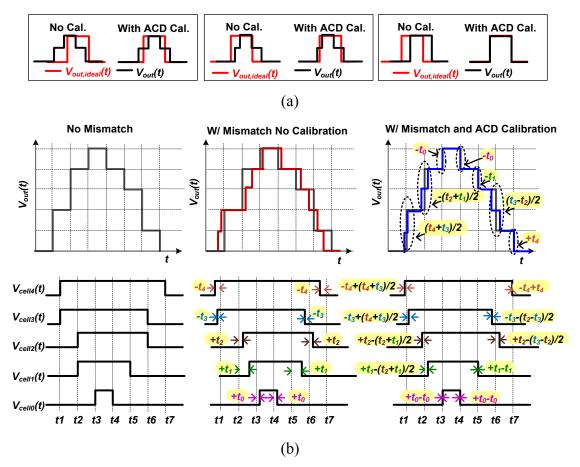

A new timing calibration, termed adaptive delay calibration (ACD), is designed in support of this work. It reduces timing mismatches in the DAC through modulation of the clock signal's delay to the DAC retiming data latches. The proposed technique is shown to reduce the effect of timing mismatches and improve the SFDR for both a single DAC and time interleaved (TI) DAC, as well as improve the signal-to-image rejection ratio (SIRR) in the TI DAC. To verify the ACD technique, a 14-bit DAC operating at  $f_{CLK}$  =3GHz is designed in a 130nm BiCMOS process. The DAC includes amplitude calibration, dynamic compensation, and the proposed ACD technique. Overall, ACD calibration shows promising results, however, it was not able to be verified on chip due to unforeseen design issues. These issues are investigated and proposed solutions are provided.

# Dedication

To my husband Christopher.

# Acknowledgments

I would like to thank my family: My parents that instilled good values and drive to pursue my education, to my sister and her family who have been here to support me, and to my husband who uprooted his life to be with me in Columbus during my education.

Thanks to the members of the CLASS lab for all their help and knowledge through the years. I'm especially indebted to: Jamin McCue for mentoring me throughout the years and for the design of several circuits used in this work, Luke Duncan for the calibration measurement circuits used in this work and the time he has spent helping with my calibration paper, and Darren Disabato for his help in board design.

To the RYDI team at AFRL, thank you for your guidance and support through the years, I'm looking forward to joining your team. A special thanks to Vipul Patel for the time he has spent on the calibration paper.

I would like to thank Dr. Brian Dupaix who has given much of his time to review papers and help with measurement setup.

Many thanks to my committee members, Dr. Steven Bibyk and Dr. Johnson, for their insight and for the many valuable classes I took with them.

Finally, I would like to thank my advisor, Dr. Waleed Khalil, for believing in me and encouraging me to pursue my education. None of this would be possible, without him. And to anyone I forgot....

-Thank you

# Vita

| 2008      | . B.S.E.C.E. (Magna Cum Laude), The Ohio     |

|-----------|----------------------------------------------|

|           | State University                             |

| 2008-2010 | Recipient of the Intel Foundation SRC GRC    |

|           | Master's Scholarship Program                 |

| 2010      | . DAGSI PhD Fellowship                       |

| 2010      | . M.S.E.C.E., The Ohio State University      |

| 2010-2011 | . Recipient of the 2010 DAGSI PhD Fellowship |

| 2011-2016 | Recipient of the SMART PhD Fellowship        |

# **Publications**

#### In-Progress

- S.M. McDonnell, B. Dupaix, and W. Khalil, "Statistical Modeling and Parametric Yield Prediction for CMOS Current-Steering DACs."

- S.M. McDonnell, B. Dupaix, L. Duncan, V.J. Patel, and W. Khalil. "Survey of Calibration and Compensation Techniques for Current-Steering DACs."

#### Journals

J. McCue, L. Duncan, S.M. McDonnell, B. Dupaix, and W. Khalil, W. "A Time-Interleaved Multi-mode ΔΣ RF-DAC for Direct Digital-to-RF Synthesis." *IEEE Journal of Solid-State Circuits*, 2016

- S. Balasubramanian, G. Creech, J. Wilson, S.M. Yoder, J.J. McCue, M. Verhelst, and W. Khalil, "Systematic Analysis of Interleaved Digital-to-Analog Converters," in Circuits and Systems II: Express Briefs, IEEE Transactions on, vol.58, no.12, pp.882-886, Dec. 2011.

- John Hu, Mark Haffner, Samantha Yoder, Gursharan Reehal, Mark Scott, and Mohammed Ismail, "An industry-driven laboratory development for mixedsignal IC test education," Circuits and Systems (ISCAS), Proceedings of 2010 IEEE International Symposium on , vol., no., pp.85-88, May 30 2010-June 2 2010.

#### Conference Proceedings

- S. M. Yoder, S. Balasubramanian, W. Khalil, and V.J. Patel, "Accuracy and speed limitations in DACs across CMOS process technologies," in Circuits and Systems (MWSCAS), 2013 IEEE 56th International Midwest Symposium on pp.868-871, 4-7 Aug. 2013

- Samantha Yoder, Mohammed Ismail, and Waleed Khalil. GOMACTech 2011, Paper/Presenter "Analysis and Modeling of Non-Idealities in VCO-Based Quantizers using Frequency-to-Digital and Time-to-Digital Converters"

#### Books and Book Chapters

• Samantha Yoder, Mohammed Ismail, and Waleed Khalil. VCO-Based Quantizers Using Frequency-to-Digital and Time-to-Digital Converters, SpringerBriefs in Electrical and Computer Engineering. New York, NY 2011.

# Fields of Study

Major Field: Electrical and Computer Engineering

Specialization: Analog and RF Electronics

# **Table of Contents**

| Abstract      |                                                | ii   |

|---------------|------------------------------------------------|------|

| Dedication    |                                                | iv   |

| Acknowledg    | gments                                         | v    |

| Vita          |                                                | vi   |

| Table of Cor  | ntents                                         | ix   |

| List of Table | es                                             | xiii |

| List of Figur | res                                            | xiv  |

| Chapter 1:    | Introduction                                   | 1    |

| 1.1. Cu       | rrent-Steering DAC Overview                    |      |

| 1.1.2.        | Intrinsic DAC Error Sources                    | 5    |

| 1.1.3.        | Mismatch DAC Error Sources                     |      |

| 1.2. Co       | ommon Current-Steering DAC Architecture        | 11   |

| 1.3. Use      | e of CMOS, Bipolar, and III-V Device Materials | 14   |

| 1.3.1.        | CMOS Technologies                              | 15   |

| 1.3.2.        | BiCMOS and III-V Technologies                  | 16   |

| Chapter 2: | Statistical Modeling for Current-Steering DAC             |    |

|------------|-----------------------------------------------------------|----|

| 2.1. Th    | e Proposed DAC Model                                      | 20 |

| 2.1.1.     | Hybrid DAC model                                          |    |

| 2.1.2.     | Rapid Mismatch Modeling Method                            |    |

| 2.1.3.     | Model Synthesis and Simulation                            |    |

| 2.2. Ex    | perimental Results                                        |    |

| 2.3. Co    | nclusion and Model Uses                                   |    |

| Chapter 3: | Compensation and Calibration Techniques                   | 33 |

| 3.1. Co    | mpensation Techniques                                     | 33 |

| 3.1.1.     | Deglitching                                               | 33 |

| 3.1.2.     | Return-to-Zero (RZ) and Differential Quad Switching (DQS) |    |

| 3.1.3.     | Always-ON-Cascoding                                       | 40 |

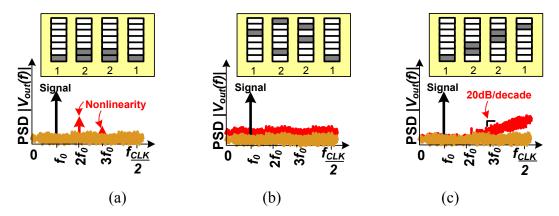

| 3.1.4.     | Dynamic Element Matching (DEM)                            | 41 |

| 3.2. Ca    | libration Techniques                                      | 43 |

| 3.2.1.     | Mismatch Measurement Circuits                             | 44 |

| 3.2.2.     | Amplitude Calibration                                     | 46 |

| 3.2.3.     | Delay Calibration                                         | 50 |

| 3.2.4.     | Mapping                                                   | 51 |

| 3.2.5.     | Digital Pre-distortion (DPD)                              | 57 |

| 3.3.    | Current and Emerging Architectures                  | 58 |

|---------|-----------------------------------------------------|----|

| 3.3.    | .1. Mixing DACs                                     | 59 |

| 3.3.    | 5.2. Multiple RZ (MRZ) DACs                         | 61 |

| 3.3.    | 3.3. Time-Interleaved (TI) DACs                     | 61 |

| 3.4.    | Conclusion and Motivation for Future Designs        |    |

| Chapter | r 4: Proposed Novel Timing Calibration Technique    | 64 |

| 4.1.    | Architecture and Calibration Procedure              | 66 |

| 4.2.    | Behavioral Simulation and Comparison with Prior Art |    |

| 4.2.    | 2.1. Single DAC study                               |    |

| 4.2.    | 2.2. Time-Interleaved (TI) DAC Study                | 74 |

| 4.2.    | 2.3. Discussion                                     | 74 |

| 4.3.    | Implementation Issues and Solutions                 |    |

| Chapter | r 5: Design of 14-bit 3GHz DAC in 130nm BiCMOS      | 79 |

| 5.1.    | Architecture                                        | 79 |

| 5.1.    | .1. DAC Core                                        | 80 |

| 5.1.    | .2. Clock Path                                      | 82 |

| 5.1.    | .3. Calibration                                     | 82 |

| 5.2.    | Layout Design and Extracted Simulation              | 84 |

| 5.3.    | Fabrication, Board Design, and Assembly             | 85 |

| 5.4.     | Measurement Setup and Results                       | . 88 |

|----------|-----------------------------------------------------|------|

| Chapter  | 6: Conclusion and Future Work                       | 91   |

| 6.1.     | Work Summary and Conclusion                         | 91   |

| 6.2.     | Future Work                                         | 92   |

| Bibliogr | aphy                                                | 93   |

| Appendi  | x A: Statistical Modeling MATLAB and Verilog-A Code | 99   |

| Appendi  | x B: SPI Register Control                           | 107  |

| Appendi  | x C: Testing Methodology                            | 108  |

| Appendi  | x D: Debugging                                      | 111  |

# List of Tables

| Table 1.1: Current DAC trends in telecommunication applications    2                   |

|----------------------------------------------------------------------------------------|

| Table 1.2: Duty cycle error per cell <i>k</i> depending on switching state transitions |

| Table 3.1: Required SFDR for various N-bit DACs, corresponding intrinsic current       |

| source area $(Ano - cal)$ without calibration, and combined current source and         |

| cal-DAC area (Acal) after calibration for optimized $m$ and $Ncal - DAC$ values.       |

|                                                                                        |

| Table 3.2: Input code vs. cell error, DNL, and INL for no mapping and 2 'sort-and-     |

| group' iterations for SSPA and CCF                                                     |

| Table 3.3: Simulated DNL, INL, and SFDR for baseline 12-bit DAC ( $fCLK = 2GHz$ )      |

| with no mapping and several x 'sort-and-group' iterations for SSPA and CCF 53          |

| Table A.1: Verilog-A retiming driver code value and parameter definition 100           |

| Table C.1: Simulated vs. measured DC supply currents    108                            |

# **List of Figures**

| Figure 1.1: Typical multiband transmitter PSD 1                                             |

|---------------------------------------------------------------------------------------------|

| Figure 1.2: <i>N</i> -bit binary current-steering DAC. (a) Simple architecture. (b) ZOH DAC |

| PSD. (c) Ideal vs. non-ideal output pulse decomposed into amplitude and timing              |

| errors. (b) ZOH nonlinear DAC PSD                                                           |

| Figure 1.3: Calculated intrinsic output (a) voltage, (b) time constant, and (c) duty cycle  |

| errors vs. input code for a 12-bit DAC operating at $fCLK = 2$ GHz using simulated          |

| transistor parameter values                                                                 |

| Figure 1.6: Summary of (a) intrinsic errors and (b) mismatch errors                   |

|---------------------------------------------------------------------------------------|

| Figure 1.7: CMOS output impedance and mismatch. (a) DAC current source impedance      |

| across technology (b) Current mismatches and (c) switching time mismatch              |

| across CMOS process technologies16                                                    |

| Figure 1.8: InP and CMOS (a) $f_T$ and (b) gain vs. frequency                         |

| Figure 2.1: Nonlinearity in the DACs conversion process and its effect on SFDR yield. |

|                                                                                       |

| Figure 2.2: Proposed hybrid DAC cell model. (a) Single cell. (b) Retiming Verilog-A   |

| code transient response (c) Arrayed unary cells                                       |

| Figure 2.3: Sampling theory for estimating SFDR                                       |

| Figure 2.4: Capture of process mismatches in the DAC and mismatch reordering          |

| process                                                                               |

| Figure 2.5: Proposed model synthesis and simulation using MATLAB and Cadence 27       |

| Figure 2.6: Comparison between full transistor model, purely behavioral model, and    |

| proposed hybrid model DAC SFDR across operating frequencies for (a) $f_{clk}$         |

| =500MHz (b) $f_{clk}$ =2GHz and (c) $f_{clk}$ =4GHz                                   |

| Figure 2.7: Simulated DAC full transistor and hybrid model. SFDR vs. frequency with   |

| (a) current mismatch, (b) timing mismatch (c) all mismatches. (d) Yield vs.           |

| frequency for SFDR $\geq$ 67.8 dB with all mismatches                                 |

| Figure 2.8: Impact of various intrinsic and mismatch errors on SFDR across frequency  |

| for the 12-bit baseline DAC operating at $fCLK = 2$ GHz                               |

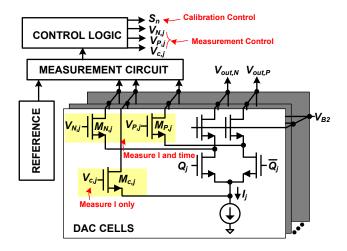

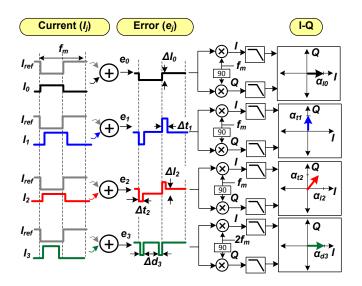

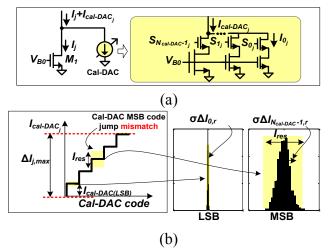

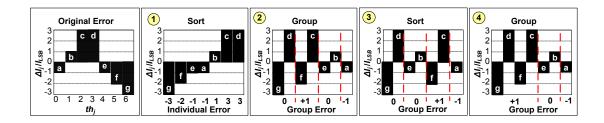

Figure 3.1: Typical deglitching compensation. (a) Block diagram. (b) Timing diagram. Figure 3.2: Sampled sinusoid (Vout) and frequency-domain response (|Hi(f)|) for the Figure 3.3: Modified DAC architecture with (a) voltage RZ (VRZ), (b) current RZ (IRZ), (c) digital RZ (DRZ/DRRZ), and (d) differential quadrature switching (DQS). (e) Time domain waveforms for NRZ, VRZ, IRZ, DRRZ, and DQS...... 36 Figure 3.4: Simulated 12-bit baseline DAC (fCLK = 2GHz) implemented with NRZ, IRZ, DRRZ, and DQS. (a) SFDR vs. frequency. (b) PSD at f0 = 923 MHz. ...... 39 Figure 3.5: DAC cell highlighting ON and OFF branches, (a) normal cell, (b) with Figure 3.6: Illustration of switching order and PSD for 7-unary cell DAC implemented with (a) no DEM, (b) stochastic DEM, and (c) deterministic DWA. ..... 42 Figure 3.7: Modified DAC architecture with auxiliary measurement transistors Figure 3.8: Concept of zero-IF mismatch sensor measurement. The measured reference waveform (Iref) is added to the cell waveform (Ij), downconverted with an I-Q

mixer, and lowpass filtered to DC to provide a measure of the current  $(\alpha I j \sim 2\Delta I j / \Delta I j)$

$\pi$ ), delay ( $\alpha tj \sim 4Ijfm\Delta tj$ ), and duty cycle ( $\alpha dj \sim 4Ijfm\Delta dj$ ) error between *Iref*

| Figure 4.1: Concept of ACD calibration. (a) Single output pulse. (b) 5 unary cell       |

|-----------------------------------------------------------------------------------------|

| example                                                                                 |

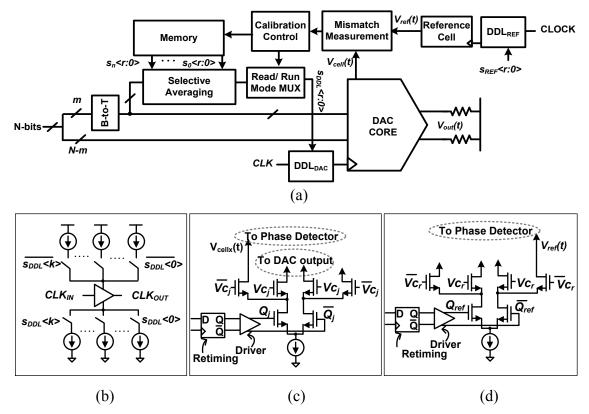

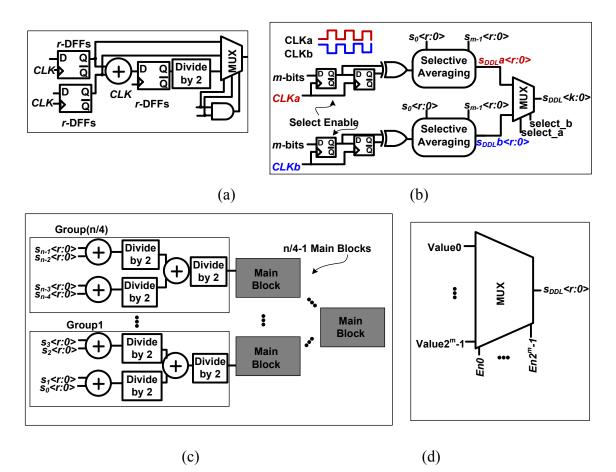

| Figure 4.2: Adaptive clock delay calibration architecture. (a) Top level block diagram. |

| (b) DDL circuit. (c) DAC cell. (d) Reference cell                                       |

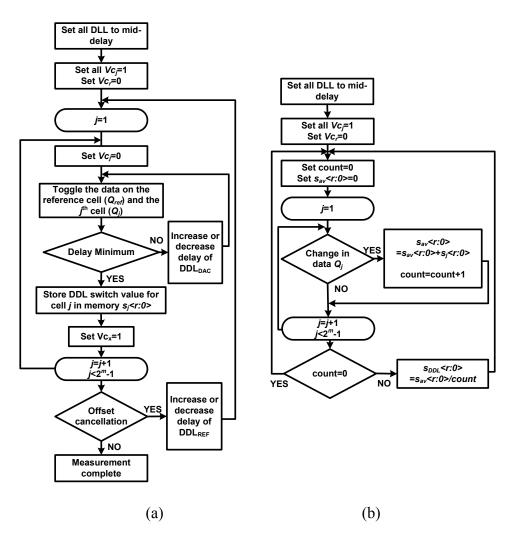

| Figure 4.3: Calibration algorithm (a) read mode and (b) run more                        |

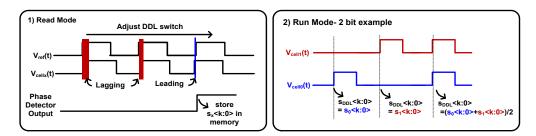

| Figure 4.4: Timing diagram. (a) Read mode. (b) Run mode                                 |

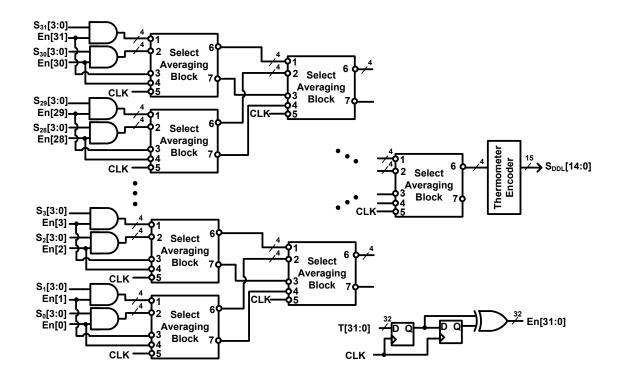

| Figure 4.5: Circuit implementation of selective averaging                               |

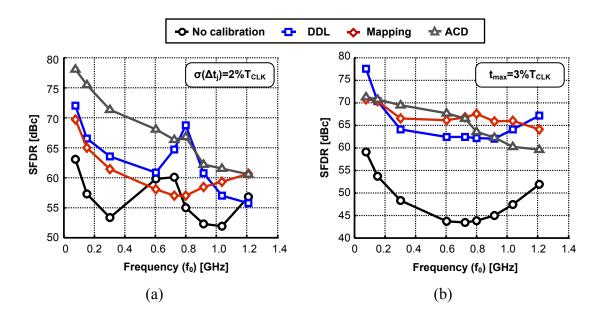

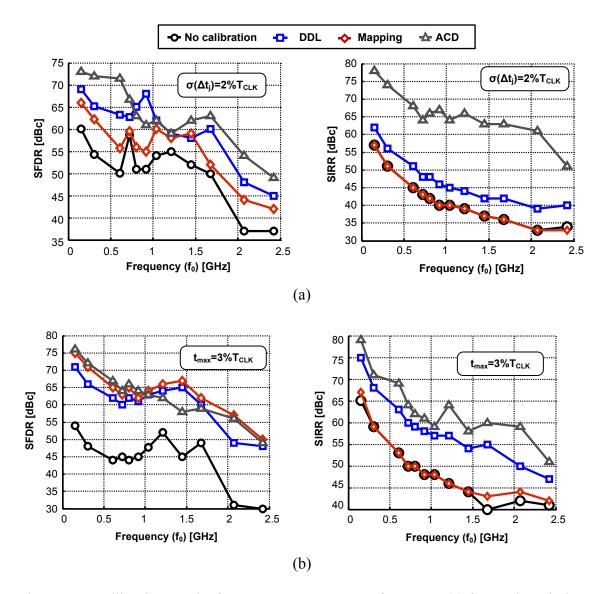

| Figure 4.6: Simulated SFDR vs. frequency for single DAC with timing calibration. (a)    |

| Random timing error result. (b) Systematic timing error result73                        |

| Figure 4.7: Calibration results for 2-TI DAC: SFDR vs. frequency (a) for random         |

| timing errors and (b) for systematic timing errors                                      |

| Figure 4.8: ACD calibration implementation solutions (a) pipelining (b) parallelization |

| (c) grouping (d) pre-computing                                                          |

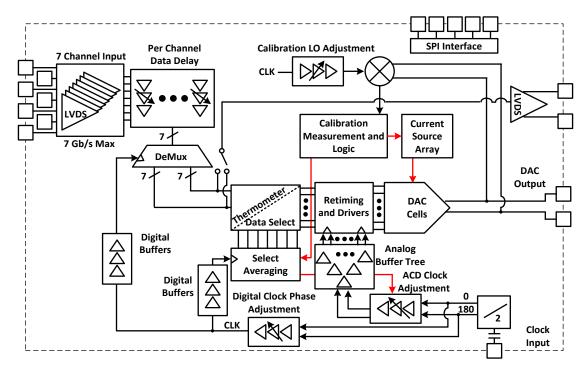

| Figure 5.1: Top level DAC chip block diagram                                            |

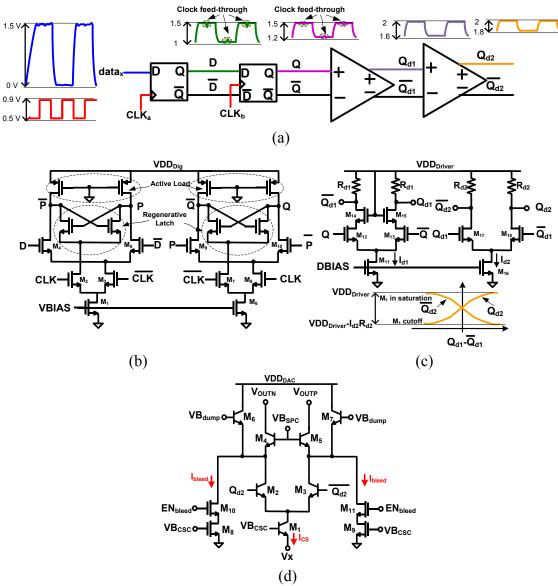

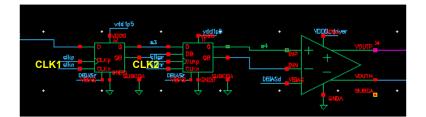

| Figure 5.2: (a) DAC data path with retiming flip-flop and buffer. (b) CML retiming      |

| flip-flop. (c) CML driver. (d) DAC cell                                                 |

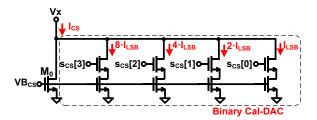

| Figure 5.3: Current calibration 4-bit binary cal-DAC                                    |

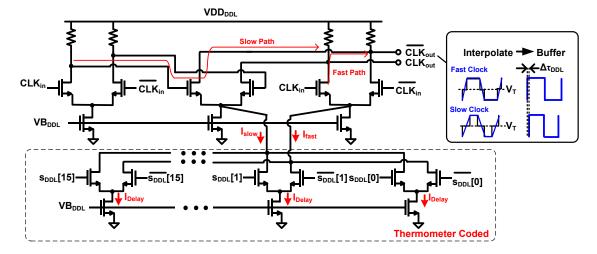

| Figure 5.4: 4-bit DDL for timing adjustment                                             |

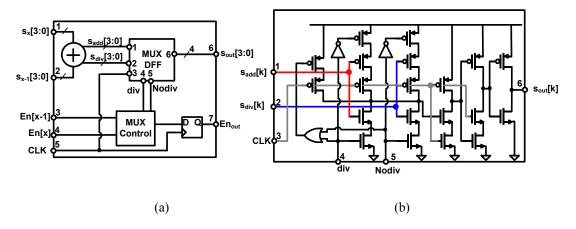

| Figure 5.5: ACD timing calibration. (a) Select averaging block including a carry-look-  |

| ahead divide by two, MUX control, and combined DFF MUX. (b) DFF MUX 84                  |

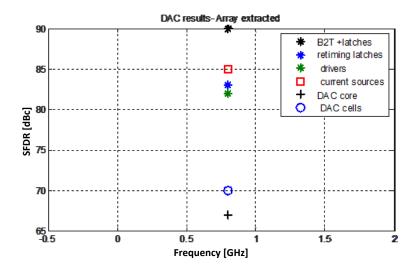

| Figure 5.6: Extracted DAC SFDR                                                          |

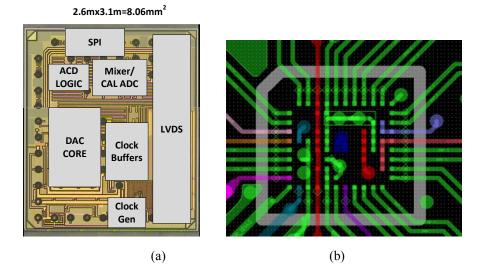

| Figure 5.7: (a) Chip micrograph. (b) Allegro PCB chip pad                               |

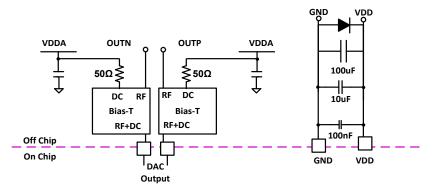

| Figure 5.8: Allegro PCB schematic design highlighting of output network and power         |

|-------------------------------------------------------------------------------------------|

| decoupling and protection                                                                 |

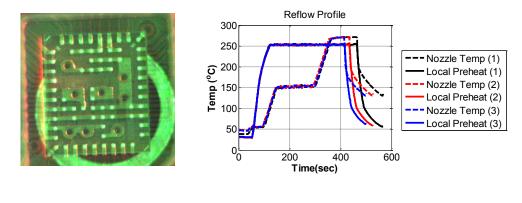

| Figure 5.9: Flip-chip mounting. (a) Alignment. (b) Reflow profiles                        |

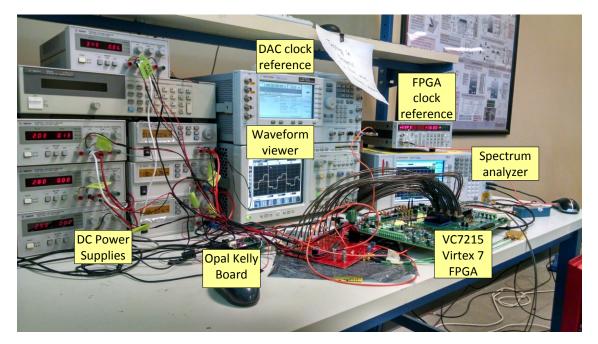

| Figure 5.10: Test setup for the 14-bit DAC                                                |

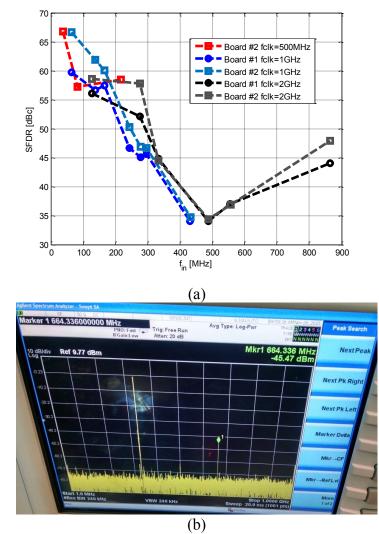

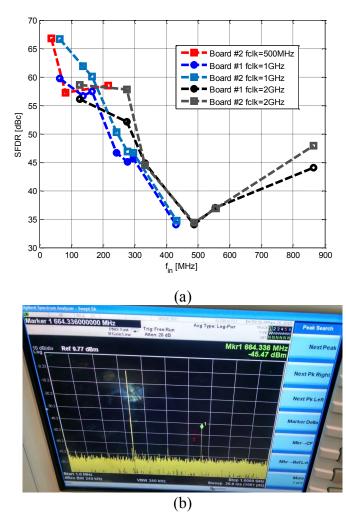

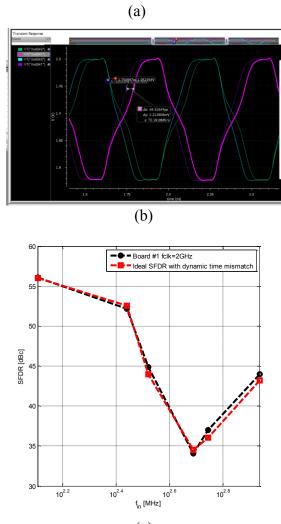

| Figure 5.11: (a) measured SFDR vs. frequency for 2 separate boards at                     |

| fCLK = 500MHZ, 1GHz, and 2GHz. (b) spectrum analyzer output for board #1 at               |

| fCLK = 2GHz and $fin = 860$ MHz90                                                         |

| Figure A.1: Spice in netlist importer. (a) Input file definitions. (b) Output file        |

| definitions                                                                               |

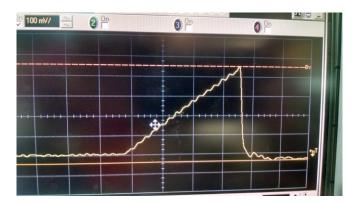

| Figure C.1: Ramp test on MSB cells                                                        |

| Figure C.2: (a) measured SFDR vs. frequency for 2 separate boards at                      |

| fCLK = 500MHZ, 1GHz, and 2GHz. (b) spectrum analyzer output for board #1 at               |

| fCLK = 2GHz and $fin = 860$ MHz                                                           |

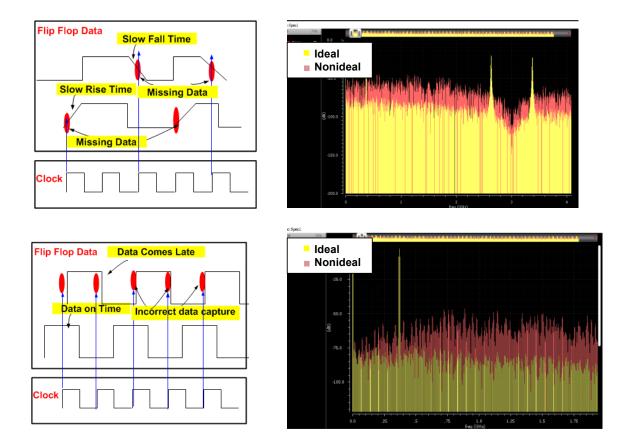

| Figure D.1: Simulation result of missing either a rising or falling data edge and missing |

| a data completely                                                                         |

| Figure D.2: (a) Data path. (b) Metastable flip-flop output with large timing delay        |

| (~50ps) between two data points. (c) Measured SFDR vs. frequency compared                 |

| with theoretical SFDR                                                                     |

# **Chapter 1: Introduction**

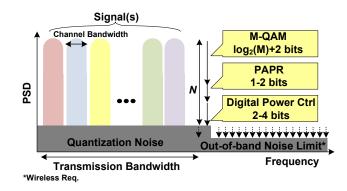

The rapid growth of mobile and fixed broadband access has been made possible through the continued digital scaling called for by Moore's law. However, as the shift occurs to Gbps wireless and Tbps wired networks, one perennial challenge is how to move such unprecedented bandwidths of data from the digital domain to the physical (analog) domain. This calls for high performance digital-to-analog converters (DACs) that are capable of synthesizing signals with complex *M*-QAM modulation schemes, while covering several GHz of bandwidth (BW). A typical power spectral density (PSD) of a wireless or wireline infrastructure DAC is displayed in Figure 1.1. The DAC synthesizes several channels with an aggregate BW that is limited to half the DAC update frequency ( $f_{CLK}$ ). The DAC's SNR budget, and hence its resolution (*N*), is set by several effects: the required modulation accuracy, peak-to-average power ratio (PAPR), and dynamic power control back-off. For example, a 512-QAM OFDM transmitter with 10dB

Figure 1.1: Typical multiband transmitter PSD

PAPR and 12dB digital control range requires a DAC with at least N = 14-bits. In the case of wireless infrastructure, the DAC's out-of-band noise is most critical and ends up setting its resolution. Table 1.1 highlights current design trends for high performance DACs covering telecommunication<sup>123</sup> and radar<sup>4</sup> applications.

| Application          | # of Bits (N) | BW (MHz) | $f_{CLK}$ (MHz) |

|----------------------|---------------|----------|-----------------|

| Cable Modem          | 14            | 1000     | 4600            |

| Cellular Basestation | 16            | 500      | 2800            |

| Satellite            | 12            | 1000     | 3000            |

| Radar                | 12            | 2000     | 4000            |

Table 1.1: Current DAC trends in telecommunication applications

Several DAC architectures exist to meet application demands with some better suited for either large N or high  $f_{CLK}$ . For example, instrumentation and audio applications use Delta-Sigma ( $\Delta\Sigma$ ) DACs which oversample and noise shape data to achieve highresolution ( $N \ge 16$ ) within a fraction of  $f_{CLK} < 10$ MHz. Resistor string and R2R DACs are utilized in industrial process control and data acquisition systems [1] that require moderate speed ( $f_{CLK} < 1$ MHz) and moderate resolution ( $8 \le N \le 16$ ). Due to their fast switching current configuration, current-steering DACs are suitable for high-speed ( $f_{CLK} > 10$ MHz) applications that require moderate resolution.

Across DAC architectures, output amplitude errors limit the accuracy upwards of DC. Applications demanding moderate to high-resolution typically require amplitude

<sup>&</sup>lt;sup>1</sup> Cable modem specifications: Maxim Integrated Circuits (MAX5882)

<sup>&</sup>lt;sup>2</sup> Cellular basestation specifications: Texas Instruments (DAC39J84). BW based on LTE 5x pre-distortion

<sup>&</sup>lt;sup>3</sup> Satellite specifications: E2V (EV12DS130). BW based on C-band satellite.

<sup>&</sup>lt;sup>4</sup> Radar specifications: Maxim Integrated Circuits (MAX19693). BW based on X-band radiolocation.

correction:  $\Delta\Sigma$  DACs apply dynamic element matching (DEM) to average amplitude errors [2], resistor string and *R2R* DACs remove amplitude errors through trimming resistors [3], and current-steering DACs utilize on-chip amplitude error correction methods. Additionally, DACs operating beyond several MHz experience static timing and dynamic non-idealities that result in a frequency dependent degradation in DAC linearity. Since the current-steering architecture is the linchpin for GHz operation, numerous calibration and compensation techniques have been proposed to improve its linearity.

## **1.1.** Current-Steering DAC Overview

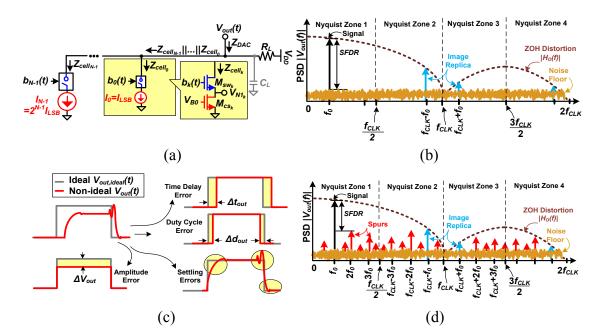

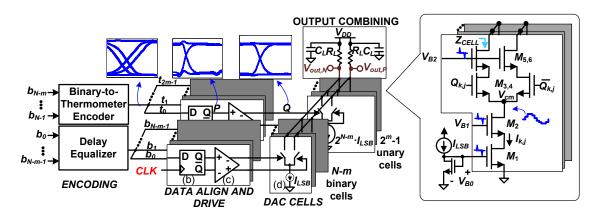

The simplest form of an *N*-bit current-steering DAC, shown in Figure 1.2(a), consists of an array of cells which contain a binary weighted current source ( $I_k = 2^k I_{LSB}, k =$ N - 1, ..., 1, 0) and switch controlled by an input digital code ( $b_k \in \{0,1\}$ ). Depending on  $b_k$ , current is steered to and from the output combining load resistor ( $R_L$ ) providing the DC output voltage

$$V_{out} = R_L \cdot I_{LSB} \sum_{k=0}^{k=N-1} b_k \cdot 2^k.$$

(1.1)

Typically,  $b_k$  is held constant for a clock update period  $(T_{CLK})$  resulting in a zero-order hold (ZOH) non return-to-zero (NRZ) output. For a sinusoidal input, the output PSD, displayed in Figure 1.2(b), contains a single tone at the input signal frequency  $(f_0)$ , noise floor set by N, image replica tones generated by the sampled nature of the signal at  $f_{CLK} \pm f_0, 2f_{CLK} \pm f_0, ...,$  and ZOH sinc response  $(|H_0(f)|)$ . On this plot, the power ratio of signal to largest spur, or spurious-free-dynamic range (SFDR), provides a measure of DAC linearity. In an ideal case, the maximum SFDR is [4]

$$SFDR[dBc] \cong 8.2N + 2.2.$$

(1.2)

In a physical DAC, however, the output also drives a capacitive load<sup>5</sup> ( $C_L$ ) and the cells are implemented with a transistor current source ( $M_{cs_k}$ ) and switch ( $M_{sw_k}$ ) (Figure 1.2(a)).  $I_k$  is scaled by sizing  $M_{cs_k}$ , while  $M_{sw_k}$  is sized accordingly to maintain the same voltage bias condition, and hence, achieve identical switching time ( $st_k$ ) among DAC cells. After  $b_k$  switches,  $V_{out}$  settles to the desired value according to the output time constant ( $\tau_{out} = R_L C_L$ ). Non-ideal transistor behavior results in output amplitude ( $\Delta V_{out}$ ), time delay ( $\Delta t_{out}$ ), duty cycle ( $\Delta d_{out}$ ), and nonlinear settling errors as depicted in Figure

Figure 1.2: *N*-bit binary current-steering DAC. (a) Simple architecture. (b) ZOH DAC PSD. (c) Ideal vs. non-ideal output pulse decomposed into amplitude and timing errors. (b) ZOH nonlinear DAC PSD.

<sup>&</sup>lt;sup>5</sup> Capacitance from layout interconnect, pad, package, and board routing.

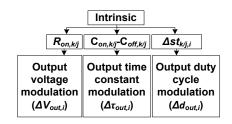

1.2(c), all of which introduce spurs in the PSD that degrade SFDR (Figure 1.2(d)). These errors can be classified as intrinsic (i) arising from the transistor terminal behavior, random (r) resulting from transistor process mismatch, and systematic (s) attributed to layout effects.

## **1.1.2. Intrinsic DAC Error Sources**

The intrinsic transistor parameters  $(g_m, r_{ds}, C_{gs}, C_{gd}, C_{db}, C_{sb})$  have two detrimental effects on the DAC performance. First, they manifest in a finite cell impedance  $(Z_{cell_k}(j\omega, V_{out}, b_k))$  which alters the effective DAC output impedance (1.3), resulting in amplitude and RC settling errors.

$$Z_{DAC}(j\omega, V_{out}, b_{0:N-1}) = R_L \|C_L\| Z_{cell_0}\| \dots \|Z_{cell_{N-1}}.$$

(1.3)

Second, they allow voltage to couple between  $V_{out}$  and the internal nodes of the cell  $(b_k, V_{N1_k}, V_{B0})$ , impacting the switching time accuracy and generating feedthrough glitches.

# 1.1.2.1. Output Voltage Error ( $\Delta V_{out,i}$ ), Induced by Cell Resistance Modulation

At DC, the cell impedance toggles between ON, i.e.  $Z_{cell_k}(j\omega = 0, b_k = 1) \sim g_{m,sw_k} r_{ds,cs_k}$ , and OFF, i.e.  $Z_{cell_k}(j\omega = 0, b_k = 0) \sim \infty^6$ . This results in an intrinsic DC output voltage error that degrades low frequency SFDR [5]

$$\Delta V_{out,i} \sim \frac{V_{out} R_L \sum_{k=0}^{N-1} \left( Z_{cell_k} (j\omega = 0, b_k) \right)^{-1}}{1 + R_L \sum_{k=0}^{N-1} \left( Z_{cell_k} (j\omega = 0, b_k) \right)^{-1}}.$$

(1.4)

<sup>&</sup>lt;sup>6</sup> In a 65nm process:  $Z_{cell_k}(j\omega = 0, b_k = 0) \sim 10^3 * Z_{cell_k}(j\omega = 0, b_k = 1)$  and hence is negligible.

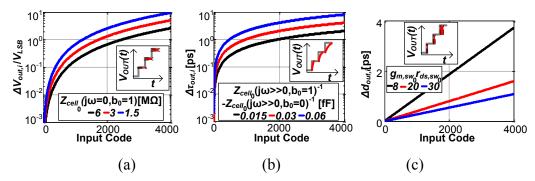

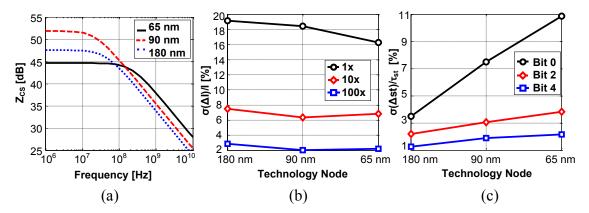

Figure 1.3(a) depicts the impact of varying the LSB current and subsequently  $Z_{cell_0}(j\omega =$  $(0, b_0 = 1)^7$  on  $\Delta V_{out,i}$ . It is desired to have a large  $Z_{cell_k}(j\omega = 0, b_k = 1)$  such that  $\Delta V_{out,i}$  is minimal. However, the size and current scaling requirements for  $M_{cs_k}$  and  $M_{sw_k}$  call for  $Z_{cell,k}(j\omega = 0, b_k = 1) = Z_{cell,0}(j\omega = 0, b_0 = 1)/2^k$ , making it challenging to achieve high impedance in the most significant binary cells of moderateto high-resolution DACs.

## 1.1.2.2. Output Time Constant Error ( $\Delta \tau_{out,i}$ ), Induced by Cell Drain **Capacitance Modulation**

As frequency increases, the transistor capacitance starts to effect  $Z_{cell_k}(j\omega \gg 0, b_k)$ which toggles between ON, i.e.  $Z_{cell_k}(j\omega \gg 0, b_k = 1)^{-1} \sim j\omega C_{gd,cs_k}/(g_{m,sw_k}r_{ds,sw_k})$ and OFF, i.e.  $Z_{cell_k}(j\omega \gg 0, b_k = 0)^{-1} \sim j\omega C_{gd_sw_k}^8$ . This code dependency modulates the DAC output time constant (1.5), inducing intrinsic settling errors that results in a frequency dependent degradation in SFDR [5].

$$\Delta \tau_{out,i} \sim R_L \sum_{k=0}^{N-1} \left( Z_{cell_k}(j\omega \gg 0, b_k) \right)^{-1}.$$

(1.5)

Figure 1.3(b) plots the resulting  $\Delta \tau_{out,i}$  for various values of LSB  $Z_{cell_0}(j\omega \gg 0, b_k =$  $(1)^{-1} - Z_{cell_0}(j\omega \gg 0, b_k = 0)^{-19}$ . It is desired to have nearly equal ON and OFF switch capacitances such that  $\Delta \tau_{out,i}$  is minimal. However, the cell scaling mandates  $Z_{cell_k}(j\omega \gg 0, b_k = 1)^{-1} = 2^k \cdot Z_{cell_0}(j\omega \gg 0, b_0 = 1)^{-1}$ , exacerbating  $\Delta \tau_{out,i}$  as k increases.

<sup>&</sup>lt;sup>7</sup> Decreases with  $I_{LSB} = 5, 15, 35 \mu A$ .

$<sup>^{8}</sup>C_{gd,cs_{k}}/g_{m,sw_{k}}r_{ds,sw_{k}} \gg C_{gd,sw_{k}}$  since  $M_{cs,k}$  is much larger than  $M_{sw,k}$ . <sup>9</sup> Increases with  $W_{cs_{0}}/L_{cs_{0}} = 1\mu$ m/500nm, 2 $\mu$ m/500nm, and 4 $\mu$ m/500nm.

Figure 1.3: Calculated intrinsic output (a) voltage, (b) time constant, and (c) duty cycle errors vs. input code for a 12-bit DAC operating at  $f_{CLK}$  =2GHz using simulated transistor parameter values.

# 1.1.2.3. Output Duty Cycle Error ( $\Delta d_{out,i}$ ), Induced by Cell Switch Time **Modulation**

When the cell is ON, finite switch output resistance  $(r_{ds,sw_k})$  allows  $V_{out}$  to couple to the source node  $(V_{N1_k})$ , modulating the switch bias voltage. This in turn results in code dependent cell switching time  $(\Delta s t_{k,i})$  that is subject to the extent of voltage feedthrough along with signal  $b_k$ 's rise/fall time  $(\tau_{b_k})$  and voltage swing  $(\Delta V_{b_k})$  [6]

$$\Delta st_{k,i}(t) = \frac{V_{out}(t)}{1 + g_{m,sw_k} r_{ds,sw_k}} (\tau_{b_k} / \Delta V_{b_k}).$$

(1.6)

Note that all the DAC cells have an identical switching time which changes as a function of  $V_{out}(t)^{10}$ . This code-dependency results in a duty cycle error per cell  $(\Delta d_k(t))$  that varies with the switching state of  $b_k$  (see Table 1.2). This aggregates to an output duty cycle error ( $\Delta d_{out,i}$ ) that results in a frequency dependent degradation in SFDR. Figure 1.3(c) plots  $\Delta d_{out,i}$  for different values of  $g_{m,sw_0} r_{ds,sw_0}^{11}$ .

<sup>&</sup>lt;sup>10</sup>  $g_{m,sw_k} \propto I_k$ ,  $r_{ds,sw_k} \propto 1/I_k$ , and assuming  $\tau_{b_k}$  and  $\Delta V_{b_k}$  are the same. <sup>11</sup> Increases with  $L_{sw_0} = 50$ nm, 75nm, and 100nm.

| $b_k(t-T_{CLK})$ | $b_k(t)$ | $b_k(t+T_{CLK})$ | $\Delta d_k(t)$                                     |

|------------------|----------|------------------|-----------------------------------------------------|

| Х                | 0        | Х                | 0                                                   |

| 0                | 1        | 0                | $\Delta st_{k,i}(t - T_{CLK}) + \Delta st_{k,i}(t)$ |

| 0                | 1        | 1                | $\Delta st_{k,i}(t-T_{CLK})$                        |

| 1                | 1        | 0                | $\Delta st_{k,i}(t)$                                |

| 1                | 1        | 1                | 0                                                   |

Table 1.2: Duty cycle error per cell k depending on switching state transitions.

#### 1.1.2.4. Glitch Feedthrough, Coupled through Cell Capacitance

Switch feedthrough glitches propagate to  $V_{out}$ ,  $V_{B0}$ , and  $V_{N1_k}$  through  $M_{cs_k}$  and  $M_{sw_k}$ 's  $C_{gs}$ ,  $C_{gd}$ ,  $C_{db}$ , and  $C_{sb}$ , creating  $V_{out}$  settling errors that are proportional to the switching cell size and  $I_k$  [7]. Switching glitches are created by several effects:

- When  $M_{sw_k}$  turns off, charge is injection and a glitch occurs on  $V_{out}$  and  $V_{N1_k}$

- When  $M_{sw_k}$  turns off,  $M_{cs_k}$  is choked and  $I_k$  is discharge through  $M_{cs_k}$ 's  $C_{db}$  creating a glitch on  $V_{N1_k}$  which propagates to  $V_{out}$ .

- When the DAC code changes, glitches are created on  $V_{out}$  from imperfect synchronization of current. For example if  $b_0 = 1$ ,  $b_1 = 0$ , and  $b_2 = 1$  ( $I_{out} = I_0 + I_2$ ) switches to  $b_0 = 1$ ,  $b_1 = 1$ , and  $b_2 = 0$  ( $I_{out} = I_0 + I_1$ ) there could be a moment when  $b_1$  and  $b_2$  are simultaneously switched on causing ( $I_{out} = I_0 + I_1 + I_2$ ).

- When a glitch propagates to  $V_{B0}$  from  $V_{N1_k}$ , a current error glitch occurs on  $V_{out}$ .

# 1.1.3. Mismatch DAC Error Sources

There are two predominant sources of mismatch in the DAC: random mismatch arising from photolithographic process variations and systematic resulting from layout routing.

#### **1.1.3.1.Random Output Voltage** ( $\Delta V_{out,r}$ ) and Duty Cycle Errors ( $\Delta d_{out,r}$ )

Photolithographic manufacturing results in random Gaussian distributed variation  $\mathcal{N}(\mu, \sigma^2)^{12}$  in the transistor gain factor:  $\beta = \mu_n C_{ox} W/L^{13}$  and threshold voltage:  $V_T$ . The variation in  $M_{cs_k}$  induces random current mismatch ( $\Delta I_{k,r}$ ), while variation in  $M_{sw_k}$ results in switching time mismatch ( $\Delta st_{k,r}$ ) [8]. The variance in  $\Delta I_{k,r}$  is equal to<sup>14</sup> [8]

$$\frac{\sigma^2(\Delta I_{k,r})}{I_k} = \frac{\sigma^2(\Delta\beta)}{\beta} + \frac{\sigma^2(2\Delta V_T)}{V_{OD}} = \frac{1}{WL} \left( A_\beta^2 + \frac{4A_{V_T}^2}{V_{OD}^2} \right).$$

(1.7)

where  $A_{\beta}$ ,  $A_{VT}$  are process dependent parameters. The variance in  $\Delta s t_{k,r}$  is primarily generated from the transistors  $V_T$  mismatch [7]

$$\sigma^{2}(\Delta st) = A_{V_{T}}^{2} C_{ox}^{2} \frac{WL}{l^{2}}.$$

(1.8)

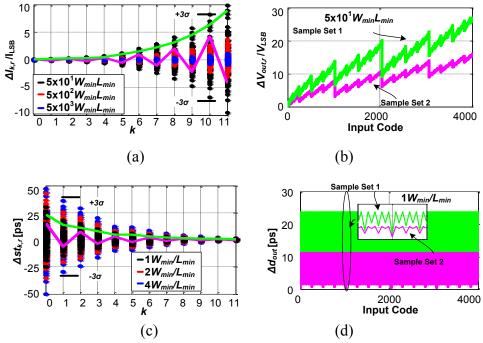

Note that, the spread of these mismatches is dependent on relevant transistor area. Figure 1.4(a-b) depicts the spread of  $\Delta I_{k,r}$  and corresponding accumulated random output voltage error ( $\Delta V_{out,r}$ ) for different sizes ( $xW_{min}/L_{min}$ )<sup>15</sup> of the LSB  $M_{cs_0}$  transistor. Alternatively, the spread of  $\Delta st_{k,r}$  and equivalent duty cycle error ( $\Delta d_{out,r}$ ) are plotted in Figure 1.4(c-d) for different sizes of the LSB  $M_{sw_0}$  transistor. As shown, the spread in  $\Delta I_{k,r}^{16}$  [8] reduces while  $\Delta s t_{k,r}^{17}$  [7] increases with larger LSB transistor sizes and both follow a sublinear relationship with bit order (k). Note also that the maximum amount of deviation in  $\Delta V_{out,r}$  and  $\Delta d_{out,r}$  are dependent on the distribution of cell mismatch values

<sup>&</sup>lt;sup>12</sup> Random variable with mean ( $\mu$ ) and variance ( $\sigma^2$ ).

$<sup>^{13}\</sup>mu_n$  is the transistor mobility,  $C_{ox}$  is the transistor oxide capacitance, W is the transistor width, and L is the transistor length.

$<sup>^{14}</sup>V_{OD} = (V_{GS} - V_T)$  is the overdrive voltage of the transistor, and  $V_{GS}$  is the gate-to-source bias voltage.  $^{15}W_{min}/L_{min} = 100$ nm/50nm in a 65nm process.

$<sup>^{16} \</sup>Delta I_{k,r} \propto I_k / \sqrt{W_{cs_k} L_{cs_k}}.$

$<sup>^{17} \</sup>Delta st_{k,r} \propto \sqrt{W_{sw_k} L_{sw_k}} / I_k.$

Figure 1.4: Simulated random mismatch for a 12-bit DAC with  $I_{LSB} = 5\mu$ A. (a) Current source mismatch vs. cell index (k) for selected sizes of the LSB  $M_{cs_0}$  transistor and (b) corresponding output voltage error vs. input code for two unique sample sets with from (a) with  $M_{cs_0} = 50 \times W_{min}L_{min}$ . (c) Switching time mismatch vs. k for selected sizes of the LSB  $M_{sw_0}$  transistor and (d) corresponding output duty cycle error for two unique sample sets from (c) with  $M_{sw_0} = W_{min}/L_{min}$ . Note the error in (c) and (d) is a function of the sample set. When the sequential cell mismatch is correlated (sample set 1) the error accumulates faster and is larger than if it is uncorrelated (sample set 2).

[9]. For example, in sample set 1 the mismatch values in adjacent cells are strongly correlated and accumulate into a large error, while the mismatch in sample set 2 cancels between adjacent cells producing a smaller error. As a result, the spread of cell mismatches for a given sample set will determine the DAC SFDR performance.

# 1.1.3.2. Systematic Output Voltage $(\Delta V_{out,s})$ and Time Constant Delays $(\Delta \tau_{out,s})$

Routing metal used during DAC layout have an associated resistance  $(R_M)$  and capacitance  $(C_M)$  which induce additional mismatch. Voltage drops across  $R_M$  create deviations in the ground supply for each cell inducing systematic current mismatch  $(\Delta I_{k,s})$  in  $M_{cs_k}$  [10], while data path routing line  $R_M C_M$  mismatch result in systematic output time constant delays  $(\Delta \tau_{out,s})$  that have an increasing impact with frequency [11].

## **1.2.** Common Current-Steering DAC Architecture

While simple in nature, the binary DAC with two transistor cell does not provide optimal performance. A widely used architecture is pictured in Figure 1.5 and adopts the following techniques to achieve a high performance baseline DAC:

- The DAC cell is implemented differentially with the switch pair  $(M_{3,4})$  to reduce glitch feedthrough errors, increase common mode rejection, and reduced even order distortion.

- The DAC cell utilizes cascoding transistors on the current source  $(M_2)$  and switch pair  $(M_{5,6})$  to increase cell ON resistance, thereby reducing output voltage  $(\Delta V_{out,i})$ and output duty cycle errors  $(\Delta d_{out,i})$ . The cascode transistors also help shield  $V_{out}$ and  $V_{N1_k}$  from glitch feedthrough [12].

- A technique known as segmentation is used to decode the top *m*-bits  $(b_{N-1}: b_{N-m})$  to a thermometer code  $(th_j, j = 0, 1, ..., 2^{m-1})$  which controls  $2^m$  unary cells, each having  $I_j = 2^{N-m} I_{LSB}$ , to provide the DC output voltage (1.8). Two main reasons for

Figure 1.5: Modified DAC architecture with segmentation, retiming flip-flop, driver, and cascode transistors.

segmenting are to ensure DAC monotonicity and reduce large glitches created by the binary mid-code transition, while still marinating a reasonable DAC area [13].

$$V_{out} = R_L \cdot I_{LSB} \left( \sum_{k=0}^{k=N-m-1} b_k \cdot 2^k + \sum_{j=0}^{j=2^m-1} t_j \cdot 2^{N-m} \right)$$

(1.9)

- The binary data (b<sub>k</sub>) and thermometer encoded data (th<sub>j</sub>) are aligned using a retiming flip-flop clocked with a global clock signal (CLK) close to the cell, thereby removing data delay differences up to the DAC buffer cell [10] [13]. Data (b<sub>k</sub>, th<sub>j</sub>) is captured once CLK crosses the clocked transistor threshold, generating a differential signal (P, P̄) after a CLK to Q delay. The flip-flop also removes data-dependent jitter occurring from the logic delay differences in the thermometer decoder.

- A differential driver circuit is used to buffer the data (P, P̄), removing clock feedthrough, and providing M<sub>3,4</sub> with fast transition time (τ<sub>b<sub>k</sub></sub>), reduced voltage swing (ΔV<sub>b<sub>k</sub></sub>), and optimal crossover point (V<sub>cross</sub>), which reduced glitch feedthrough errors and output duty cycle errors (Δd<sub>out,i</sub>) [10]. For instance, when V<sub>cross</sub> is set below the V<sub>T</sub> of M<sub>3,4</sub>, both switch pairs are simultaneously turned off. This causes M<sub>1</sub> to turn

off, generating a large negative glitch on the differential common source node  $(V_{cm_k})$ and requiring time for the current source to turn back on. If the  $V_{cross}$  is set above the  $V_T$ , a positive glitch at  $V_{cm_k}$  occurs.

Although the addition of retiming flip-flops and drivers mitigates many timing errors in the data path, they also contribute their own time delay and duty cycle errors. These errors can be reduced by choosing the appropriate architecture and following careful design practices. For example, multiple retiming flip-flop stages can be used to reduce data dependent jitter (DDJ) in the latch element [14]. Current mode logic (CML) latches and buffers are often utilized to achieve faster switching speed while providing low amplitude voltages that reduce glitch feedthrough [15]. Although CML draws more current, it induces less switching supply noise than that of full swing CMOS circuits [16] [17]. However, any mismatch in the clock distribution tree or CML circuit will add to the output delay errors ( $\Delta t_{out,r/s}$ ) [18] and output duty cycle errors ( $\Delta d_{out,r/s}$ ), respectively [19]. Figure 1.6 summarizes the output errors and parameters created by the *k*-binary and *j*-thermometer cells.

In addition to the aforementioned circuit techniques, careful layout design should be followed. For example, larger line widths are used to reduce  $R_M$  [20]. Tree structures, which provide equal routing impedance and electrical length, reduce the spread of systematic mismatch [14] [21]. Additionally, common-centroid floorplans [22] and pre-fabrication switching schemes [23], [9] spatially average systematic errors.

Figure 1.6: Summary of (a) intrinsic errors and (b) mismatch errors.

## **1.3.** Use of CMOS, Bipolar, and III-V Device Materials

CMOS scaling has benefited designs by providing increased transistor  $f_T$ , reduced device capacitance, reduced power, and large scale integration. However, when scaling into the nanometer range, transistors have increased process mismatch [24] and reduced output impedance [25] that present a challenge in maintaining high yield in currentsteering DACs. Emerging device technologies, such as bipolar junction transistors (BJTs) and more recently DARPA's COSMOS and DAHI program integration of III-V with CMOS silicon, allow high performance DACs to be designed. These technologies offer much higher  $f_T > 350$  GHz and output impedance, but suffer from increased switching power consumption, limited device yield, and self-heating. Often DAC designs opt for a mixed design integrating CMOS and bipolar or III-V. This integration capability lends itself well to allowing designers to optimize the transistor for the desired function [26].

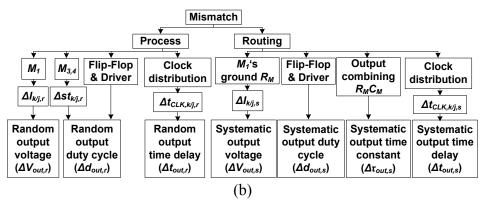

### **1.3.1. CMOS Technologies**

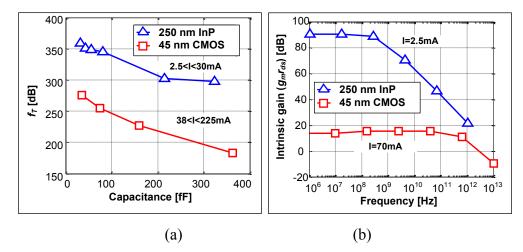

To illustrate the benefits and limitations of CMOS, several simlations are performed across 180nm, 90nm, and 65nm CMOS process technologies. The transistor impedance of an NMOS device<sup>18</sup> is simulated across process technology and shown in Figure 1.7(a). While the results indicate a slight improvement in DC output impedance from 180nm to the 90nm process, there is a significant degradation in DC output impedance when moving from 90nm to the 65nm process. However, the impedance at high frequencies is seen to improve. This is attributed to the fact that a smaller device (therefore smaller drain capacitance) is used to draw the same current, as process scales. Current and timing mismatch are obtained next using a 50-point Monte-Carlo simulation. Figure 1.7(b) plots the current mismatch  $(\sigma \Delta I/I)$  of identical area NMOS transistors<sup>19</sup>. The transistor starts with a 1x area device and scales up to 10x and  $100x^{20}$ . As shown, technology scaling has little or no effect on the overall current mismatch error. The only room for improvement are to increase  $V_{GS} - V_T$ , or the area of the transistor. While increasing  $V_{GS} - V_T$  is limited by headroom requirements, increasing the transistor size is limited by area Figure 1.7(c) plots the switching time mismatch with respect to the constraints.

<sup>&</sup>lt;sup>18</sup>  $V_{GS} - V_T = 100 \text{ mV}$ ,  $L = 1 \mu \text{m}$ , and W is scaled to provide a current  $I = 70 \mu \text{A}$ . <sup>19</sup>  $V_{GS} - V_T = 100 \text{ mV}$ .

$<sup>^{20}</sup>$  The transistor area of 1x means the same area transistor for 65nm, 90nm, and 180nm. Each process uses a minimum L, while W is scaled to provide the same area.

Figure 1.7: CMOS output impedance and mismatch. (a) DAC current source impedance across technology (b) Current mismatches and (c) switching time mismatch across CMOS process technologies.

switching time constant  $(\sigma \Delta st / \tau_{out})$  for different binary cells  $(k=0, 2, \text{ and } 4)^{21}$ . As shown, relative timing accuracy diminishes for scaling CMOS devices.

# 1.3.2. BiCMOS and III-V Technologies

In highly analog circuits such as DACs, higher bias currents are needed to obtain faster switching speeds (i.e. higher  $f_T$ ). Nanometer CMOS transistors are shown to have a high  $f_T$  in some situations reaching that of III-Vs but require multiple interconnected devices to handle large current densities resulting in additional capacitance and reduced usable device  $f_T$ . As shown in Figure 1.8(a-b), InP offers much higher  $f_T$  and intrinsic gain  $(g_m r_{ds})$  with smaller bias currents relative to CMOS. Similarly, bipolar transistors offer higher  $f_T$  and intrinsic gain than CMOS. Therefore, using bipolar or III-V devices as the cascode and switch pair yields higher output impedance and faster switching. CMOS transistors are favored for the current sources since current matching and scaling is

<sup>&</sup>lt;sup>21</sup> For binary cell k=0, a minimum W and L are used with  $I_{LSB} = 2\mu A$ .

Figure 1.8: InP and CMOS (a)  $f_T$  and (b) gain vs. frequency.

directly achievable [27]. Silicon technologies have benefited from the decades of commercial resources in developing the infrastructures, teams, models, and design and test methodologies. Silicon also offers very high-levels of integration with transistor counts in the billions and available scaling based on device size and bias values. Capability for large scale integration of III-V technologies is a recent development and is well behind CMOS in scaling. For example, only discrete device size of InP transistors are available in PDKs. Therefore to provide the correct current scaling between the binary DAC cells a designer would have to compensate for the lack of scaling by relying on a hybrid architecture utilizing an *R2R* resistor ladder in conjunction with current steering cells to realize binary-weighted currents [28].

# Chapter 2: Statistical Modeling for Current-Steering DAC

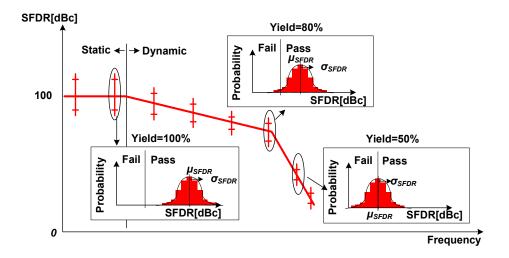

The effects of intrinsic and mismatch error sources on DAC SFDR is investigate in this chapter. While intrinsic effects are uncovered during nominal simulations, mismatch errors require several steps to discover. For instance, process mismatch errors create a statistical variance ( $\sigma_{SFDR}^2$ ) in SFDR, whose mean ( $\mu_{SFDR}$ ) deteriorates as operation frequency increases, limiting device yield (Figure 2.1). Monte Carlo (MC) simulations are used to determine the process mismatch induced loss in DAC performance, requiring 100's of runs per frequency point to accurately model yield. Often, the DAC design is iterated several times until the MC simulated yield is acceptable. To uncover layout mismatch, the extracted layout design must be simulated. This often leads to several redesigns in layout until optimal performance is reached. MC and post layout extraction

Figure 2.1: Nonlinearity in the DACs conversion process and its effect on SFDR yield.

demand rigorous DAC design and simulation testing to meet SFDR yield, which has motivated research focused on characterizing the current-steering DAC as well as simulation models to predict its behavior, shortening design and simulation testing time.

Equation based analyses have been developed to predict theoretical DC static (i.e. integral nonlinearity (INL)) yield using the current source mismatch variance ( $\sigma \Delta I_{k,j}$ ) as the variable. In [29], the probability of current source mismatch is used to determine the INL yield of a binary DAC. In [30], a Brownian-Bridge-based analysis is used to calculate binary and thermometer DAC INL yield. [31], builds on these ideas and provides the most accurate prediction of INL yield for an arbitrary segmented DAC using an empirically-fitted model.

While these equations predict low frequency yield, they fail to predict yield limited by dynamic amplitude and timing errors. A rigorous attempt at equating DAC distortion to each source of error is presented in [7], including derivation of the average signal-to-distortion ratio originating from output time constant errors ( $\Delta \tau_{out,i}$ ) and random delay mismatch ( $\Delta t_{out,r}$ ). However, it fails to provide the SFDR spread or yield outcome.

In contrast, simulation based models abstract DAC components into mathematical and behavioral descriptions to capture dynamic performance while reducing simulation time. Mathematical HDL blocks are used in [32] to model the DAC INL, output glitches, and settling time. The INL performance of the model is validated against a 10-bit DAC 100-point MC simulation. Wavelet theory is used in [33] to generate a series of filtered voltage pulses which capture the DAC DC voltage steps, glitches, and settling performance. It is validated with an 8-bit DAC, comparing INL and SFDR at 10 kHz. A

series of 1-bit behavioral DAC models in [34] are filtered through a nonlinear equation to simulate amplitude mismatch and subsequently low pass filtered to simulate settling errors. An ideal differential switch and RC equivalent current source are used to model the DAC cells in [35] with delay mismatches inserted between the switches to model random delay mismatch ( $\Delta t_{out,r}$ ). The model SFDR without delay mismatch is confirmed with a 6-bit DAC operating at 400 MHz and 10-bit DAC operating at 200 MHz. Then delay mismatches are generated from a generic set of 23 random timing distributions to show the effect on SFDR spread, but results are not verified with a MC simulation.

Due to these shortcomings, a new simulation model for the current-steering DAC architecture is developed here that simultaneously predicts SFDR yield in the GHz operating range and provides simulation speedup by abstracting non-critical circuits to behavioral models. The model captures process variation induced DAC cell mismatch via current, timing, and voltage offset blocks at specific circuit nodes. A statistical modeling methodology that accounts for process mismatch is developed which predicts the SFDR yield in significantly less (on the order of DAC bits- N) simulation runs by populating the offset blocks with a set of deterministic mismatch distributions. In total this modeling methodology allows a simulation speedup of three orders of magnitude.

## 2.1. The Proposed DAC Model

A new DAC model is proposed that accurately captures intrinsic and mismatch performance, without requiring 100's of MC simulations. The proposed model accomplishes this through a hybrid modeling approach. Noncritical transistors are modeled with simulation efficient Verilog-A blocks, while transistor mismatches are captured with parameterizable offset blocks fed with a deterministic distribution that covers the SFDR spread. The model synthesis and simulation is automated using MATLAB and Cadence ocean scripts to reduce setup time. See Appendix A for the MATLAB and Verilog-A codes.

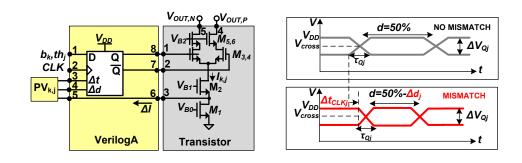

## 2.1.1. Hybrid DAC model

While simulation of a full transistor DAC design is the most accurate, it requires the greatest amount of time to compute. Using a Verilog-A behavioral DAC model is fast to simulate but inaccurate. The proposed model combines transistor and Verilog-A blocks to capture the DAC inherent and transistor mismatch performance accurately and in the most time efficient manner. Identifying which blocks can be modeled involves examining how the non-idealities propagate throughout the DAC data chain.

#### 2.1.1.1. Capturing Intrinsic Performance

The binary-to-thermometer decoder generates data dependent jitter that is removed by the following retiming flip-flop, allowing it to be represented with a Verilog-A decoder without losing simulation accuracy. The retiming flip-flop delays the data to the driver by the CLK - to - Q delay ( $t_{CLK}$ ) and generates clock feedthrough that is minimized by the following driver, allowing it to be represented with a Verilog-A flip-flop with a delay of  $t_{CLK}$ . The driver generates data with a specific voltage swing ( $\Delta Q_{k,j}$ ), transition time ( $\tau_{Q_{k,j}}$ ), and cross over point ( $V_{cross}$ ), allowing it to be modeled with a Verilog-A block with controls of  $\Delta Q_{k,j}$ ,  $\tau_{Q_{k,j}}$ , and  $V_{cross}$ . The Verilog-A retiming flip-flop and driver are combined into one Verilog-A retiming logic block with several input parameters. The DAC cell consists of operating region dependent impedance varying transistors with complex switching behavior. The switch pair  $(M_{3,4})$  and cascode  $(M_{5,6})$  are kept in the model as BSIM transistors to accurately account for impedance variation and output dependent sampling delay. Although the cascoded current source can be modeled with an equivalent *RC* circuit [35], it only offers a speedup of 1.14x compared with a transistor one and requires measurement time to extract the *R* and *C* of each cell. It also fails to capture the dynamic switching glitches which couple to the current source bias node  $(V_{B0})$ . For these reasons the cascoded current source is kept as BSIM transistors in the model.

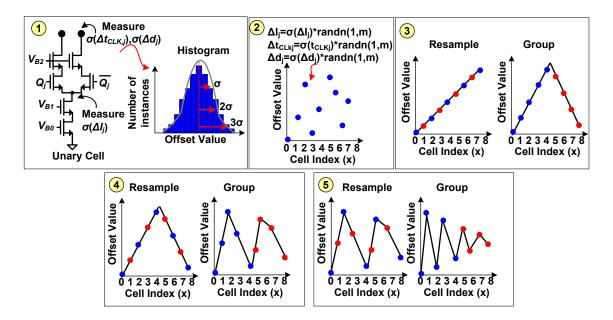

#### 2.1.1.2. Capturing Mismatch Performance

Mismatches arise in the clock distribution, retiming flip-flop, driver, and DAC cell. Consider the accumulate mismatch effects in the data path coming from the clock distribution, retiming flip-flop, and driver. In this case, mismatch in the final signal  $(Q_{k,j})$ controlling the switch pair  $(M_{3,4_{k,j}})$  is what matters. The  $Q_{k,j}$  mismatches that will affect the DAC SFDR are the clock delay error  $(\Delta t_{CLK_{k,j}})$  and the duty cycle error  $(\Delta d_{Q_{k,j}})$ . Now consider the mismatches in the DAC cell. There is mismatch in current  $(\Delta I_{k,j})$  and mismatch in  $M_{3,4_{k,j}}$  sampling time  $(st_{k,j})$  which causes a duty cycle error  $(\Delta d_{M_{3,4,k,j}})$ . The proposed model includes these mismatches as Verilog-A offsets, as displayed in Figure 2.2(a). The delay error  $(\Delta t_{CLK_{k,j}})$  and duty cycle error  $(\Delta d_{k,j} = \Delta d_{Q_{k,j}} + \Delta d_{M_{3,4,k,j}})$  are captured in the Verilog-A retiming logic output, while the current mismatch  $(\Delta I_{k,j})$  is modeled by adding/subtracting current from  $M_{1_{k,j}}$ 's drain node. The retiming Verilog-A response, plotted in Figure 2.2(b), depicts how the data arrives to  $M_{3,4_{k,j}}$  with and without the timing and duty cycle mismatch. The mismatch variables (2.1) per cell (k, j) are set individually to any desired distribution, as displayed in Figure 2.2(c) for the unary cell array.

$$PV_{k,j} = (\Delta t_{CLK_{k,j}}, \Delta d_{k,j}, \Delta I_{k,j})$$

(2.1)

In most DAC segmentations, the SFDR is dominated by the unary cells. Therefore the modeling approach focuses on modeling the unary cell mismatches. SFDR yield can be predicted by populating the unary offset blocks with a deterministic set of mismatch values which anticipate the majority of SFDR scenarios. The modeling methodology

Figure 2.2: Proposed hybrid DAC cell model. (a) Single cell. (b) Retiming Verilog-A code transient response (c) Arrayed unary cells.

which accurately predicts the statistical SFDR spread and yield is explained next.

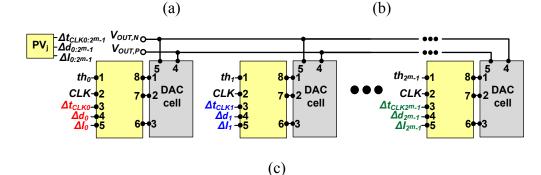

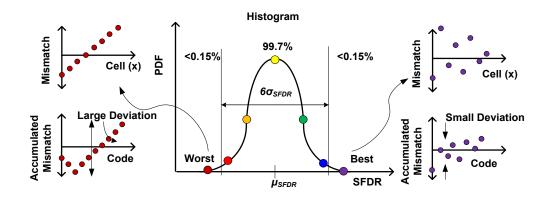

### 2.1.2. Rapid Mismatch Modeling Method

The proposed mismatch modeling attains a sampled set of SFDR values from the SFDR PDF to cover the  $6 - \sigma$  SFDR spread where 99.7% of the SFDR values lye (Figure 2.3). The SFDR is bound by a worst case and best case mismatch distribution related to the correlation of mismatches in sequentially switching cells. In a worst case SFDR scenario, neighboring cells have a high correlation in mismatch values resulting in a linear error distribution [31], accounting for <0.15% of SFDR cases. In a best case SFDR the accumulated error is cancelled to the maximum [36] [37], accounting for <0.15% of SFDR values. In between these two scenarios, there exist a set of distributions that provide the  $6 - \sigma$  SFDR spread. The procedure for determining the distributions involve measuring the  $PV_j$  (2.1)  $\sigma$ 's and ordering the mismatch per cell to provide a desired mismatch distribution. This procedure is outlined in Figure 2.4 for 8 unary cell mismatch values (m = 3) and described below.

Figure 2.3: Sampling theory for estimating SFDR

- **(**) The  $PV_j \sigma$ 's are extracted from measured data by running a 200-point MC simulation on a single full transistor implementation of a DAC unary cell including the retiming flip-flop and driver. In particular, delay  $(\sigma \Delta t_{CLK_j})$  and duty cycle mismatch  $(\sigma \Delta d_j)$  is measured at the output node, while current mismatch  $(\sigma \Delta I_j)$  is measured at the switch pair common source node. Since each unary cell consist of the same transistor properties and biasing conditions, they will statistically have the same mismatch properties. Binary cell mismatch can be modeled in a similar manner, but excluded in this study due to their small contribution to the overall DAC linearity. This 200point MC run takes approximately  $1/10^{\text{th}}$  the simulation time compared with a 1point full MC DAC run.

- **2** The  $\sigma$  values are used to create a random Gaussian distribution in MATLAB.

- <sup>3</sup> The random number set is ordered least to greatest, simulating a worst case SFDR.

Figure 2.4: Capture of process mismatches in the DAC and mismatch reordering process.

This scenario is unlikely to occur within the  $6 - \sigma$  spread. What is more probable is a triangular distribution, formed by sampling every other point in the linear distribution and grouping the odd samples followed by the even samples.

(4-) The resample and group process repeats until the mismatch in one cell is close in amplitude and opposite to the mismatch in the following switched cell.

In this example, 3 distinct error distributions for  $\Delta t_{Q_{k,j}}$ ,  $\Delta d_{k,j}$ , and  $\Delta I_{k,j}$  exist. The mismatch values are plugged into the offset blocks resulting in the unique delay mismatch  $(t_{CLK_j} + \Delta t_{CLK_j})$ , duty cycle mismatch  $(d_j + \Delta d_j)$ , and current mismatch  $(I_j + \Delta I_j)$ . Each one of the 3 distribution profiles must be simulated in separate runs to model an accurate SFDR variance, requiring 3 simulation runs total. From these 3 runs the max (*SFDR<sub>max</sub>*), mean (*SFDR<sub>mean</sub>*), and min (*SFDR<sub>min</sub>*) SFDR are calculated. The  $\sigma$ (*SFDR*) is determined assuming a  $6 - \sigma$  spread from the *SFDR<sub>max</sub>* to *SFDR<sub>min</sub>* where 99.7% of the points fall into

$$\sigma(SFDR) = \frac{SFDR_{max} - SFDR_{min}}{6}$$

(2.2)

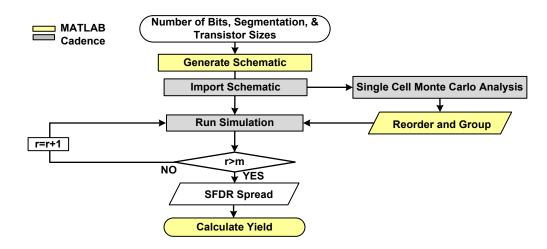

### 2.1.3. Model Synthesis and Simulation

The proposed model utilizes the processing capabilities of MATLAB and the simulation capabilities of Cadence to automate the synthesis and simulation. As outlined in Figure 2.5, MATLAB is used to generate the model netlist given the number of bits (N), segmentation number (m) and transistor sizes [38]. The netlist is then imported into the Cadence environment, liked to a specified PDK, and used to generate a hierarchical schematic. The data properties for the Verilog-A retiming code  $(t_{CLK}, \Delta Q_{k,j}, \tau_{Q_{k,j}}, V_{cross})$

Figure 2.5: Proposed model synthesis and simulation using MATLAB and Cadence

are set to their specified value. The mismatch values (2.1) are modeled as parameterizable blocks whose value is read from a mismatch distribution file generated in MATLAB. A test bench is created in Cadence's analog design environment (ADE) and a simulation is ran, each time selecting the offset distribution file and recording the SFDR, which is subsequently used in MATLAB to calculate the DAC yield.

# 2.2. Experimental Results

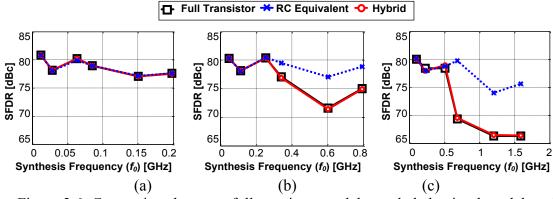

A 10-bit DAC segmented with 6-thermometer bits is implemented in a 65nm CMOS process and used to verify the model. Full transistor simulations, including the retiming flip-flop and driver, are compared with the proposed model and also with the RC equivalent model developed in [35]. The results are shown in Figure 2.6(a)-(c) for  $f_{CLK}$ = 500MHz, 2GHz, and 4GHz. Although the RC model reduces simulation time by ~40x that of a full transistor design, the accuracy of the model degrades as the sampling frequency increases ( $f_{CLK}$ >2GHz) with input frequencies ( $f_0$ >200MHz) due to the use of

Figure 2.6: Comparison between full transistor model, purely behavioral model, and proposed hybrid model DAC SFDR across operating frequencies for (a)  $f_{clk}$  =500MHz (b)  $f_{clk}$  =2GHz and (c)  $f_{clk}$  =4GHz

ideal switches. The proposed hybrid model is accurate within 1 dB SFDR across all operating frequencies, while providing a speedup of  $\sim$ 10x that of a full transistor design.

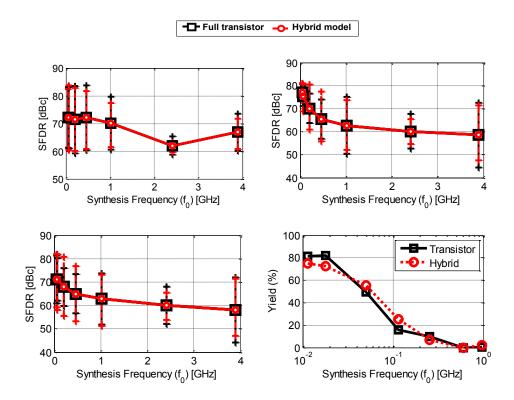

The DAC under investigation is found to have the following thermometer mismatch values  $(\sigma \Delta t_{CLK_j}) = 1.6$ ps,  $(\sigma \Delta d_j) = 1.5$ ps and  $(\sigma \Delta I_j) = 590$ nA. In this example a total of 6 distributions exist and must be simulated in 6 separate runs. From these 6 runs the *SFDR<sub>mean</sub>* and  $6 - \sigma(SFDR)$  spread are calculated and plotted in Figure 2.7 along with the measured values from a 200-point full transistor Monte-Carlo simulation. The data is broken up into 3 cases to verify the model accurately predicts the separate and combined effect of amplitude and timing mismatch. The first simulation includes mismatches on the current source transistor only and corresponding current offset in the model, Figure 2.7(a). The next simulation considers the timing mismatches only (Figure 2.7(b)), while last simulation, Figure 2.7(c), is a full MC run with all mismatches included in the DAC. Figure 2.7(d), shows the achievable yield for an SFDR>67dB for the measured and modeled DAC. By choosing the appropriate 6 distributions, the model is accurate to 1 dB, reducing simulation time by ~330x per frequency point.

Figure 2.7: Simulated DAC full transistor and hybrid model. SFDR vs. frequency with (a) current mismatch, (b) timing mismatch (c) all mismatches. (d) Yield vs. frequency for  $SFDR \ge 67.8 \text{ dB}$  with all mismatches.

## 2.3. Conclusion and Model Uses

A new modeling methodology that accurately captures DAC performance at low and high operating frequencies was developed. The model generation and simulation is automated using MATLAB and Cadence to provide rapid analyses. The model also accounts for process mismatches by including timing and current offsets blocks. In general, this model can be useful in studying different DAC architectures and effects of statistical mismatch and systematic offset distributions. It can also aid in the study and development of novel calibration techniques. In the following chapter compensation and calibration techniques are discussed and compared using a baseline 12-bit DAC (Figure

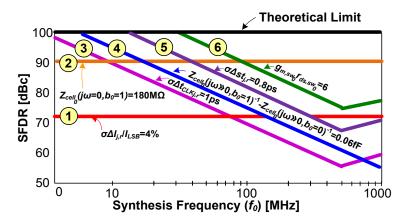

1.5) segmented with 6-thermometer designed in a 65nm process operating at  $f_{CLK} = 2$ GHz. The hybrid model is used to capture its intrinsic and mismatch performance. Ignoring systematic effects induced by layout, the resultant SFDR is plotted in Figure 2.8 and exhibits the classical resolution versus speed tradeoff [10] [20] [39] [40] [41]. The sources of SFDR degradation are as follows:

- (1) Random output voltage errors  $(\Delta V_{out,r})$ , induced by current source mismatch  $(\Delta I_{k_r})^{22}$ , result in flat 3<sup>rd</sup> order harmonic distortion. The simulated  $-3\sigma$  SFDR is ~70 dBc<sup>23</sup> for an  $M_1$  LSB area  $(W_{1,k=0}L_{1,k=0} = 12\mu\text{m}\times8\mu\text{m} = 19,000W_{min}L_{min})$ . Note the total current source area for a 12-bit DAC using this LSB size would be ~0.4mm<sup>2</sup>. This area grows exponentially for every 3dB increase in SFDR. For example, to meet a 90dBc SFDR,  $W_{1,k=0}L_{1,k=0} = 1 \times 10^6 W_{min}L_{min}$ , and the total current source area for a 12-bit DAC would be prohibitive at ~20mm<sup>2</sup>.

- <sup>(2)</sup> Cell resistance modulation generates intrinsic output voltage errors  $(\Delta V_{out,i})^{24}$  that have little impact on SFDR due to the use of cascoding, limiting SFDR~90dBc with flat 3<sup>rd</sup> order harmonic distortion.

- <sup>3</sup> Random output delay errors (Δ*t*<sub>out,r</sub>), induced by clock mismatch (Δ*t*<sub>CLK,j,r</sub>)<sup>25</sup>, result in 2<sup>nd</sup> order harmonic distortion with a -20dB/decade roll off. Note that a 1-σ clock mismatch of 1ps is enough to limit  $-3\sigma(SFDR) \approx 55$ dBc at 500MHz.

$<sup>^{22} \</sup>sigma(\Delta I_{i,r}/I_{LSB}) = 4\%$  obtained from Monte Carlo simulation.

<sup>&</sup>lt;sup>23</sup> Applying a linear triangular error distribution represents the  $-3\sigma SFDR$  within  $\pm 1$ dB when compared with a 200-point Monte Carlo simulation.

<sup>&</sup>lt;sup>24</sup>  $Z_{cell_0}(j\omega = 0, b_0 = 1) = 180M\Omega$ . Simulated with all mismatch errors omitted.

<sup>&</sup>lt;sup>25</sup> Mainly contributed by mismatch in the clock buffers where  $\sigma(\Delta t_{CLKj,r}) = 1$  ps is obtained from Monte Carlo simulation.

Figure 2.8: Impact of various intrinsic and mismatch errors on SFDR across frequency for the 12-bit baseline DAC operating at  $f_{CLK} = 2$ GHz.

- (4) Cell capacitance modulation generates intrinsic time constant errors  $(\Delta \tau_{out,i})^{26}$ , resulting in 3<sup>rd</sup> order harmonic distortion which falls off at -20 dB/decade.

- **(5)** Random duty cycle errors  $(\Delta d_{out,r})^{27}$ , induced by switch time mismatch  $(\Delta st_{j,r})$ , results in 2<sup>nd</sup> order harmonic distortion that rolls off at -20dB/decade.

- 6 Intrinsic duty cycle errors  $(\Delta d_{out,i})^{28}$ , attributed to switch time modulation, result in 2<sup>nd</sup> order harmonic distortion that falls off at -20dB/decade.

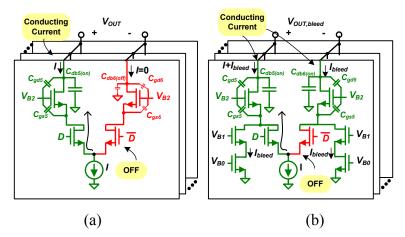

Note that the reversal in SFDR at  $f_{CLK}/4$  is expected since the second order distortion terms alias to lower frequencies and experiences greater attenuation [11].

Overall, the modified DAC architecture (Figure 1.5) provides a solid foundation for high-performance. However, several intrinsic and mismatch errors degrade SFDR well below the theoretical limit of 100dBc. Moreover, systematic layout mismatch will add to

<sup>&</sup>lt;sup>26</sup> Simulated with all mismatch errors omitted.

$<sup>^{27} \</sup>sigma(\Delta st_{j,r}) = 0.8$  ps is obtained from Monte Carlo simulation of  $M_{3,4}$ . All other intrinsic and mismatch errors are eliminated by setting  $R_L = 0$  and using the output current to measure SFDR.

<sup>&</sup>lt;sup>28</sup> Simulated by eliminating  $\Delta \tau_{out,i}$  effects using a bleeder current of  $10\mu A$  (section 3.1.3) and omitting all mismatch errors.

the output voltage and time delay errors, further degrading SFDR. In general, compensation techniques are used to address intrinsic limitations such as time constant  $(\Delta \tau_{out,i})$  and duty cycle  $(\Delta d_{out,i})$  errors, while calibration is employed to correct unary cell random and systematic mismatch such as current  $(\Delta I_{j,r/s})$ , delay  $(\Delta t_{j,r/s})$ , duty cycle  $(\Delta d_{j,r/s})$  errors.

# **Chapter 3:** Compensation and Calibration Techniques

Compensation and calibration are two distinct correction techniques applied to a DAC at various circuit nodes to improve static and/or dynamic linearity. Compensation is an open loop scheme that blindly (i.e. without measurement) minimizes the code-dependency of errors. In contrast, calibration is a closed loop technique that senses DAC errors and tunes the circuit accordingly. The following sections provide an overview of compensation and calibration techniques and how they have evolved over time. For comparison purposes, key correction techniques are simulated using the 12-bit baseline DAC (section 2.3).

# **3.1.** Compensation Techniques

In general, compensation techniques are used to minimize the correlation between input code and resulting DAC error by: 1) resampling the output signal, 2) altering the sampling clock, 3) modifying the cell structure, or 4) dynamically rearranging the switching sequence of the DAC cells.

## **3.1.1. Deglitching**

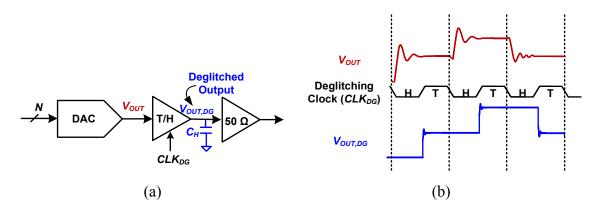

A typical method to remove switching-dependent errors<sup>29</sup> is to resample the output after it has settled using a track-and-hold (T/H) circuit [42], depicted in Figure 3.1(a).

<sup>&</sup>lt;sup>29</sup> This includes timing errors ( $\Delta \tau_{out,i}, \Delta \tau_{out,s}, \Delta t_{out,r/s}$ ), duty cycle ( $\Delta d_{out,i}, \Delta d_{out,r/s}$ ), glitch feedthrough, and DDJ.

Figure 3.1: Typical deglitching compensation. (a) Block diagram. (b) Timing diagram. Utilizing an additional sampling clock, the deglitcher tracks and holds the DAC output only after it has settled to a steady state (Figure 3.1(b)). Whereas deglitching allows for relaxed retiming clock distribution and data path design, the T/H circuit linearity and settling speed ultimately limits the DAC performance [43]. To overcome the speed limitation, a diode-bridge current-steering deglitcher has been proposed with the drawback of increased power consumption [28]. In addition, the deglitcher is followed by a high-linearity output buffer to interface with off-chip circuitry, affecting linearity and settling time.

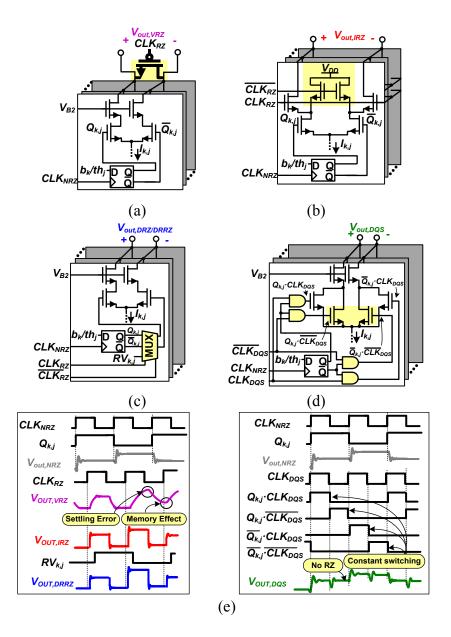

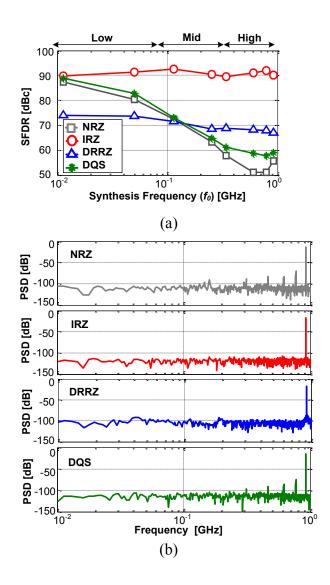

## 3.1.2. Return-to-Zero (RZ) and Differential Quad Switching (DQS)

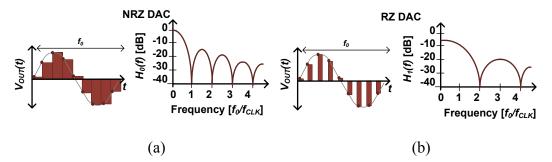

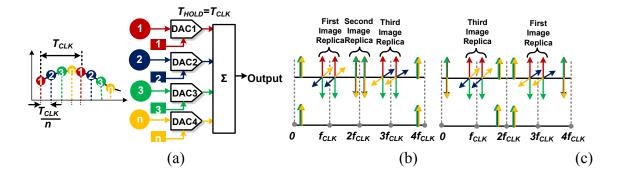

The return-to-zero (RZ) technique was initially conceived to perform deglitching without the drawbacks of the T/H circuit [43]. In general, RZ DACs utilize an additional clock ( $CLK_{RZ}$ ) that returns the output to a known state every sample period, removing the data dependency of switching glitches. Furthermore, by ensuring  $Q_{k,j}$  and  $\overline{Q_{k,j}}$  transitions in the reset phase ( $CLK_{RZ} = 0$ ), cell data path delay errors do not propagate to the output. Although data dependencies are mitigated, the RZ output is two times more sensitive to

Figure 3.2: Sampled sinusoid ( $V_{out}$ ) and frequency-domain response ( $|H_i(f)|$ ) for the (a) NRZ and (b) RZ DAC. random clock jitter since it transitions on both rising and falling clock edge [44]. Another drawback of RZ DACs is the reduction of the output signal power at DC by 6dB<sup>30</sup>, as depicted in Figure 3.2. However, it also shifts the first null to  $2f_{CLK}$ , resulting in a flatter response in the first Nyquist zone.

Initial designs implemented RZ in voltage-mode (VRZ) by inserting a single switch between the DAC differential outputs, as pictured in Figure 3.3(a) [43]. This requires only a single clock tap, allowing for a simple clock network. During the reset phase, the DAC differential branches are shorted together which results in zero current flow through  $R_L$ , effectively setting  $V_{out,VRZ}$  to zero. Based on the switch size, either the nonlinear switch ON resistance or capacitance dominates the output time constant. As a result, the output may not fully charge to its desired value (i.e. settling error) or fail to completely reset to zero (i.e. memory effect), as illustrated in Figure 3.3(e). This data-dependent error ultimately limits the achievable SFDR. VRZ has demonstrated an SFDR of 74dBc ( $f_0$ =8.5MHz,  $f_{CLK}$ =100MHz) for a 14-bit DAC designed in 0.8µm CMOS [43].

<sup>&</sup>lt;sup>30</sup> Assuming a 50%  $CLK_{RZ}$  duty cycle.

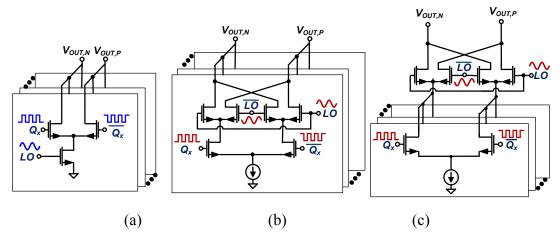

Figure 3.3: Modified DAC architecture with (a) voltage RZ (VRZ), (b) current RZ (IRZ), (c) digital RZ (DRZ/DRRZ), and (d) differential quadrature switching (DQS). (e) Time domain waveforms for NRZ, VRZ, IRZ, DRRZ, and DQS.

In order to break the speed-linearity tradeoff for the single RZ switch, a current-mode RZ (IRZ) approach was proposed to incorporate a small RZ switch in the current path of each cell, as shown in Figure 3.3(b) [45]. During the reset phase, all cell currents are redirected to the power supply and zero current flows through  $R_L$  (Figure 3.3(e)). Note

that unlike VRZ, the switched current-mode IRZ maintains the inherent speed of the current-steering architecture at the expense of a more complex RZ clock distribution. Specifically, this requires the RZ clock to be routed to each cell individually, and hence, introduces its own mismatch errors. This approach has been favored for its high-frequency operation, demonstrating an SFDR of 57dBc ( $f_0 = 0.76$ GHz,  $f_{CLK} = 1.6$ GHz) for a 12-bit DAC designed in a 1µm GaAs HBT technology, wherein an increase of 12dBc is obtained relative to NRZ [45].

RZ was later proposed in the digital domain (DRZ) to alleviate analog complexity with additional overhead in the data path. DRZ was initially conceived solely for bandwidth extension [46], and later implemented to improve the dynamic DAC behavior using a technique termed digital random RZ (DRRZ) [47]. In DRZ, the cell data is multiplexed with a reset value  $(RV_{k,j})$ , outputting  $b_k$ ,  $th_j$  during the positive clock cycle  $(CLK_{RZ}=1)$ and  $RV_{k,j}$  during the negative clock cycle ( $CLK_{RZ}=0$ ) (Figure 3.3(c)). Note that for DRZ,  $RV_{k,j}$  is kept constant per clock cycle at a logical '1' for half the DAC cells and '0' for the other half of the cells such that the output  $(V_{out,DRZ})$  returns to zero during the negative clock cycle (Figure 3.3(e)). Given that the cell only switches when  $b_k$ ,  $th_i \neq b_k$  $RV_{k,i}$ , the switching glitches remain correlated with the input code while occurring at twice the rate of NRZ, resulting in lower SFDR than NRZ [47]. To address these shortcomings, DRRZ proposes a pseudo-random  $RV_{k,j}$  which changes during each reset phase, decorrelating the switching transitions from the input code [47]. Although randomizing  $RV_{k,j}$  improves SFDR by spreading the distortion across frequency, it incurs a small penalty in the DAC noise floor [47]. Additionally, since DRRZ is applied before

the DAC switch pair, the cell dependent switching mismatch errors remain uncompensated. DRRZ has demonstrated an SFDR of 57dBc ( $f_0=0.8$ GHz,  $f_{CLK}=1.6$ GHz) for an 8-bit DAC in 90nm CMOS, showing a 14dB improvement over DRZ for the same design [47].

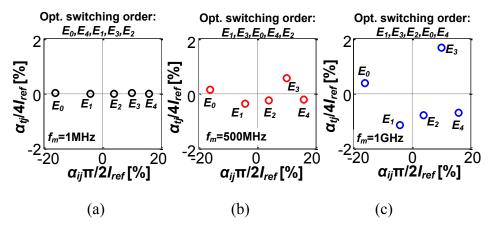

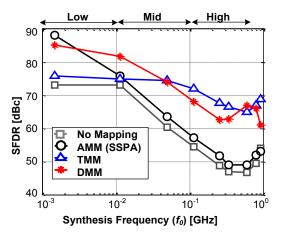

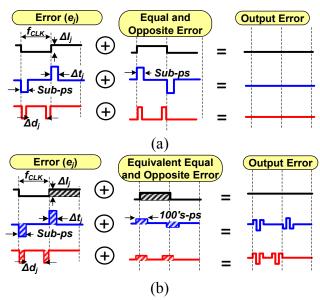

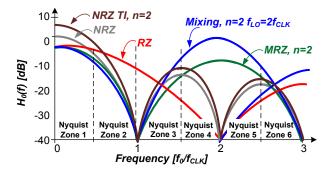

As clock frequency increases, the finite slewing of the narrow RZ output pulse can result in incomplete transitions. This has prompted a technique termed differential quadrature switching (DQS), which does not require the output to return to a reset state, while ensuring uniform cell switching every clock cycle regardless of code [48]. As illustrated in Figure 3.3(d), DQS utilizes four logical signals obtained from the AND operation of input code  $(b_k, th_j)$ , clock  $(CLK_{DQS})$ , and their inverted versions. This can be viewed as two complementary RZ operations where the output voltage ( $V_{out,DOS}$ ) avoids returning to a reset value, thereby incurring zero power loss (Figure 3.3(e)). Additionally, by ensuring constant switching for each cell, irrespective of data transitions, the code dependent glitch error on the common source node (Figure 1.5  $V_{cm}$ ) is removed. However, like DRRZ, the cell dependent switching mismatch errors remain uncompensated. Furthermore, since  $V_{out,DQS}$  does not return to a reset value, intrinsic output time constant and duty cycle errors are not addressed. This technique has demonstrated an SFDR of 67dBc ( $f_0$ =260MHz,  $f_{CLK}$ =1.4GHz) [49] and SFDR of 52dBc  $(f_0=1.5 \text{GHz}, f_{CLK}=3 \text{GHz})$  [50] for a 14-bit DAC in 0.18µm CMOS.