# Accelerating Component-Based Dataflow Middleware with Adaptivity and Heterogeneity

Dissertation

### Presented in Partial Fulfillment of the Requirements for the Degree Doctor of Philosophy in the Graduate School of The Ohio State University

By

Timothy D. R. Hartley, M.S.

Graduate Program in Electrical and Computer Engineering

The Ohio State University

2011

Dissertation Committee: Professor Ümit V. Çatalyürek, Advisor Professor Füsun Özgüner Professor Charles A. Klein

### Abstract

This dissertation presents research into the development of high performance dataflow middleware and applications on heterogeneous, distributed-memory supercomputers. We present coarse-grained state-of-the-art ad-hoc techniques for optimizing the performance of real-world, data-intensive applications in biomedical image analysis and radar signal analysis on clusters of computational nodes equipped with multicore microprocessors and accelerator processors, such as the Cell Broadband Engine and graphics processing units. Studying the performance of these applications gives valuable insights into the relevant parameters to tune for achieving efficiency, because being large-scale, data-intensive scientific applications, they are representative of what researchers in these fields will need to conduct innovative science. Our approaches shows that multi-core processors and accelerators can be used cooperatively to achieve application performance which may be many orders of magnitude above naïve reference implementations. Additionally, a fine-grained programming framework and runtime system for the development of dataflow applications for accelerator processors such as the Cell is presented, along with an experimental study showing our framework leverages all of the peak performance associated with such architectures, at a fraction of the cognitive cost to developers. Then, we present an adaptive technique for automating the coarse-grained ad-hoc optimizations we developed for tuning the decomposition of application data and tasks for parallel execution on distributed, heterogeneous processors. We show that our technique is able to achieve high performance, while significantly reducing the burden placed on the developer to manually tune the relevant parameters of distributed dataflow applications. We evaluate the performance of our technique on three real-world applications, and show that it performs favorably compared to three state-of-the-art distributed programming frameworks. By bringing our adaptive dataflow middleware to bear on supporting alternative programming paradigms, we show our technique is flexible and has wide applicability. To Annie and Charlotte

### Acknowledgments

Graduate school is hardly a solo endeavor, and I am indebted to the following people for their support.

I would like to thank the Dayton Area Graduate Studies Institute and Dr. Elizabeth Downie for providing support for me to be able to focus on my research. The flexibility a fellowship affords was deeply appreciated.

I am grateful to my collaborators Charles Berdanier, AFRL, and Ahmed Fasih for their help drilling radar signal analysis into my head, what little it would hold. I would like to thank Dr. George Teodoro and Professor Renato Ferreira for their collaborations. I would like to thank Professor Manuel Ujaldón and Antonio Ruiz for helping me get interested in GPUs.

I would like to thank Professor Füsun Özgüner for her invaluable support and her committee membership. I am also grateful to Professor Charles Klein for his committee membership, and I wish him well in his impending retirement!

I would especially like to thank Dr. Erik Saule for his constant advice, support, on-point technical criticisms, and his friendship. I owe thanks also to all of the other members of the HPC lab.

I will never be able to thank Professor Ümit Çatalyürek enough for his Herculean support in getting me to this point. There were too many times to count where an encouraging talk lifted me out of yet another motivation black hole. His advice, support, kindness, and friendship will always be truly appreciated.

I'd like to thank my daughter, Charlotte Madeline Lindgren Hartley for her amazing attitude, intelligence, and sense of humor. She has changed my life.

Lastly I'd like to thank Dr. Annie Rose Lindgren for being the best partner anyone could ever hope for. For her steadfast support, advice, patience, and good humor in the face of a difficult situation (dealing with a graduate student husband while being a talented research scientist and an incredible mother), I will forever be in her debt.

### Vita

| January 16, 1980 | Born - High Wycombe, UK                                                                        |

|------------------|------------------------------------------------------------------------------------------------|

|                  | B.S. Electrical and Computer<br>Engineering,<br>New Mexico State University                    |

| 2005-2011        | Graduate Research Associate,<br>The Ohio State University.                                     |

|                  | M.S. Electrical and Computer<br>Engineering,<br>The Ohio State University                      |

|                  | Air Force Research Laboratory /<br>Dayton Area Graduate Studies Ohio<br>Student-Faculty Fellow |

### Publications

T. D. R. Hartley, U. V. Catalyurek, A. Ruiz, F. Igual, R. Mayo, and M. Ujaldon. Biomedical image analysis on a cooperative cluster of gpus and multicores. In *Proceedings of the 22nd Annual International Conference on Supercomputing, ICS 2008*, pages 15–25, 2008.

F. Igual, R. Mayo, T. D. R. Hartley, U. V. Catalyurek, A. Ruiz, and M. Ujaldón. Optimizing co-occurrence matrices on graphics processors using sparse representations. In *Proceedings of the 9th International Workshop on State-of-the-Art in Scientific and Parallel Computing (PARA '08)*, 2008.

H. G. Ozer, D. Bozdag, T. Camerlengo, J. Wu, Y.-W. Huang, T. Hartley, J. D. Parvin, T. Huang, U. V. Catalyurek, and K. Huang. A comprehensive analysis workflow for genome-wide screening data from chip-sequencing experiments. In *Proceedings of 1st International Conference on Bioinformatics and Computational Biology*, volume 5462 of *Lecture Notes in Computer Science*, pages 320–330. Springer, April 2009.

T. D. R. Hartley and U. V. Catalyurek. A component-based framework for the cell broadband engine. In *Proceedings of 23rd International Parallel and Distributed Processing Symposium, The 18th Heterogeneous Computing Workshop (HCW 2009)*, May 2009.

T. D. R. Hartley, A. R. Fasih, C. A. Berdanier, F. Özgüner, and U. V. Catalyurek. Investigating the use of GPU-accelerated nodes for SAR image formation. In *Proceedings of the IEEE International Conference on Cluster Computing, Workshop on Parallel Programming on Accelerator Clusters (PPAC)*, 2009.

U.V. Catalyurek, T. Hartley, O. Sertel, M. Ujaldon, A. Ruiz, J. Saltz, and M. Gurcan. Processing of large-scale biomedical images on a cluster of multi-core cpus and gpus. In W. Gentzsch, L. Grandinetti, and G. Joubert, editors, *High Performance and Large Scale Computing*, volume 18, pages 341–364. IOS Press, 2009.

F. Igual, R. Mayo, T. D. R. Hartley, U. Catalyurek, A. Ruiz, and M. Ujaldon. Exploring the gpu for enhancing parallelism on color and texture analysis. In *Proceedings* of the 2009 International Conference on Parallel Computing (ParCo 2009), 2009.

U. V. Catalyurek, R. Ferreira, T. D. R. Hartley, R. Sachetto, and G. Teodoro. Dataflow frameworks for emerging heterogeneous architectures and its application to biomedicine. In *Scientific Computing with Multicore and Accelerators*. Chapman and Hall / CRC Press, 2010.

T. D. R. Hartley, E. Saule, and U. V. Catalyurek. Automatic dataflow application tuning for heterogeneous systems. In *Proceedings of The 17th International Conference on High Performance Computing (HiPC 2010)*, 2010.

F. Igual, R. Mayo, T. D. R. Hartley, U. Catalyurek, A. Ruiz, and M. Ujaldon. Color and texture analysis on emerging parallel architectures. *International Journal of High Performance Computing Applications*, to appear.

G. Teodoro, T. D. R. Hartley, U. V. Catalyurek, and R. Ferreira. Run-time optimizations for replicated dataflows on heterogeneous environments. In *Proceedings of* the 19th ACM International Symposium on High Performance Distributed Computing (HPDC), 2010.

G. Teodoro, T. D. R. Hartley, U. V. Catalyurek, and R. Ferreira. Optimizing dataflow applications on heterogeneous environments. *Cluster Computing*, to appear.

T. D. R. Hartley, E. Saule, and Ü. V. Çatalyürek. Evaluating support for heterogeneous computing in high-level distributed programming frameworks. In *Proceedings* of The Twentieth International Conference on Parallel Architectures and Compilation Techniques (PACT 2011), 2011, under review.

T. D. R. Hartley, E. Saule, and Ü. V. Çatalyürek. Improving performance of adaptive component-based dataflow middleware. *Parallel Computing*, 2011, under review.

### Fields of Study

Major Field: Electrical and Computer Engineering

# Table of Contents

## Page

| Abstract                                                                                | ii                       |

|-----------------------------------------------------------------------------------------|--------------------------|

| Dedication                                                                              | iv                       |

| Acknowledgments                                                                         | v                        |

| Vita                                                                                    | vii                      |

| Table of Contents                                                                       | x                        |

| List of Tables                                                                          | kiv                      |

| List of Figures                                                                         | xv                       |

| 1. Introduction                                                                         | 1                        |

| <ul> <li>1.1 Motivation</li></ul>                                                       | $1 \\ 3 \\ 6 \\ 8 \\ 14$ |

| I Ad-Hoc High-Performance Dataflow Application Programming<br>for Heterogeneous Systems | 18                       |

| 2. Biomedical Image Analysis on a Cooperative Cluster of GPUs and Multicores            | 19                       |

|                                                                                         | 19<br>22                 |

|            |                                                | 2.2.1 The algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23                                                                                                                                                         |

|------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                | 2.2.2 Major challenges                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 25                                                                                                                                                         |

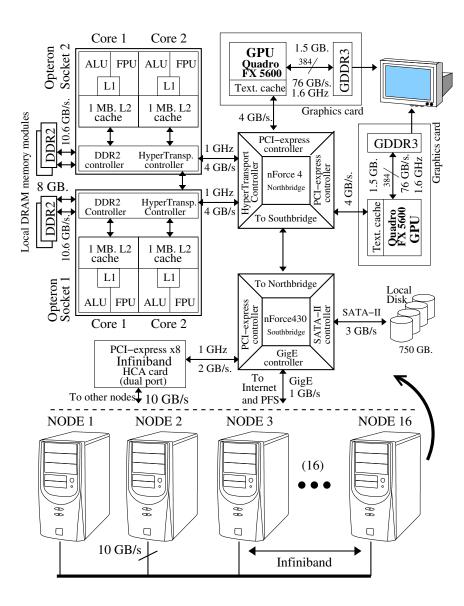

|            | 2.3                                            | GPU Cluster Testbed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26                                                                                                                                                         |

|            | 2.4                                            | Tools and GPU implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 29                                                                                                                                                         |

|            |                                                | 2.4.1 CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29                                                                                                                                                         |

|            |                                                | 2.4.2 Implementation with DataCutter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                                                         |

|            | 2.5                                            | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                                                                                                         |

|            | 2.6                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48                                                                                                                                                         |

| 3.         | Inve                                           | stigating the Use of GPU-Accelerated Nodes for SAR Image Formation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 50                                                                                                                                                         |

|            | 3.1                                            | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                                                                                                                                                         |

|            | 3.2                                            | Overview of Computed Tomography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 51                                                                                                                                                         |

|            | 3.3                                            | Software Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 55                                                                                                                                                         |

|            | 3.4                                            | Implementation Details                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56                                                                                                                                                         |

|            |                                                | 3.4.1 Backprojection with DataCutter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                                                                                                         |

|            |                                                | 3.4.2 Backprojection with GPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 59                                                                                                                                                         |

|            |                                                | 3.4.3 Combining DataCutter and CUDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 60                                                                                                                                                         |

|            | 3.5                                            | Application Experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 61                                                                                                                                                         |

|            | 3.6                                            | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65                                                                                                                                                         |

|            |                                                | n-Performance Dataflow Middleware for Heterogeneous Com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

| put        |                                                | n-Performance Dataflow Middleware for Heterogeneous Com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 68                                                                                                                                                         |

| put:<br>4. | ing                                            | p-Performance Dataflow Middleware for Heterogeneous Com-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                            |

| -          | ing                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                         |

| -          | ing<br>A Co                                    | omponent-Based Framework for the Cell Broadband Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68<br>69                                                                                                                                                   |

| -          | ing<br>A Co<br>4.1                             | omponent-Based Framework for the Cell Broadband Engine<br>Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68<br>69                                                                                                                                                   |

| -          | ing<br>A Co<br>4.1                             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 68<br>69<br>69                                                                                                                                             |

| -          | ing<br>A Co<br>4.1                             | omponent-Based Framework for the Cell Broadband Engine         Introduction         Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters         4.2.1       DataCutter-Lite Architecture and Programming         Model                                                                                                                                                                                                                                                                                                                                     | 68<br>69<br>69                                                                                                                                             |

| -          | ing<br>A Co<br>4.1<br>4.2                      | Introduction       Introduction         Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters         4.2.1         DataCutter-Lite Architecture and Programming         Model         4.2.2         DataCutter for Distributed Multicore Programming                                                                                                                                                                                                                                                                                                        | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> </ul>                                                                         |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3               | omponent-Based Framework for the Cell Broadband Engine          Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> </ul>                                                             |

| -          | ing<br>A Co<br>4.1<br>4.2                      | omponent-Based Framework for the Cell Broadband Engine          Introduction          Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters          4.2.1       DataCutter-Lite Architecture and Programming         Model          4.2.2       DataCutter for Distributed Multicore Programming         CBE Intercore Messaging Library          DataCutter-Lite for CBE Optimizations                                                                                                                                                                     | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> </ul>                                                 |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3               | omponent-Based Framework for the Cell Broadband Engine          Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>84</li> </ul>                                     |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3               | omponent-Based Framework for the Cell Broadband Engine          Introduction          Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters          4.2.1       DataCutter-Lite Architecture and Programming         Model          4.2.2       DataCutter for Distributed Multicore Programming         CBE Intercore Messaging Library          DataCutter-Lite for CBE Optimizations          4.4.1       High-Bandwidth SPE-SPE Two-Sided Communication         4.4.2       Pure Pull-based PPE-SPE Communication                                       | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>84</li> <li>87</li> </ul>                         |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3               | omponent-Based Framework for the Cell Broadband Engine          Introduction          Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters          4.2.1       DataCutter-Lite Architecture and Programming         Model          4.2.2       DataCutter for Distributed Multicore Programming         CBE Intercore Messaging Library          DataCutter-Lite for CBE Optimizations          4.4.1       High-Bandwidth SPE-SPE Two-Sided Communication                                                                                                 | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>84</li> <li>87</li> <li>89</li> </ul>             |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3<br>4.4        | omponent-Based Framework for the Cell Broadband Engine          Introduction          Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters          4.2.1       DataCutter-Lite Architecture and Programming         Model          4.2.2       DataCutter for Distributed Multicore Programming         CBE Intercore Messaging Library          DataCutter-Lite for CBE Optimizations          4.4.1       High-Bandwidth SPE-SPE Two-Sided Communication         4.4.3       Buffer Prefetching         4.4.4       Fine-grained Buffer Arrival Blocking | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>87</li> <li>89</li> <li>90</li> </ul>             |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5 | omponent-Based Framework for the Cell Broadband Engine          Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>87</li> <li>89</li> <li>90</li> <li>91</li> </ul> |

| -          | ing<br>A Co<br>4.1<br>4.2<br>4.3<br>4.4        | omponent-Based Framework for the Cell Broadband Engine          Introduction          Filter-Stream Programming for Heterogeneous,         Hierarchical Clusters          4.2.1       DataCutter-Lite Architecture and Programming         Model          4.2.2       DataCutter for Distributed Multicore Programming         CBE Intercore Messaging Library          DataCutter-Lite for CBE Optimizations          4.4.1       High-Bandwidth SPE-SPE Two-Sided Communication         4.4.3       Buffer Prefetching         4.4.4       Fine-grained Buffer Arrival Blocking | <ul> <li>68</li> <li>69</li> <li>69</li> <li>73</li> <li>74</li> <li>79</li> <li>81</li> <li>84</li> <li>87</li> <li>89</li> <li>90</li> </ul>             |

|    | 5.1   | Introduction                                                       | 99           |

|----|-------|--------------------------------------------------------------------|--------------|

|    | 5.2   | Related Work                                                       | 101          |

|    | 5.3   | Application and System Model                                       | 103          |

|    | 5.4   |                                                                    | 104          |

|    | 5.5   |                                                                    | 109          |

|    |       |                                                                    | 109          |

|    |       |                                                                    | 113          |

|    |       |                                                                    | 120          |

|    | 5.6   |                                                                    | 122          |

| 6. | Impi  | roving Performance of Adaptive Component-Based Dataflow Middleware | 123          |

|    | 6.1   | Introduction                                                       | 123          |

|    | 6.2   |                                                                    | $123 \\ 127$ |

|    | 6.2   |                                                                    | $121 \\ 129$ |

|    | 0.5   |                                                                    | $129 \\ 129$ |

|    |       | I                                                                  | $129 \\ 130$ |

|    |       | ·                                                                  |              |

|    | 6.4   | 1                                                                  | 132<br>135   |

|    | 6.4   |                                                                    |              |

|    | C F   |                                                                    | 136<br>147   |

|    | 6.5   | <b>FF</b>                                                          |              |

|    | 6.6   | 1                                                                  | 150          |

|    |       |                                                                    | 150          |

|    |       |                                                                    | 151          |

|    |       |                                                                    | 153          |

|    |       |                                                                    | 154          |

|    | 6.7   |                                                                    | 155          |

|    |       | 1 0                                                                | 155          |

|    |       | 1                                                                  | 159          |

|    |       | V 1                                                                | 160          |

|    |       | 0 2                                                                | 164          |

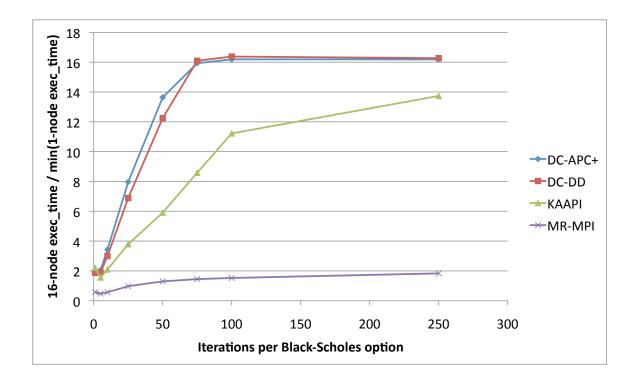

|    |       | 6.7.5 Black-Scholes                                                | 166          |

|    |       | 6.7.6 Tunable CCR                                                  | 170          |

|    |       | 6.7.7 Discussion of Experimental Results                           | 172          |

|    | 6.8   | Summary                                                            | 174          |

| 7. | Effic | iently Supporting Programming Models with Adaptive Dataflow        | 176          |

|    | 7.1   | Introduction                                                       | 176          |

|    | 7.2   |                                                                    | 176          |

|    |       |                                                                    | 177          |

|    |       |                                                                    | 178          |

|    | 7.3   | · ·                                                                | 180          |

|    | 1.0   |                                                                    | 100          |

|       |        | 7.3.1 Application Programming Interface                | 182 |

|-------|--------|--------------------------------------------------------|-----|

|       |        | 7.3.2 Interface Improvements and Runtime Optimizations | 184 |

|       | 7.4    | Preliminary Experimental Results                       | 190 |

|       | 7.5    | Summary                                                | 193 |

| 8.    | Conc   | clusions and Future Work                               | 194 |

| Bibli | iograp | phy                                                    | 197 |

# List of Tables

| Tab | le                                                                                                    | Page |

|-----|-------------------------------------------------------------------------------------------------------|------|

| 1.1 | Parallel and Distributed Programming Frameworks                                                       | 11   |

| 2.1 | Hardware features of the CPU and GPU                                                                  | 27   |

| 2.2 | Major hardware and software limitations with CUDA $\ . \ . \ . \ .$ .                                 | 32   |

| 2.3 | Major CUDA optimizations in the image analysis application                                            | 35   |

| 2.4 | Properties of the three slides used in our experiments                                                | 42   |

| 2.5 | Execution times for the image analysis application                                                    | 42   |

| 4.1 | High Performance Computing (HPC) techniques and DataCutter-Lite's approach                            | 70   |

| 4.2 | CBE Intercore Messaging Library Application Programming Interface                                     | 83   |

| 5.1 | Single tile execution times in milliseconds for four applications                                     | 111  |

| 5.2 | Aggregate number of tiles computed by each processor type while vary-<br>ing the system configuration | 119  |

| 5.3 | Aggregate work area computed by each processor type while varying the system configuration            | 120  |

| 6.1 | Execution times (in milliseconds) for SAR, BIA, and Black-Scholes for various tile sizes              | 156  |

# List of Figures

## Figure

## Page

| 1.1  | Example Filter-stream Application Layout and Placement                                                                   | 5  |

|------|--------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | Taxonomy of Parallel and Distributed Programming Frameworks                                                              | 9  |

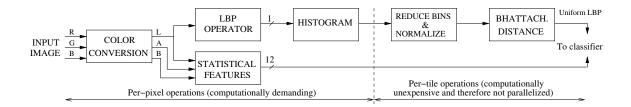

| 2.1  | Flow chart for the stroma classification algorithm                                                                       | 20 |

| 2.2  | The computation of a co-occurrence matrix (right) from a 4x4 image (left) where pixel intensities are shown              | 24 |

| 2.3  | The LBP operator on a 3x3 grid                                                                                           | 25 |

| 2.4  | The BALE supercomputer at a glance                                                                                       | 28 |

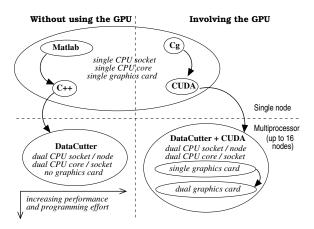

| 2.5  | The programming approaches and their effect on performance, both single node and parallel.                               | 30 |

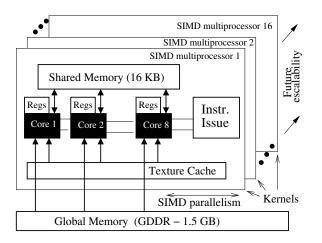

| 2.6  | The CUDA hardware interface.                                                                                             | 31 |

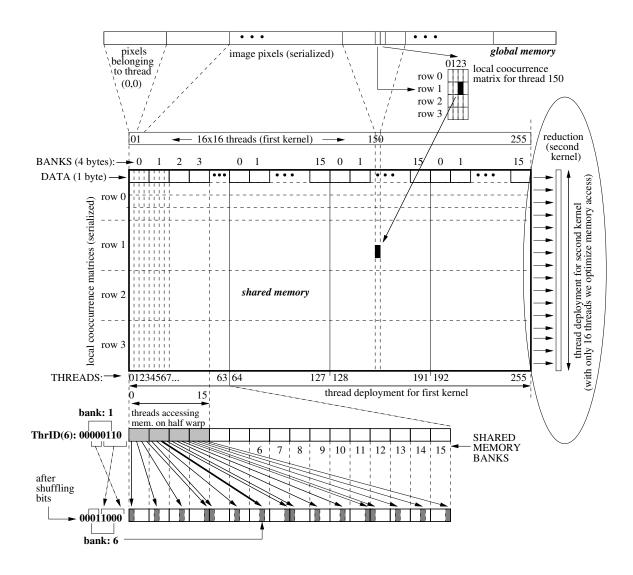

| 2.7  | Phase 2: Local co-occurrence matrices in CUDA                                                                            | 34 |

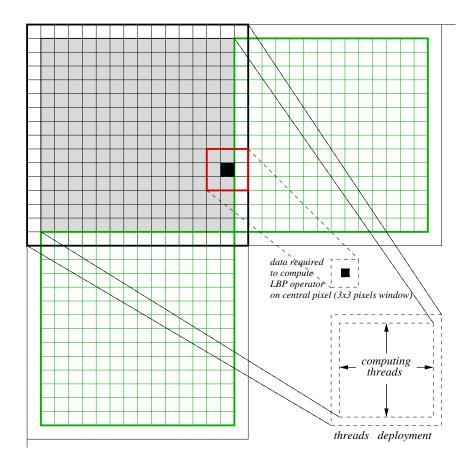

| 2.8  | Phase 3: LBP operator in CUDA                                                                                            | 36 |

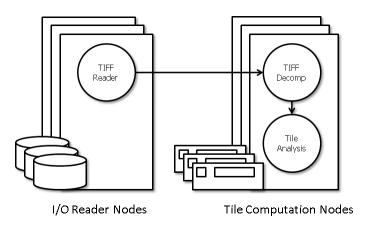

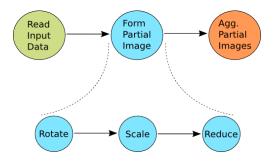

| 2.9  | DataCutter layout of the image analysis application.                                                                     | 40 |

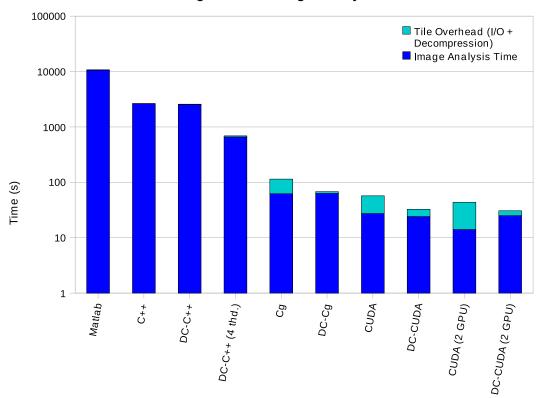

| 2.10 | Execution time comparison of all implementations of the image analysis codes running on a single node using SMALL image. | 44 |

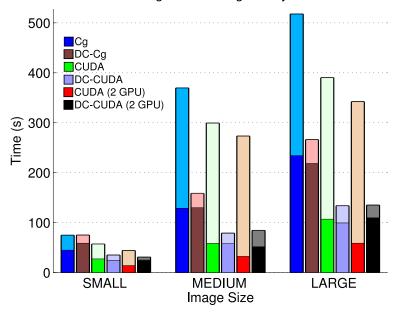

| 2.11 | Execution time comparison of GPU and DataCutter implementations running on a single node using all three input images    | 45 |

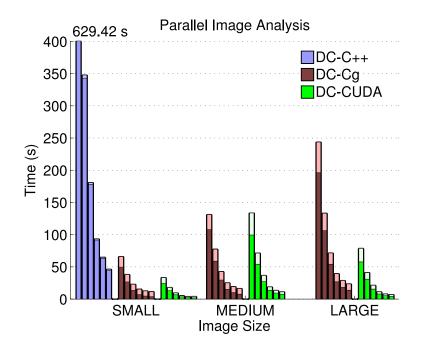

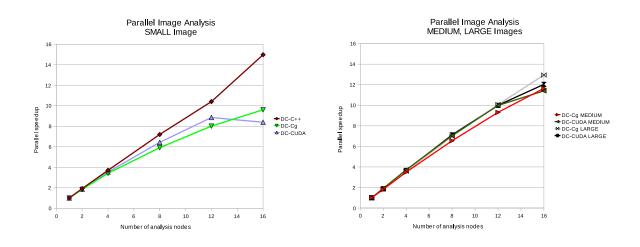

| 2.12 | Parallel execution times of C++, Cg, and CUDA based DataCutter implementations                                                | 46 |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

| 2.13 | Parallel speedup results                                                                                                      | 47 |

| 3.1  | Schematic demonstrating operation of the tomographic principle                                                                | 52 |

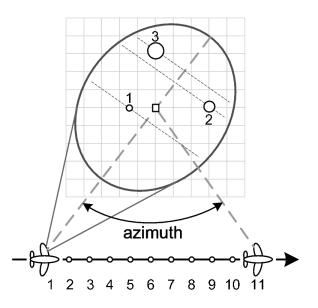

| 3.2  | Airborne sensor-gathered line projections                                                                                     | 53 |

| 3.3  | SAR Imaging Pipeline                                                                                                          | 57 |

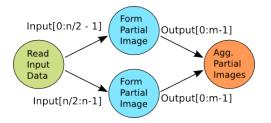

| 3.4  | SAR Imaging Input Partitioning                                                                                                | 59 |

| 3.5  | SAR Imaging Output Partitioning                                                                                               | 59 |

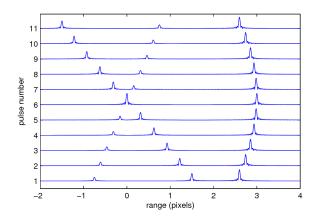

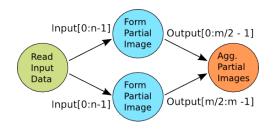

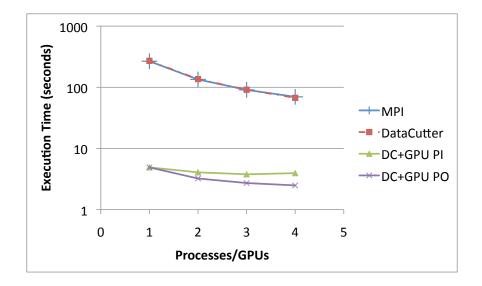

| 3.6  | Execution times of C/MPI and DataCutter backprojection implementations with $1^{\circ}$ of input data and varying image sizes | 62 |

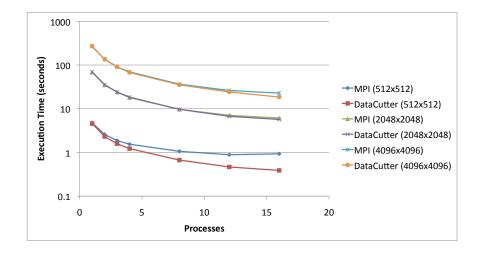

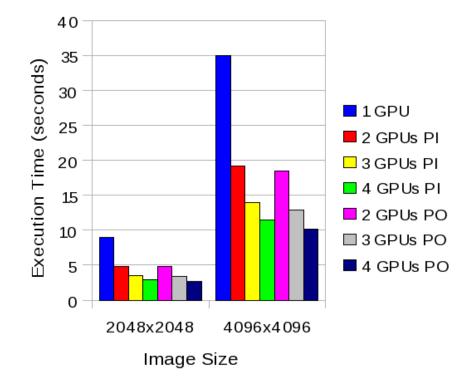

| 3.7  | Execution times of single GPU implementations with $1^\circ$ of input data.                                                   | 64 |

| 3.8  | Execution times of CPU and GPU implementations                                                                                | 65 |

| 3.9  | Execution times of DataCutter/GPU implementation                                                                              | 66 |

| 3.10 | Execution times of DataCutter/GPU implementation running on 4 GPUs while varying the input data set size.                     | 67 |

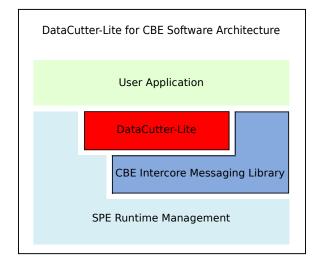

| 4.1  | DataCutter-Lite Library Application Interface                                                                                 | 75 |

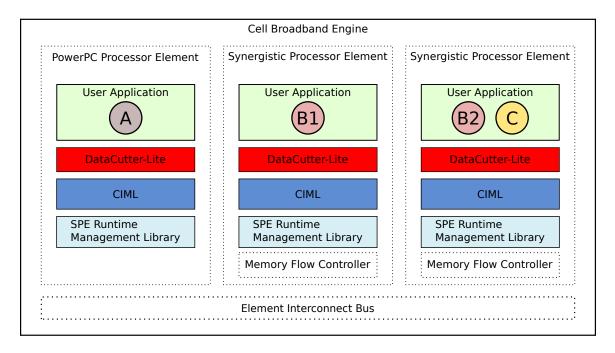

| 4.2  | Overall DataCutter-Lite System on the CBE                                                                                     | 75 |

| 4.3  | Sample DataCutter-Lite application and example mapping onto the Cell.                                                         | 76 |

| 4.4  | DataCutter-Lite Example PPE Code                                                                                              | 78 |

| 4.5  | DataCutter-Lite Example PPE Code                                                                                              | 79 |

| 4.6  | DataCutter-Lite Example SPE Code                                                                                              | 80 |

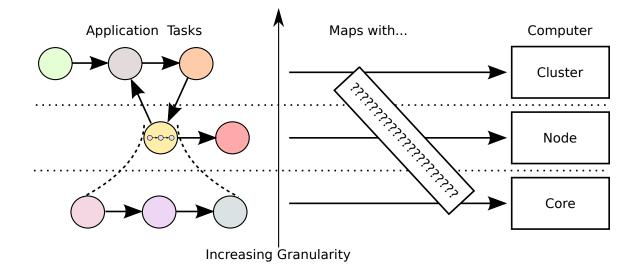

| 4.7  | Software and Hardware Granularities                                                                                           | 81 |

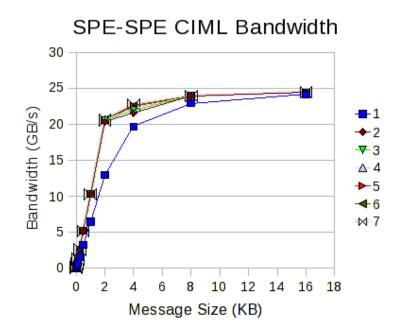

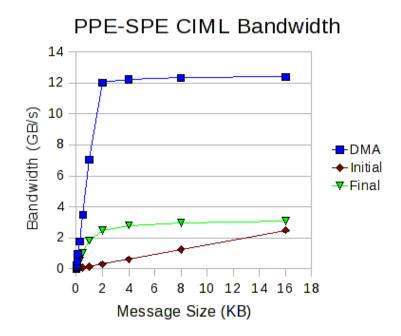

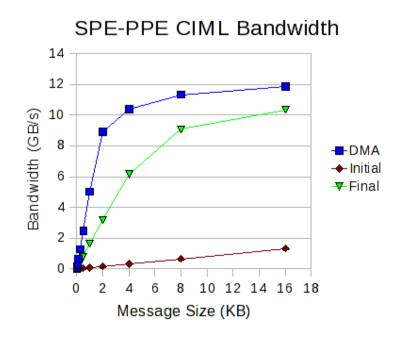

| 4.8  | SPE-SPE Communication Bandwidth Results                                                                                       | 84 |

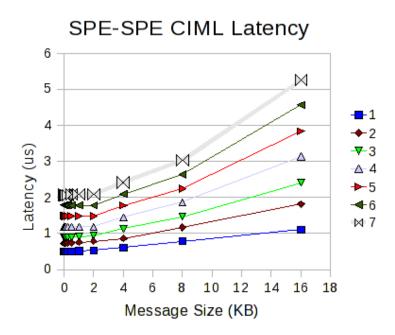

| 4.9  | SPE-SPE Communication Latency Results                                                                               | 85  |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

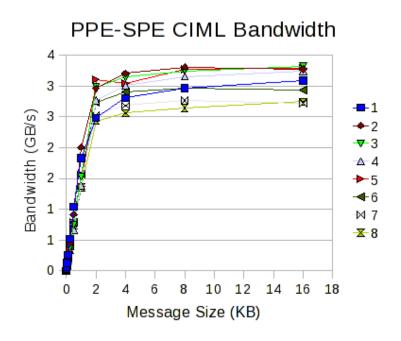

| 4.10 | PPE-SPE Communication Bandwidth Results                                                                             | 86  |

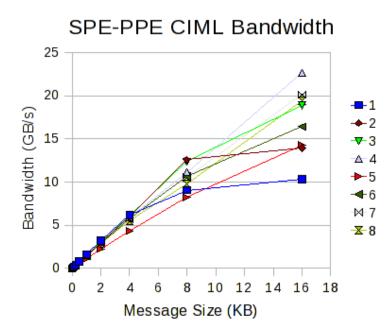

| 4.11 | SPE-PPE Communication Performance Results                                                                           | 86  |

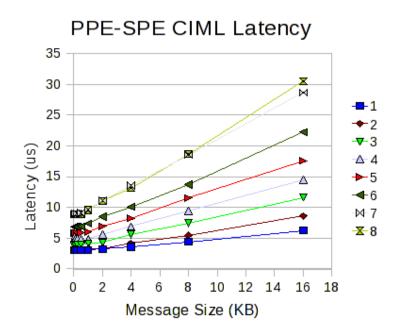

| 4.12 | SPE-PPE Communication Latency Results                                                                               | 87  |

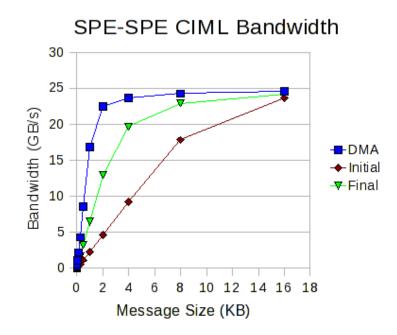

| 4.13 | SPE-SPE Communication Bandwidth Results                                                                             | 88  |

| 4.14 | PPE-SPE Communication Bandwidth Results                                                                             | 89  |

| 4.15 | SPE-PPE Communication Bandwidth Results                                                                             | 90  |

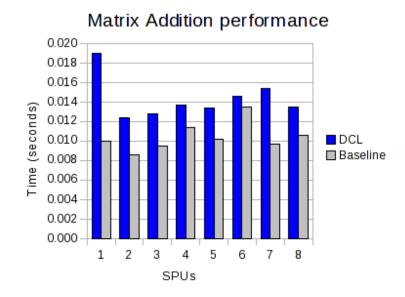

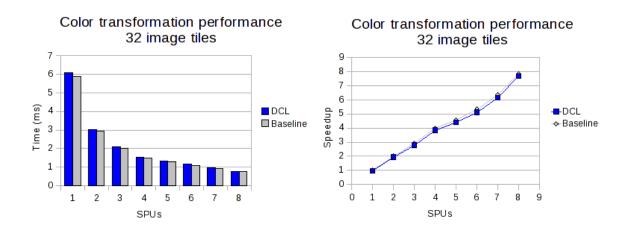

| 4.16 | Execution times for Matrix Addition                                                                                 | 94  |

| 4.17 | Execution times and speedups for color transformation for 32 image tiles                                            | 94  |

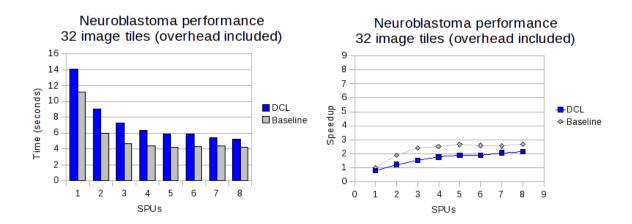

| 4.18 | Execution times and speedups for biomedical image analysis applica-<br>tion for 32 image tiles - overheads included | 95  |

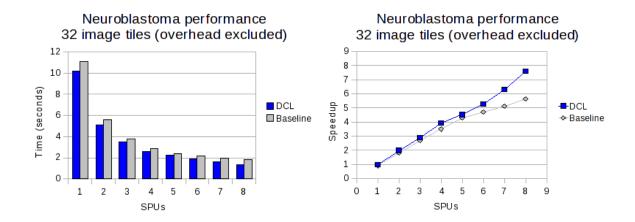

| 4.19 | Execution times and speedups for biomedical image analysis applica-<br>tion for 32 image tiles - overheads excluded | 96  |

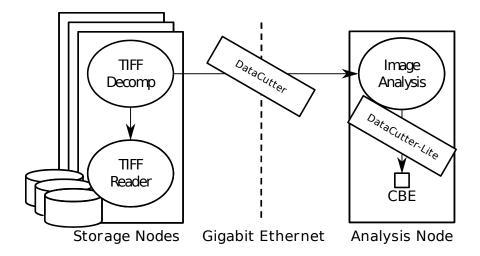

| 4.20 | DataCutter and DataCutter-Lite mixed implementation                                                                 | 97  |

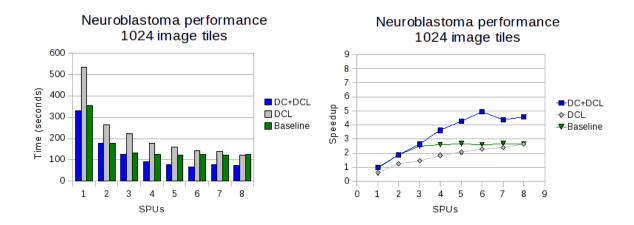

| 4.21 | Execution times and speedups for biomedical image analysis applica-<br>tion for 1024 image tiles                    | 98  |

| 5.1  | Adaptive Partitioning Controller Pseudocode                                                                         | 107 |

| 5.2  | Adaptive Dataflow Work Partitioner Pseudocode                                                                       | 108 |

| 5.3  | Microbenchmark #1 with 5:1 GPU:CPU core speedup; 4 Nodes; 10<br>1K x 1K Images                                      | 114 |

| 5.4  | Microbenchmark #2 with 10:1 GPU:CPU core speedup; 4 Nodes; 10<br>1K x 1K Images                                     | 115 |

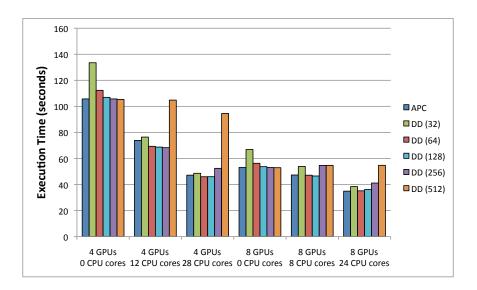

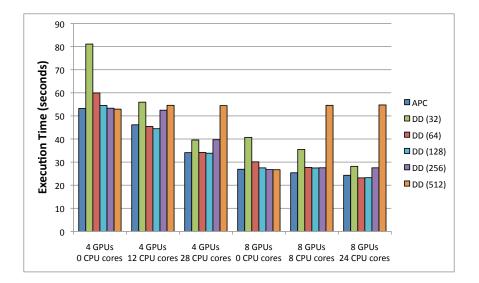

| 5.5  | BIA: Biomedical Image Analysis; 4 Nodes; 20 25K x 25K Images Analyzed                                               | 117 |

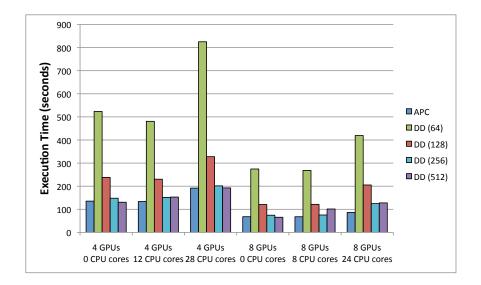

| 5.6  | SAR: Synthetic Aperture Radar Image Formation; 4 Nodes; 100 2K x 2K Images Formed                                    | 118 |

|------|----------------------------------------------------------------------------------------------------------------------|-----|

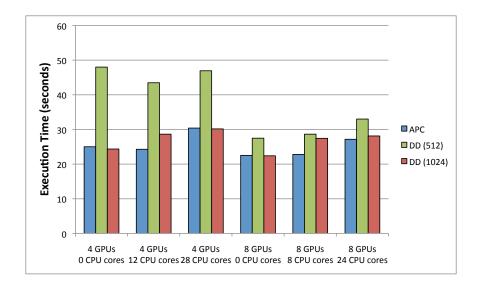

| 5.7  | Performance profile of APC and DD with a fixed tile size for all the system configurations for the four applications | 121 |

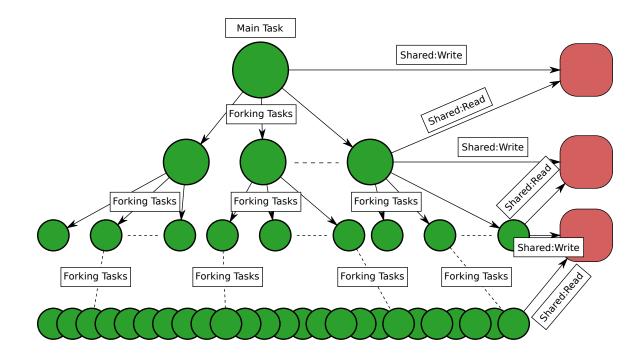

| 6.1  | Example Asynchronous Task Forking and Shared Data Access $\ . \ . \ .$                                               | 131 |

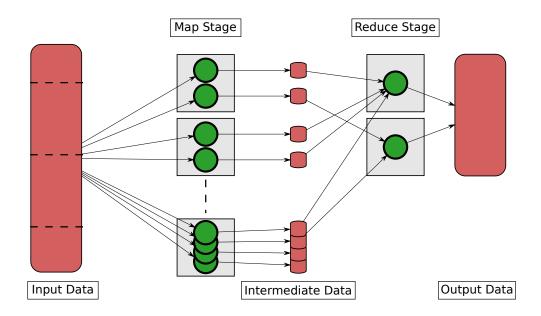

| 6.2  | Example MapReduce Execution                                                                                          | 133 |

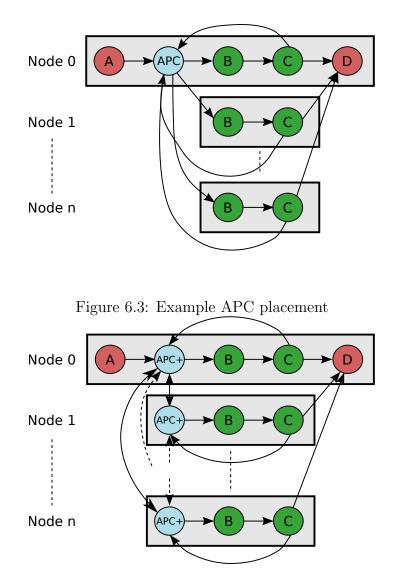

| 6.3  | Example APC placement                                                                                                | 140 |

| 6.4  | Example APC+ placement                                                                                               | 140 |

| 6.5  | Adaptive Partitioning Controller (APC+) Setup Pseudocode                                                             | 141 |

| 6.6  | Adaptive Partitioning Controller (APC+) Main Loop Pseudocode                                                         | 142 |

| 6.7  | Adaptive Dataflow Work Partitioner                                                                                   | 145 |

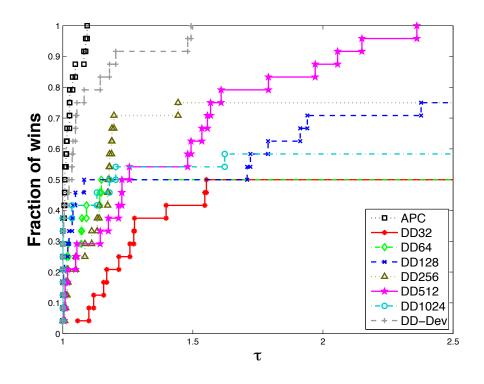

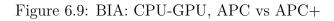

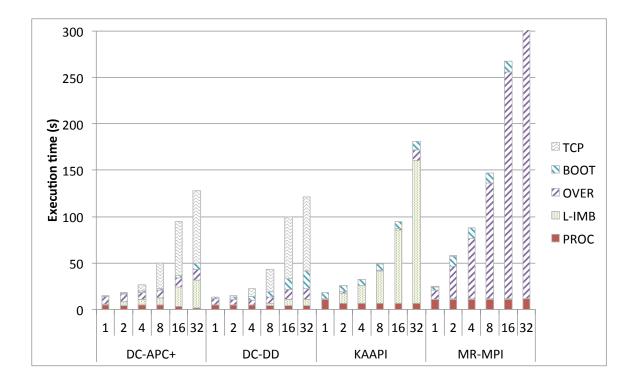

| 6.8  | SAR: CPU-GPU, APC vs APC+                                                                                            | 157 |

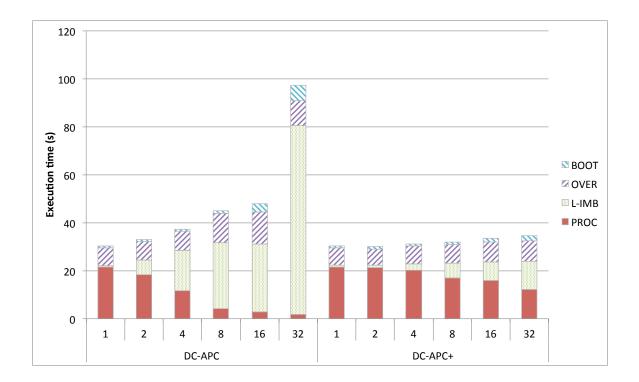

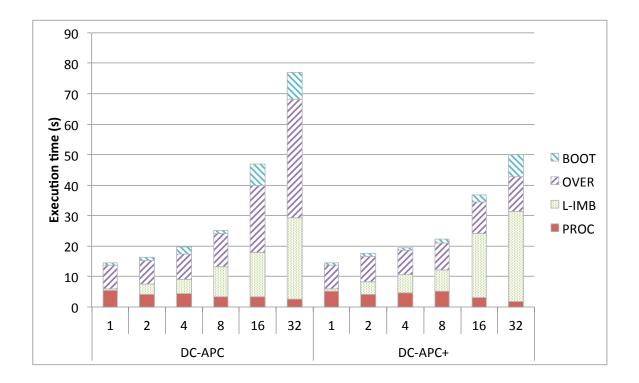

| 6.9  | BIA: CPU-GPU, APC vs APC+                                                                                            | 158 |

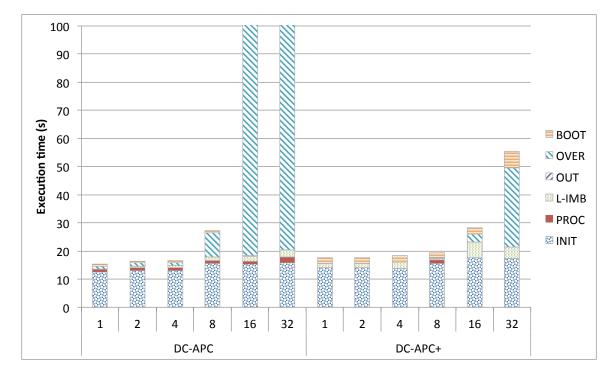

| 6.10 | Black-Scholes: CPU-GPU, APC vs APC+                                                                                  | 158 |

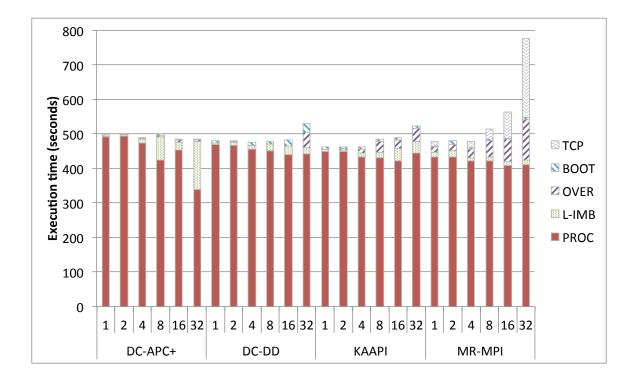

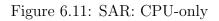

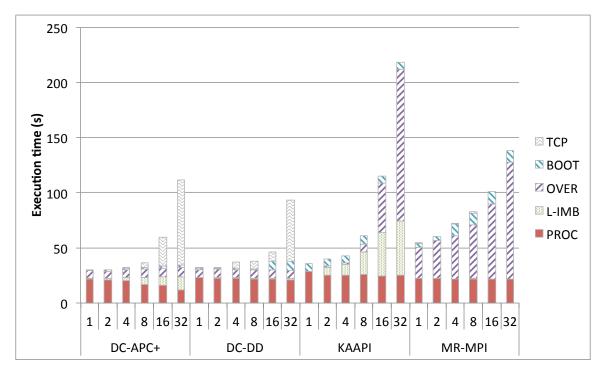

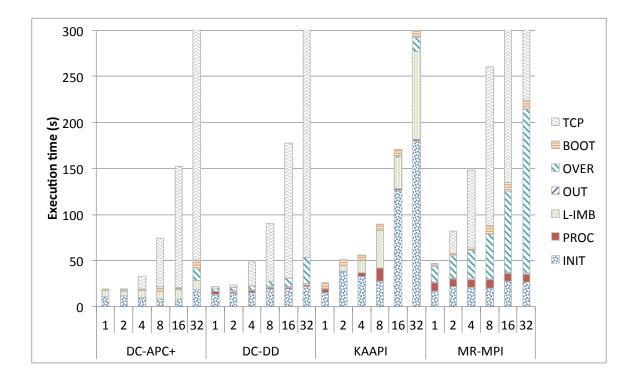

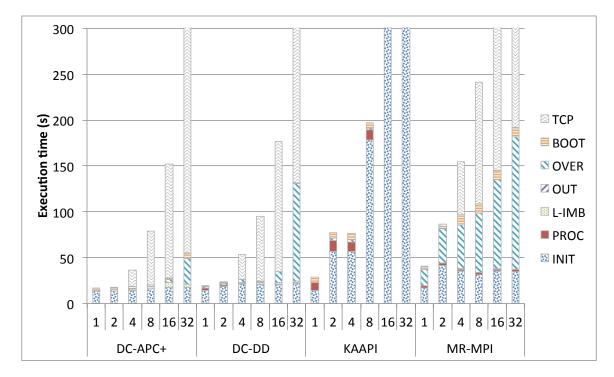

| 6.11 | SAR: CPU-only                                                                                                        | 161 |

| 6.12 | SAR: CPU-GPU                                                                                                         | 161 |

| 6.13 | Biomedical Image Analysis: CPU-only                                                                                  | 166 |

| 6.14 | Biomedical Image Analysis: CPU-GPU                                                                                   | 167 |

| 6.15 | Black-Scholes: CPU-only                                                                                              | 168 |

| 6.16 | Black-Scholes: CPU-GPU                                                                                               | 168 |

| 6.17 | Tunable CCR Application: 16 nodes, CPU-only                                                                          | 171 |

| 7.1  | Simple OpenMP Parallel-For Example                                                                                   | 177 |

| 7.2  | Homogeneous Adaptive Component-Based Parallel-For                                                                    | 179 |

|      |                                                                                                                      |     |

| 7.3  | Heterogeneous Adaptive Component-Based Parallel-For                  | 181 |

|------|----------------------------------------------------------------------|-----|

| 7.4  | Black-Scholes MR-MPI main function                                   | 183 |

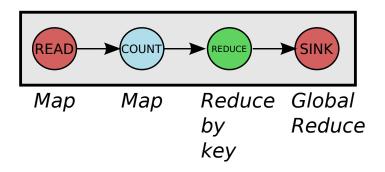

| 7.5  | MapReduce Wordcount Application Layout                               | 184 |

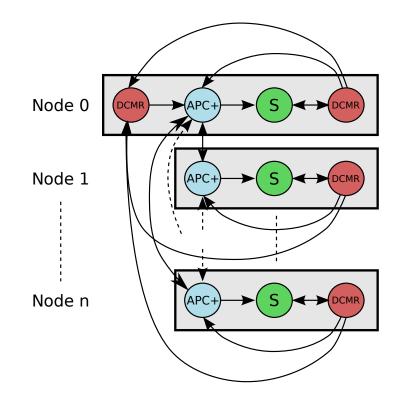

| 7.6  | DataCutter MapReduce                                                 | 185 |

| 7.7  | DataCutter MapReduce Application Programming Interface: Setup .      | 186 |

| 7.8  | DataCutter MapReduce Application Programming Interface: Source .     | 187 |

| 7.9  | DataCutter MapReduce Application Programming Interface: Count Words  | 188 |

| 7.10 | DataCutter MapReduce Application Programming Interface: Reduce Count | 189 |

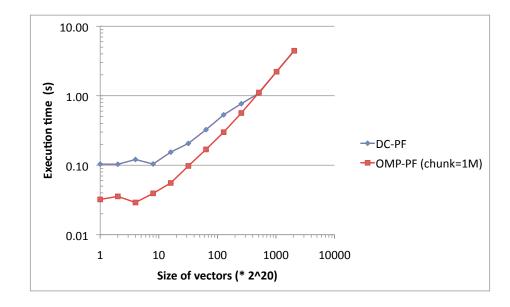

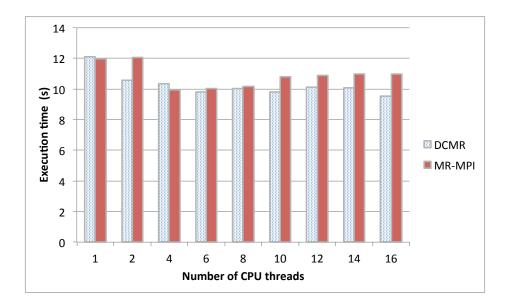

| 7.11 | DataCutter Parallel-For Vector Addition Single Node Performance      | 191 |

| 7.12 | DataCutter MapReduce WordCount Single Node Performance               | 192 |

### Chapter 1: Introduction

### 1.1 Motivation

In recent years, a growing falloff of the performance of microprocessors compared to Moore's Law (which states that the number of transistors on a chip will double roughly every eighteen months) has created a new opportunity for specialized, highperformance accelerator architectures such as the Cell Broadband Engine (CBE) [50]. The same trend of microprocessor performance rolloff, predominantly caused by increasing power consumption, has forced microprocessor manufacturers to increasingly rely on on-die, CPU-level parallelism for increased performance [79]. Further, during the same time period, Graphics Processing Unit (GPU) manufacturers have increased programmability and computational throughput such that GPUs are an attractive substitute for standard CPU architectures in certain extremely parallel and computationally demanding applications [81].

These new architectures have very high computational capability, but applications often need to be restructured to take advantage of the high performance on tap when using emerging architectures. Traditional techniques - pipelining of instruction execution, superscalar instruction execution, out-of-order instruction execution, as well as the introduction of SIMD operations to commodity microprocessors - have provided sequential programs enough performance [113] to make the added benefit of parallel computation not worth the additional complexity in application development. However, with the increasing parallelism inherent in new architectures, the available performance for certain applications [81, 51, 53, 112, 118, 93, 92] makes the increased development cost acceptable, since making full use of these high-performance architectures leads to cost-savings in other areas, such as lead time to market, reduced latency in decision-making, or power savings due to reduced computation time. Additionally, certain applications absolutely require extremely fast computation times to even be feasible such as certain types of medical image analysis [20, 96] and radar signal processing [56]. If sequential versions of certain computerized image analysis applications were the only ones available, no clinical practice, research laboratory, or military concern could use them, due to their excessively large execution times.

The modern supercomputers which can support these types of applications are built by using fast networks to connect large clusters of commodity microprocessors and emerging architecture-based nodes [8]. These systems are becoming more difficult to program because of the increasing levels of hierarchy and heterogeneity present in modern supercomputer designs due to the result of system upgrades, or more recently, the result of explicit initial design decisions. Current practical software solutions have not kept pace with these programming challenges, placing most of the burden on the developer [4]. To address this issue, this dissertation shows that componentbased dataflow middleware allows developers of high-performance scientific applications to leverage all of the peak computational capability inherent in heterogeneous, distributed supercomputers, without requiring heavy use of low-level programming tools requiring expert knowledge. Further, efficient solutions to tune and schedule component-based applications for these systems are few and far between, even in state-of-the-art middleware runtime systems. Therefore, this dissertation presents an adaptive framework and runtime system for developing and executing componentbased dataflow applications on heterogeneous, distributed supercomputers. We show our framework is able to generalize our ad-hoc optimization approaches and achieve comparable performance to manually tuned implementations in a number of largescale, real-world applications.

The rest of this introduction consists of an overview of the state-of-the-art of component-based programming frameworks, followed by a presentation of autotuning research, and of the programming models and runtime systems commonly used to develop applications for supercomputers. Following these sections, we present our contributions.

### 1.2 State of the Art

#### **1.2.1** Component-Based Framework Overview

The central thesis of component-based programming is that there are many advantages to describing and implementing complex applications by way of components - distinct tasks with well-defined interfaces. By describing these components and the explicit data connections between them, many advantages are conferred. Applications are decomposed along natural task boundaries, according to the application domain. Therefore, component-based application design is an intuitive process, with explicit demarcation of task responsibilities. Further, the communication patterns are also explicit, as each component includes in its description its input data requirements and outputs. Since many applications are comprised of a series of serial processing or analysis steps, explicitly defining a task graph to represent these processing steps is a natural method for breaking up and writing the program.

Beyond the implementation benefits, component-based programming also enables some runtime benefits, which come at no additional cost to the developer. Applications composed of a number of individual tasks can be executed on parallel and distributed computing resources and gain extra performance over those run on strictly sequential machines. Additionally, provided the interfaces exposed by a task to the rest of the application match, different implementations of tasks, possibly on different processor architectures can co-exist in the same application deployment, allowing developers to take full advantage of modern, heterogeneous supercomputers.

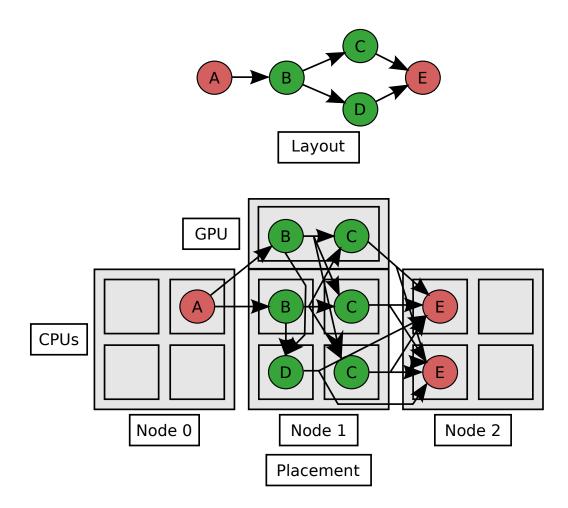

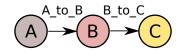

Filter-stream programming is an instance of component-based programming supported by DataCutter, a component-based middleware tool. The filter-stream programming model [13] (a specific implementation of the dataflow programming model [33]) implements computations as a set of components, referred to as *filters*, that exchange data through *logical streams*. A *stream* denotes a uni-directional data flow from some filters (i.e., the producers) to others (i.e., the consumers). Data flows along these *streams* in untyped *databuffers* so as to minimize various system overheads. A *layout* is a filter ontology which describes the set of application tasks, streams, and the connections required for the computation. A *placement* is one instance of a *layout* with actual filter copy to physical processor mappings. A *filter* can be *replicable*, if it is stateless; for instance, if a filter's output for a given *databuffer* does not depend on the ones it processed previously, it is stateless and replicable. Traditionally, the filterstream programming model is used through a middleware runtime system, which sits on top of the operating system(s) of the involved computational nodes and provides the dataflow interface abstraction to the application. Figure 1.1 shows an example filter-stream layout and placement.

Figure 1.1: Example Filter-stream Application Layout and Placement

In the filter-stream programming model, filters perform all of the computation in the application. Data flows through streams and into filters, and undergoes transformations inside the filters. Filter functions can transform data in a number of ways, ranging from one-to-one databuffer functions, to data join functions (where one or more databuffers are required from more than one stream), to data split functions (where more than one databuffer is created based on a single input databuffer). In the filter-stream model, application developers are only responsible for writing the filter functions and determining the filter and stream layout. The filter-stream model is ideal for programming for heterogeneous processor types, because the architecturespecific details are hidden inside the filter function; provided the same data structure interface is used by two implementations of the same filter function targeted at two different architectures, they can be used interchangeably.

### 1.2.2 Autotuning

Autotuning (automatic performance testing and optimization) is a field where a feedback loop is introduced in the software development process or when the application is executed. This feedback loop is used to allow some adaptive process to occur, such that execution times from test runs of a sequential or a parallel application can be used to choose application parameters such as data partitioning, number of concurrent processing threads, size of computational kernel, size of cache footprint, extent of loop unrolling, amount of data prefetching. It is an active field, especially in the realm of multicore computing, as traditionally compiled application performance has begun to lag behind the architectures' capabilities [4, 66].

Atune-IL [94] is a language-independent framework for instrumenting parallel applications for an automatic tuning process. The types of tuning include number of threads, data chunk size, and algorithm choice. Developers introduce pragmas into their code, and then build their executable with a special compiler. Then, by using a search algorithm, the framework automatically adapts the instrumented parameters for best performance. Tiwari et al. present a method for efficiently searching for the highest-performing compiler transformation for an arbitrary set of nested loop iterations [109]. By combining an updated Parallel Rank Ordering algorithm [102] algorithm and a library for generating complex, but correct loop transformations, CHiLL [25], the authors rival the performance of other auto-tuned numerical libraries.

FIBER [68, 67] is a framework for automatically tuning - at install time, before execution, and at runtime - numerical software, by testing which algorithms and loop unrolling parameters achieve the highest performance.

Several researchers at UC Berkeley have conducted extensive analyses of optimizations required to generate high-performance stencil kernels on several state-ofthe-art multicore architectures such as standard multi-core CPUs, highly-threaded multi-core CPUs, the Cell Broadband Engine, and GPUs [29, 65]. By first developing architecture-agnostic, application-specific optimization techniques, as well as a framework for automatic optimization, the authors are able to quickly search a large space of optimizations, to find and present the important tradeoffs involved with the area of regular numeric kernals.

POET [115] is a language for describing and applying complex loop optimizations to numerical kernels. It is intended to be used as a communication method between successive optimization steps, and as a generator for different combinations of parameters for optimized kernels.

SPRIAL, Signal Processing Implementation Research for Adaptable Libraries is a framework for autotuning DSP software [90]. ATLAS [111] uses compile-time performance tests to tune its implementations of linear algebra operations. FFTW [42] tunes data structures and algorithms at runtime to efficiently perform FFT operations.

Networking techniques for congestion control and QOS, such as TCP Vegas [18] have been well-known for some time as adaptive methods to improve performance in a distributed setting.

#### **1.2.3** Parallel and Distributed Programming Frameworks

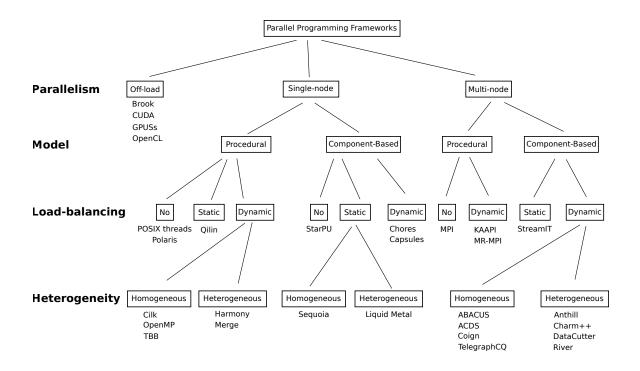

Since our work targets hierarchical, heterogeneous, distributed supercomputers, we will discuss programming models, middleware, and libraries to ease programming for parallel systems, as well as systems with heterogeneous processors or networks. The axes along which we will compare the frameworks are their overall programming model, their supported level of parallelism, their explicit support for heterogeneity, and their load balance capabilities. Figure 1.2 and Table 1.1 show the overall picture.

Our list of frameworks falls into three categories of parallelism, off-load, singlenode, and multi-node. The off-load frameworks focus on developing high-performance kernels for graphics processors. While the development of kernels for accelerator devices is outside the scope of this dissertation, GPUs are in and of themselves parallel architectures, and their effective use requires many of the same steps as does more traditional parallel programming: data and task decomposition, parallel algorithm design, etc. Brook [19] was the first framework for developing general purpose computation on GPUs, predating CUDA by several years. However, with the release of the Nvidia CUDA SDK [26], the level of computational power in GPUs had increased steadily, meaning that the commodity status and the increased programmability of

Figure 1.2: Taxonomy of Parallel and Distributed Programming Frameworks

GPUs made for very fertile research ground. Later, higher-level frameworks such as GPUSs [6] were developed for writing applications to leverage multiple GPUs more easily. Finally, the industry has standardized an approach to writing applications for GPUs from all vendors, OpenCL [80].

Though our research focuses on parallel computing in the physically and logically distributed-memory paradigm, the array of frameworks which target single nodes can still be inspirational. These frameworks can be classified along many different axes, but among the most important characteristics is the framework's similarity to sequential programming. Here we call sequential-like programming frameworks *procedural*, while the opposing style is called *component-based*. Component-based frameworks encourage (or require) developers to create multiple, concurrent components

and an explicit plan for how these components will interact. Well-known procedural frameworks such as POSIX threads [61] and OpenMP [27] are mature technologies, which are mainstays of high-performance scientific computing. Cilk [16] uses a similar procedural-style programming paradigm, although it adds a work-stealing load-balancing framework, and some theoretical guarantees of asymptotically optimal performance, in certain circumstances. TBB [105] is somewhat of a shared-memory Swiss army knife, in that it provides a framework for exploiting loop iteration parallelism, task parallelism with work-stealing load-balancing, and pipeline parallelism. Finally, frameworks like Qilin [75], Harmony [34], and Merge [74] leverage explicit support for heterogeneous processor types to enable developers to write efficient applications.

High-level parallel and distributed programming frameworks for multi-node systems lower the bar to programming efficient applications for modern HPC systems. As can be seen from Figure 1.2, while single-node frameworks can be found in both the procedural and component-based categories in equal measure, multi-node frameworks are more often component-based than not. Be that as it may, the vast majority of high-performance scientific application software is undoubtedly written in MPI [77]. Before the message-passing standard was developed, there were many competing vendor-specific frameworks, each tied to the manufacturer's specific architecture. While programming efficient applications with an explicit message-passing interface is challenging, developing a parallelizing compiler capable of producing an

| Framework       | Programming Model Parallelism | Parallelism | CPU/GPU          | Load Balancing         |

|-----------------|-------------------------------|-------------|------------------|------------------------|

| ABACUS [1]      | Component-Based               | Multi-node  | Homogeneous CPU  | Dynamic                |

| ACDS $[62]$     | Component-Based               | Multi-node  | Homogeneous CPU  | Dynamic                |

| Anthill $[40]$  | Component-Based               | Multi-node  | CPU/GPU          | Dynamic                |

| Brook [19]      | Procedural                    | Off-load    | GPU              | No                     |

| CUDA [26]       | Procedural                    | Off-load    | GPU              | No                     |

| Capsules [76]   | Component-Based               | Single-node | Homogeneous CPU  | Dynamic                |

| Charm++ [64]    | Component-Based               | Mixed       | CPU/Accelerators | Dynamic                |

| Chores [36]     | Component-Based               | Single-node | Homogeneous CPU  | Dynamic                |

| Cilk [16]       | Procedural                    | Single-node | Homogeneous CPU  | Dynamic                |

| Coign [59]      | Component-Based               | Multi-node  | Homogeneous CPU  | Dynamic                |

| DataCutter [13] | Component-Based               | Multi-node  | CPU/GPU          | Dynamic                |

| GPUSs [6]       | Procedural                    | Off-load    | GPU              | No                     |

| Harmony [34]    | Procedural                    | Single-node | CPU/GPU          | Dynamic                |

| KAAPI [45]      | Procedural                    | Multi-node  | Homogeneous CPU  | Dynamic                |

|                 |                               |             | Cont             | Continued on next page |

Table 1.1: Parallel and Distributed Programming Frameworks

11

| Framework            | Model           | Parallelism | Heterogeneity     | Load Balancing |

|----------------------|-----------------|-------------|-------------------|----------------|

| Liquid Metal [58]    | Component-Based | Single-node | CPU/FPGA          | Static         |

| MIT's StreamIT [108] | Component-Based | Multi-node  | Homogeneous CPU   | Static         |

| MPI [77]             | Procedural      | Multi-node  | Homogeneous CPU   | No             |

| MR-MPI [88]          | Procedural      | Multi-node  | Homogeneous CPU   | Dynamic        |

| Merge [74]           | Procedural      | Single-node | CPU/GPU           | Dynamic        |

| OpenCL [80]          | Procedural      | Off-load    | GPU               | No             |

| OpenMP [27]          | Procedural      | Single-node | Homogeneous CPU   | Dynamic        |

| POSIX threads [61]   | Procedural      | Single-node | Homogeneous CPU   | No             |

| Polaris [15]         | Procedural      | Single-node | Homogeneous CPU   | No             |

| Qilin [75]           | Procedural      | Single-node | CPU/GPU           | Static         |

| River [3]            | Component-Based | Multi-node  | Heterogeneous CPU | Dynamic        |

| Sequoia [38]         | Component-Based | Single-node | Homogeneous CPU   | Static         |

| [StarPU [5]]         | Component-Based | Single-node | Homogeneous CPU   | No             |

| TBB [105]            | Mixed           | Single-node | Homogeneous CPU   | Dynamic        |

| TelegraphCQ [23]     | Component-Based | Multi-node  | Homogeneous CPU   | Dynamic        |

Table 1.1 – continued from previous page

efficient parallel version of an arbitrary sequential program is essentially impossible. Thus, the great variety of MPI-based parallel program. However, recently MapReduce [32], another procedural parallel programming framework for multi-node systems, has made a significant impact on developers of parallel programs. By using a simplified application task and data model, MapReduce allows users to write functions which operate on portions of an implicitly-referenced distributed hashtable. Further, MapReduce allows application-oblivious parallel communication. As such, developers of MapReduce programs do not need to write any parallel-specific code.

Component-based distributed programming frameworks attempt to ease the developer's task of managing the often conflicting concerns of processor utilization, network efficiency, and load balance. MIT's StreamIT project [108] provides a framework and compiler to easily produce high-performance streaming dataflow applications. While StreamIT performs heuristic dataflow graph operations which give a best-effort static load balance, many multi-node distributed programming frameworks offer online, dynamic load balancing. This final group of frameworks is still further divided by their explicit support for heterogeneity. The legacy frameworks ABACUS [1], ACDS [62], Coign [59], and TelegraphCQ [23] all focus on homogeneous clusters of SMP systems. KAAPI [45], a newer framework based on the Athapascan-1 language [43], also targets homogeneous clusters, although the authors are currently completely rewriting the codebase from the ground up to explicitly support accelerators. Anthill [40], Charm++ [64], and DataCutter [13] also support heterogeneous CPUs and GPUs with encapsulation and abstraction. Finally, River [3] supports heterogeneous data production and consumption rates, in that producer/consumer relationships are efficiently handled over the network by their flow rate. Thus, any node characteristic that would alter the flow rate is explicitly handled.

#### **1.3** Contributions