# OPTIMIZING LOCALITY AND PARALLELISM THROUGH PROGRAM REORGANIZATION

DISSERTATION

Presented in Partial Fulfillment of the Requirements for

the Degree Doctor of Philosophy in the

Graduate School of The Ohio State University

By

Sriram Krishnamoorthy, B.E., M.S.

\* \* \* \* \*

The Ohio State University

2008

**Dissertation Committee:**

P. Sadayappan, Adviser

Srinivasan Parthasarathy

Atanas Rountev

Approved by

Adviser Graduate Program in Computer Science and Engineering

#### ABSTRACT

Development of scalable application codes requires an understanding and exploitation of the locality and parallelism in the computation. This is typically achieved through optimizations by the programmer to match the application characteristics to the architectural features exposed by the parallel programming model. Partitioned address space programming models such as MPI foist a process-centric view of the parallel system, increasing the complexity of parallel programming. Typical global address space models provide a shared memory view that greatly simplifies programming. But the simplified models abstract away the locality information, precluding optimized implementations. In this work, we present techniques to reorganize program execution to optimize locality and parallelism, with little effort from the programmer.

For regular loop-based programs operating on dense multi-dimensional arrays, we propose an automatic parallelization technique that attempts to determine a parallel schedule in which all processes can start execution in parallel. When the concurrent tiled iteration space inhibits such execution, we present techniques to re-enable it. This is an alternative to incurring the pipelined startup overhead in schedules generated by prevalent approaches.

For less structured programs, we propose a programming model that exposes multiple levels abstraction to the programmer. These abstractions enable quick prototyping coupled with incremental optimizations. The data abstraction provides a global view of distributed data organized as blocks. A block is a subset of data stored contiguously in a single process' address space. The computation is specified as a collection of tasks operating on the data blocks, with parallelism and dependence being specified between them. When the blocking of the data does not match the required access pattern in the computation, the data needs to be reblocked to improve spatial locality. We develop efficient data layout transformation mechanisms for blocked multi-dimensional arrays. We also present mechanisms for automatic management of load balance, disk I/O, and inter-process communication on computations expressed as sets of independent tasks on blocked data stored on disk. To my parents, Sri. S. Krishnamoorthy and Smt. K. Seethalakshmi

### ACKNOWLEDGMENTS

This thesis would not have been possible without help from lots of friends and strangers. In addition to being my graduate school stint, these were five years of my life and I would like to thank those that made it memorable. But the list is too long and I will only mention a few.

Sandhya Krishnan and Chi-Chung Lam showed me the methodical approach that motivated me to do my PhD. Sandhya was among the first of a long line of hands that fed me in graduate school. Arjav Chakravarti gave me company on numerous lunches, dinners, and late-nighters. Gerald Sabin introduced me to Slashdot and PhD comics, which probably added a few months to my graduate school. Qingda Lu and Amol Ghoting provided their helpful insights on a lot of things.

There were those attempts at tennis and physical fitness that will keep Rajkiran Panuganti, Muthu Baskaran, Shirish Tatikonda, Uday Bondhugula, and Gaurav Khanna in my memories. Jim Dinan, Joshua Levine, and I made my first snow man. Together with Brian, they have always kept things funny and lively in the lab. My first Thanksgiving experience was with Beth Connell and her family.

My advisor Prof. P Sadayappan provided continuous support, motivation, and enthusiasm throughout my graduate studies. His never-say-die attitude to research has inspired me many a time. I cannot count the number of times I have been told how fortunate I am to have him as my advisor. Srini Parthasaraty and Atanas Rountev provided me timely and useful guidance on research and the publication process. I had insightful discussions with J Ramanujam on loop transformations.

My family made sure I survived through graduate school. I am fortunate to have them as part of my life. My parents inculcated in me a balanced outlook that was extremely helpful through these years. My father's insistence on education and love for books rubbed off on me. He motivated me to pursue graduate school rather than take up a job. My mother constantly reminded me that I need to eat, and is largely the reason I am alive today. I cannot recount all the instances in which my life was made easier by just following my brother's footsteps. He did all the hard work. My sister was the one that kept things light through the years.

If my parents were instrumental in me starting graduate school, Chandrika provided me strong enough encouragement to try to end it. I cannot thank her enough for packing my bags on countless occasions. Despite having known me for the better part of my life, she has agreed to hang around for some more time in the future.

### VITA

| 2002 | <br>B.E. Computer Science & Engineering, |

|------|------------------------------------------|

|      | Anna University, Chennai, TN, India      |

| 2006 | <br>M.S. Computer Science & Engineering, |

|      | Ohio State University, Columbus, OH      |

### PUBLICATIONS

X. Gao, S. Krishnamoorthy, S. K. Sahoo, C. Lam, G. Baumgartner, J. Ramanujam, and P. Sadayappan. "Efficient Search-Space Pruning for Integrated Fusion and Tiling Transformations". *Concurrency and Computation: Practice and Experience*, 19(18):2425–2443, December 2007.

S. Krishnamoorthy, G. Baumgartner, C. Lam, J. Nieplocha, and P. Sadayappan. "Layout Transformation Support for the Disk Resident Arrays Framework". *Journal of Supercomputing*, 36(2):153–170, May 2006.

A. Auer, G. Baumgartner, D. E. Bernholdt, A. Bibireata, V. Choppella, D. Cociorva, X. Gao, R. Harrison, S. Krishnamoorthy, S. Krishnan, C. Lam, M. Nooijen, R. Pitzer, J. Ramanujam, P. Sadayappan, and A. Sibiryakov. "Automatic Code Generation for Many-Body Electronic Structure Methods: The Tensor Contraction Engine". *Molecular Physics*, 104(2):211–228, January 2006.

S. Krishnan, S. Krishnamoorthy, G. Baumgartner, C. Lam, J. Ramanujam, P. Sadayappan, and V. Choppella. "Efficient Synthesis of Out-of-Core Algorithms Using a Nonlinear Optimization Solver". *Journal of Parallel and Distributed Computing*, 66(5):659–673, May 2006.

G. Baumgartner, A. Auer, D.E. Bernholdt, A. Bibireata, V. Choppella, D. Cociorva, X. Gao, R.J. Harrison, S. Hirata, S. Krishnamoorthy, S. Krishnan, C. Lam, Q. Lu, M. Nooijen,

R.M. Pitzer, J. Ramanujam, P. Sadayappan, and A. Sibiryakov. "Synthesis of High-Performance Parallel Programs for a Class of Ab Initio Quantum Chemistry Models". *Proceedings of the IEEE*, 93(2):276–292, February 2005.

S. Krishnamoorthy, G. Baumgartner, D. Cociorva, C. Lam, and P. Sadayappan. "Efficient Parallel Out-of-core Matrix Transposition". *International Journal of High Performance Computing and Networking*, 2(2/3/4):110–119 2004.

M. Baskaran, Uday Bondhugula, S. Krishnamoorthy, J. Ramanujam, A. Rountev, and P. Sadayappan. "Automatic Data Movement and Computation Mapping for Multi-level Parallel Architectures with Explicitly Managed Memories". In *Proceedings of ACM SIGPLAN Symposium on Principles and Practice of Parallel Programming (PPoPP'08)*, February 2008.

S. Krishnamoorthy, J. P. Canovas, V. Tipparaju, J. Nieplocha, and P. Sadayappan. "Non-Collective Parallel I/O for Global Address Space Programming Models". In *Proceedings of Cluster 2007*, September 2007.

S. Krishnamoorthy, M. Baskaran, U. Bondhugula, J. Ramanujam, A. Rountev, and P. Sadayappan. "Effective Automatic Parallelization of Stencil Computations". In *Proceedings* of ACM SIGPLAN Conference on Programming Language Design and Implementation (PLDI'07), June 2007.

S. Krishnamoorthy, U. Catalyurek, J. Nieplocha, and P. Sadayappan. "Hypergraph Partitioning for Automatic Memory Hierarchy Management". In *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis. November 2006 (SC 2006)*, November 2006.

M. Blocksome, C. Archer, T. Inglett, P. McCarthy, M. Mundy, J. Ratterman, A. Sidelnik, B. Smith, G. Almasi, J. Castanos, D. Lieber, J. Moreira, S. Krishnamoorthy, and V. Tipparaju. "Design and Implementation of a One-Sided Communication Interface for the IBM eServer Blue Gene Supercomputer". In *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis. November 2006 (SC 2006)*, November 2006.

N. Vydyanathan, S. Krishnamoorthy, G. Sabin, U. Catalyurek, T. Kurc, P. Sadayappan, and J. Saltz. "Locality Conscious Processor Allocation and Scheduling for Mixed-Parallel Applications". In *Proceedings of the IEEE International Conference on Cluster Computing*, September 2006.

Q. Lu, S. Krishnamoorthy, and P. Sadayappan. "Combining Analytical and Empirical Approaches in Tuning Matrix Transposition". In *Proceedings of the 15th International Conference on Parallel Architectures and Compiler Techniques. (PACT 2006)*, September 2006.

N. Vydyanathan, S. Krishnamoorthy, G. Sabin, U. Catalyurek, T. Kurc, P. Sadayappan, and J. Saltz. "An Integrated Approach for Processor Allocation and Scheduling of Mixed-Parallel Applications". In *Proceedings of the 35th International Conference on Parallel Processing (ICPP 2006)*, August 2006.

A. Hartono, Q. Lu, X. Gao, S. Krishnamoorthy, M. Nooijen, G. Baumgartner, V. Choppella, D. E. Bernholdt, R. M. Pitzer, J. Ramanujam, A. Rountev, and P. Sadayappan. "Identifying Cost-Effective Common Subexpressions to Reduce Operation Count in Tensor Contraction Evaluations". In *Proceedings of the 6th International Conference on Computational Science (ICCS 2006)*, May 2006.

G. Khanna, N. Vydyanathan, U. Catalyurek, T. Kurc, S. Krishnamoorthy, P. Sadayappan, and J. Saltz. "Task Scheduling and File Replication for Data-Intensive Jobs with Batch-Shared I/O" In *Proceedings of the 15th IEEE International Symposium on High Performance Distributed Computing (HPDC 2006)*, June 2006.

S. Krishnamoorthy, J. Nieplocha, and P. Sadayappan. "Data and Computation Abstractions for Dynamic and Irregular Computations". In *Proceedings of the 12th Annual International Conference on High Performance Computing (HiPC 2005)*, December 2005.

S. K. Sahoo, S. Krishnamoorthy, R. Panuganti, and P. Sadayappan. "Integrated Loop Optimizations for Data Locality Enhancement of Tensor Contraction Expressions" In *Proceedings of Supercomputing (SC 2005)*, November 2005.

S. K. Sahoo, R. Panuganti, S. Krishnamoorthy, and P. Sadayappan. "Cache Miss Characterization and Data Locality Optimization for Imperfectly Nested Loops on Shared Memory Multiprocessors". In *Proceedings of the 19th IEEE International Parallel & Distributed Processing Symposium (IPDPS 2005)*, April 2005.

S. Krishnamoorthy, G. Baumgartner, C. Lam, J. Nieplocha, and P. Sadayappan. "Efficient Layout Transformation Support for Disk-based Multidimensional Arrays". In *Proceedings of the 11th Annual International Conference on High Performance Computing (HiPC 2004)*, December 2004.

S. Krishnan, S. Krishnamoorthy, G. Baumgartner, C. Lam, J. Ramanujam, P. Sadayappan, and V. Choppella. "Efficient Synthesis of Out-of-Core Algorithms Using a Nonlinear

Optimization Solver". In Proceedings of the 18th International Parallel & Distributed Processing Symposium (IPDPS 2004), April 2004.

S. Krishnan, S. Krishnamoorthy, G. Baumgartner, D. Cociorva, C. Lam, P. Sadayappan, J. Ramanujam, David E. Bernholdt, and V. Choppella. "Data Locality Optimization for Synthesis of Efficient Out-of-Core Algorithms". In *Proceedings of the 10th Annual International Conference on High Performance Computing (HiPC 2003)*, December 2003.

S. Krishnamoorthy, G. Baumgartner, D. Cociorva, C. Lam, and P. Sadayappan. "Efficient Parallel Out-of-core Matrix Transposition". In *Proceedings of IEEE International Conference on Cluster Computing (CLUSTER 2003)*, December 2003.

### FIELDS OF STUDY

Major Field: Computer Science and Engineering

# TABLE OF CONTENTS

# Page

| Abst | ract . | ii                                                        |

|------|--------|-----------------------------------------------------------|

| Dedi | cation | iiv                                                       |

| Ackı | nowled | lgments                                                   |

| Vita |        | vii                                                       |

| List | of Tab | les                                                       |

| List | of Fig | ures                                                      |

| List | of Alg | orithms                                                   |

| Chap | oters: |                                                           |

| 1.   | Intro  | duction                                                   |

| 2.   | Effec  | ctive Automatic Parallelization of Stencil Computations 6 |

|      | 2.1    | Introduction                                              |

|      | 2.2    | Background and Problem Statement                          |

|      | 2.3    | Inhibition of Concurrent Start                            |

|      |        | 2.3.1 Concurrent Start in the Non-Tiled Space             |

|      |        | 2.3.2 Inhibition of Concurrent Start in the Tiled Space   |

|      | 2.4    | Overlapped Tiling                                         |

|      | 2.5    | Split Tiling                                              |

|      | 2.6    | Code Generation                                           |

|      | 2.7    | Experimental Evaluation                                   |

|      | 2.8    | Related Work                                              |

|      | 2.9    | Conclusions                                               |

| 3. | Data | Layout Transformation for Disk Resident Arrays                  | . 32  |

|----|------|-----------------------------------------------------------------|-------|

|    | 3.1  | Introduction                                                    | . 32  |

|    | 3.2  | Disk I/O Characterization                                       | . 35  |

|    | 3.3  | Out-of-core Matrix Transposition                                | . 38  |

|    |      | 3.3.1 Problem Definition                                        | . 38  |

|    |      | 3.3.2 Matrix Transposition Algorithms                           | . 40  |

|    |      | 3.3.3 Formulation of Transposition Algorithms                   | . 43  |

|    |      | 3.3.4 Performance Analysis                                      | . 45  |

|    |      | 3.3.5 Sequential Out-of-Core Matrix Transposition               | . 50  |

|    |      | 3.3.6 Parallel Out-of-Core Matrix Transposition                 | . 55  |

|    |      | 3.3.7 Experimental Evaluation                                   | . 65  |

|    | 3.4  | Out-of-core Matrix Reblocking                                   | . 68  |

|    |      | 3.4.1 Background                                                | . 68  |

|    |      | 3.4.2 Problem Definition                                        | . 69  |

|    |      | 3.4.3 Algorithm Design                                          | . 71  |

|    |      | 3.4.4 Implementation                                            | . 80  |

|    |      | 3.4.5 Experimental Evaluation                                   | . 88  |

|    | 3.5  | Related Work                                                    | . 95  |

|    | 3.6  | Conclusion                                                      | . 96  |

| 4. | Com  | putation Mapping and Scheduling                                 | . 97  |

|    | 4.1  | Introduction                                                    | . 97  |

|    | 4.2  | Tensor Contraction Engine                                       |       |

|    | 4.3  | Abstraction for Block-Sparse Matrices                           |       |

|    | 4.4  | Computation Abstraction: Task Pool                              |       |

|    | 4.5  | Hypergraph Partitioning Problem                                 |       |

|    | 4.6  | Optimizing Computations on In-Memory Data                       |       |

|    | 4.0  | 4.6.1 Problem Definition                                        |       |

|    |      | 4.6.2 Communication Minimization: Locality-Aware Load-balancing |       |

|    |      | 4.6.3 Experimental Evaluation                                   |       |

|    | 4.7  | Optimizing Computations on out-of-core data                     |       |

|    | т./  | 4.7.1 Problem Definition                                        |       |

|    |      | 4.7.2 Disk I/O Minimization: One-Level Partitioning             |       |

|    |      | 4.7.2 Disk f/O minimization. One-Level ratificating             |       |

|    |      | 4.7.4 Integrated Approach: Two-Level Partitioning               |       |

|    |      | 4.7.4 Integrated Approach. Two-Level Faithforming               |       |

|    | 4.8  | Related Work                                                    |       |

|    | 4.8  |                                                                 |       |

|    | 4.7  | Conclusion                                                      | . 130 |

| 5.    | Conclusions and Future Directions | 133 |

|-------|-----------------------------------|-----|

| Bibli | ography                           | 136 |

# LIST OF TABLES

| Ta  | able                                                                | Page  |

|-----|---------------------------------------------------------------------|-------|

| 3.  | 1 Configuration of systems used for I/O characterization            | 35    |

| 3.  | 2 Illustration of our matrix transposition algorithm                | . 54  |

| 3.  | 3 Illustration of our parallel matrix transposition algorithm       | . 63  |

| 3.4 | 4 Parallel matrix transposition time on ia64-osc – $N=64K$          | . 66  |

| 3.: | 5 Parallel matrix transposition time on ia64-osc – $N=128K$         | . 67  |

| 3.  | 6 Parallel matrix transposition time on amd-osc – $N=64K$           | . 67  |

| 3.' | 7 Parallel matrix transposition time on amd-osc – $N=128K$          | . 67  |

| 3.  | 8 Configuration of systems on which matrix reblocking was evaluated | . 92  |

| 3.  | 9 Matrix reblocking evaluation on ia64-osc – N=32K                  | . 93  |

| 3.  | 10 Matrix reblocking evaluation on ia64-osc – N=64K                 | . 93  |

| 3.  | 11 Matrix reblocking evaluation on ia64-pnl – N=64K (#procs=1,2)    | 94    |

| 3.  | 12 Matrix reblocking evaluation on ia64-pnl – N=64K (#procs=4)      | 94    |

| 4.  | 1 Out-of-core CCD sub-calculation – turnaround time                 | . 126 |

# LIST OF FIGURES

| Figu | re                                                          | Page |

|------|-------------------------------------------------------------|------|

| 2.1  | Imperfectly-nested one-dimensional Jacobi                   | . 8  |

| 2.2  | Fused one-dimensional Jacobi                                | . 9  |

| 2.3  | Single-statement form of one-dimensional Jacobi             | . 10 |

| 2.4  | Standard tiling for one-dimensional Jacobi                  | . 11 |

| 2.5  | Overlapped tiling for one-dimensional Jacobi                | . 11 |

| 2.6  | Split tiling for one-dimensional Jacobi                     | . 12 |

| 2.7  | Illustration of concurrent-start                            | . 14 |

| 2.8  | Overlapped tiling for two-dimensional Jacobi: top view      | . 18 |

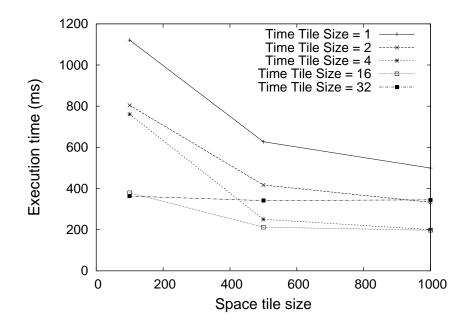

| 2.9  | Optimal space and time tile size for pipelined schedule 1   | . 28 |

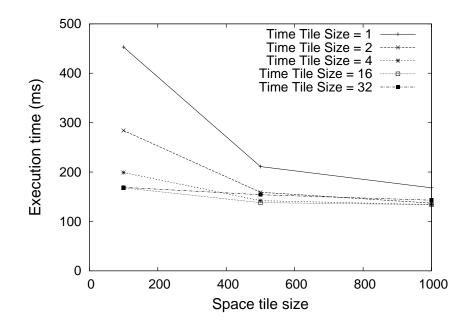

| 2.10 | Optimal space and time tile size for pipelined schedule 2   | . 29 |

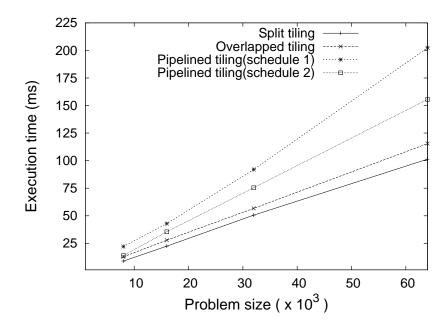

| 2.11 | One-dimensional Jacobi execution time, varying problem size | . 30 |

| 2.12 | One-dimensional Jacobi execution time, varying #procs       | . 31 |

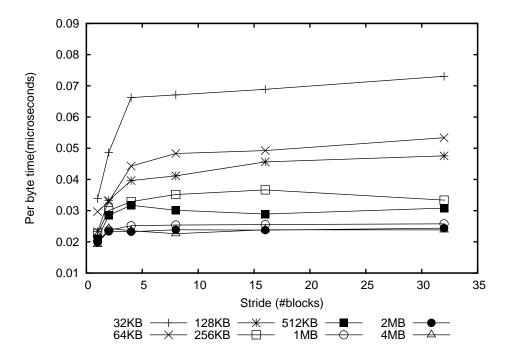

| 3.1  | Strided read times on amd-osc                               | . 36 |

| 3.2  | Strided write times on amd-osc                              | . 36 |

| 3.3  | Strided read times on ia64-osc                              | . 37 |

| 3.4 | Strided write times on ia64-osc                                                |

|-----|--------------------------------------------------------------------------------|

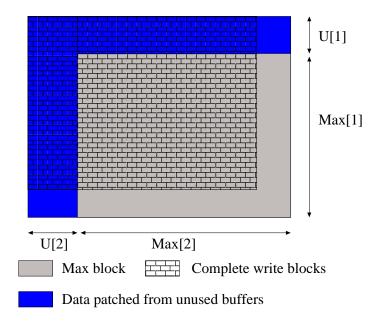

| 3.5 | Parallel matrix reblocking – in-place construction of complete write blocks 84 |

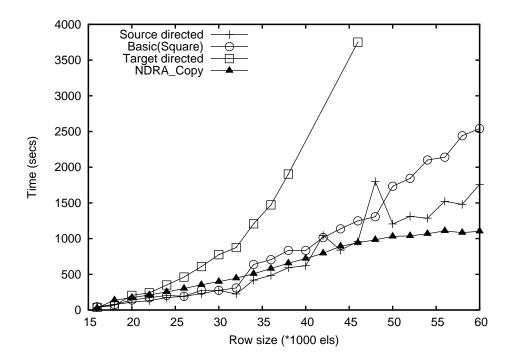

| 3.6 | Matrix reblocking time (brick size=1MB) – set-of-rows to set-of-columns . 89   |

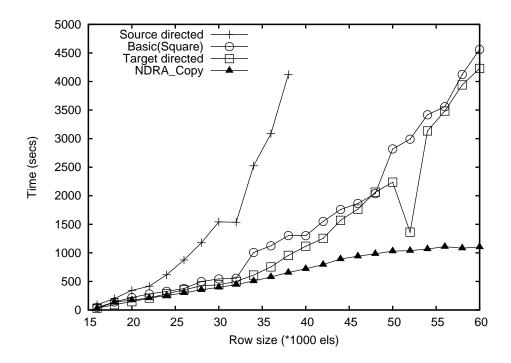

| 3.7 | Matrix reblocking time (brick size=1MB) – set-of-columns to set-of-rows . 90   |

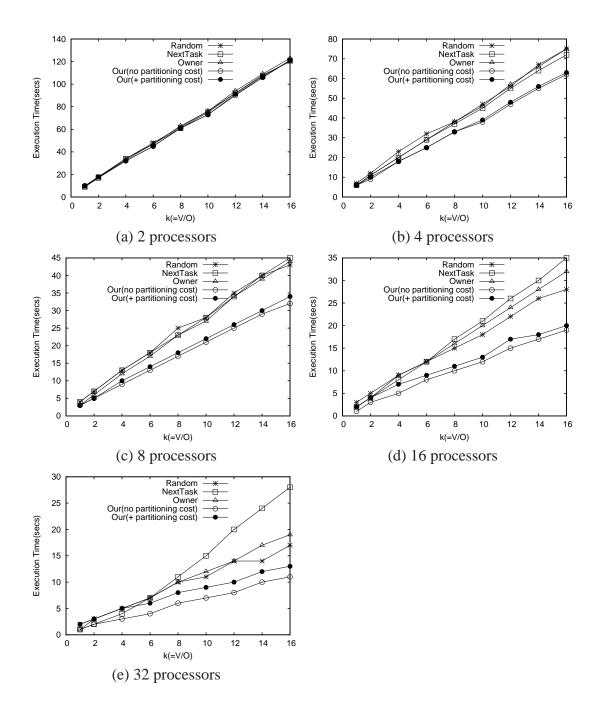

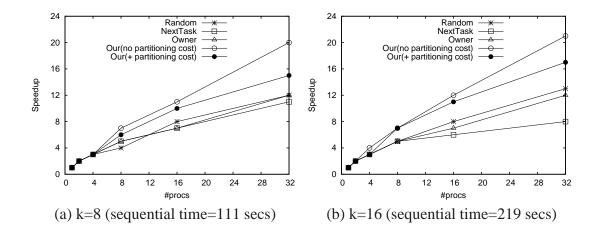

| 4.1 | Parallel block-sparse matrix multiplication – execution times                  |

| 4.2 | Parallel block-sparse matrix multiplication – scalability                      |

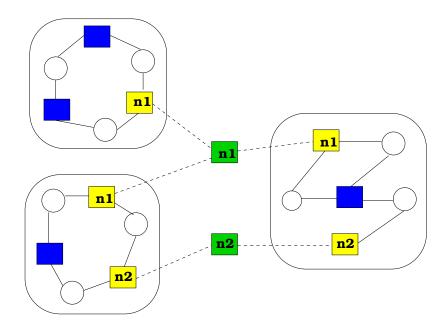

| 4.3 | Illustration of one-level partitioning                                         |

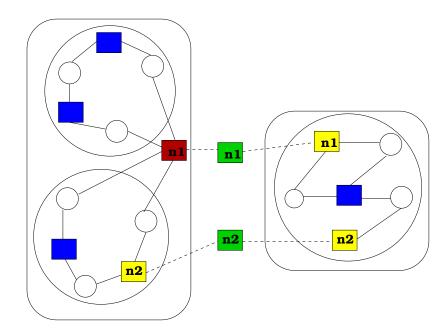

| 4.4 | Illustration of two-level partitioning                                         |

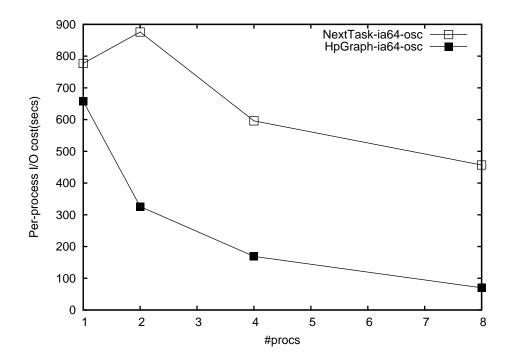

| 4.5 | Out-of-core CCD sub-calculation on ia64-osc – average I/O cost                 |

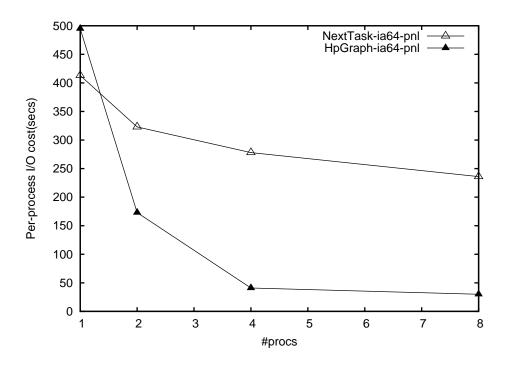

| 4.6 | Out-of-core CCD sub-calculation on ia64-pnl – average I/O cost                 |

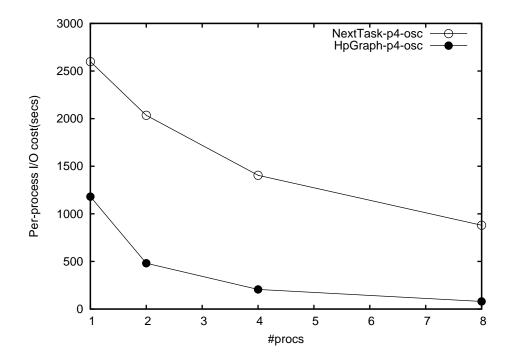

| 4.7 | Out-of-core CCD sub-calculation on p4-osc – average I/O cost                   |

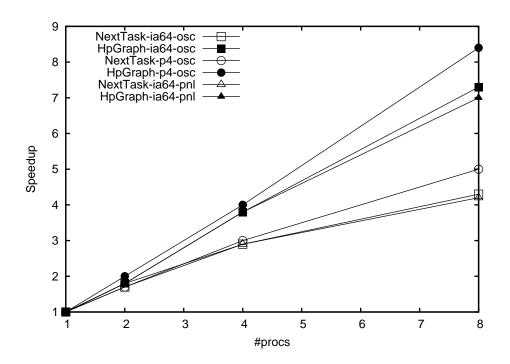

| 4.8 | Out-of-core CCD sub-calculation – speed-ups                                    |

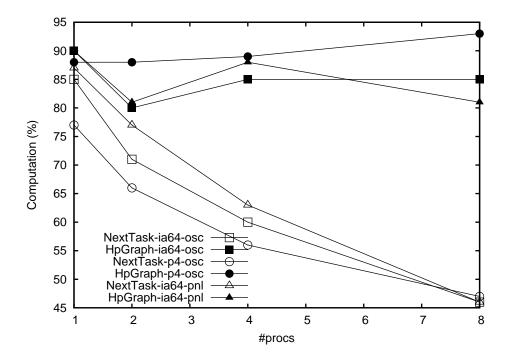

| 4.9 | Out-of-core CCD sub-calculation – percentage computation time                  |

# LIST OF ALGORITHMS

# Algorithm

# Page

| 2.1  | Computation/communication scheduling algorithm for split-tiling 23  |

|------|---------------------------------------------------------------------|

| 3.1  | Block transposition algorithm                                       |

| 3.2  | Eklundh's algorithm                                                 |

| 3.3  | Kaushik et al.'s algorithm                                          |

| 3.4  | Suh and Prasanna's algorithm                                        |

| 3.5  | Generic transposition algorithm                                     |

| 3.6  | Algorithm to determine the memory cost for a given template size 74 |

| 3.7  | Algorithm to determine template size for a single-pass solution     |

| 3.8  | Algorithm to determine a multi-pass solution                        |

| 3.9  | Algorithm for sequential implementation of layout transformation 80 |

| 3.10 | Pseudo-code to enumerate all load-balanced parallel Max blocks 87   |

| 4.1  | Abstraction for multi-dimensional block-sparse arrays               |

| 4.2  | Task pool abstraction                                               |

| 4.3  | Task pool illustration – block-sparse matrix multiplication         |

| 4.4  | Computation schedule for one-level partitioning                     |

| 4.5 | Computation schedule for a read-once partition | • | • | • | ••• | • | • | • • | • | • | • | • | • | • | 132 |

|-----|------------------------------------------------|---|---|---|-----|---|---|-----|---|---|---|---|---|---|-----|

| 4.6 | Two-Level partitioning algorithm: TwoLevel     |   |   |   |     |   |   |     |   |   |   |   |   |   | 132 |

### **CHAPTER 1**

#### **INTRODUCTION**

There have been dramatic strides in hardware performance of modern high-end systems. These improvements have been accompanied by a corresponding increase in the complexity of these systems. Modern parallel computers have increasingly large number of processors, deeper memory hierarchies, and higher processor clock speeds. This has resulted in an increasingly important role of exploitation of parallelism in the computation to utilize the available processors, and data locality to maximize the time spent in useful computation by processors.

The dramatic strides in hardware performance of modern high-end systems over the past decades have not been matched by a corresponding improvement in the ease of programming them. The increasingly complex hardware and communication architectures, while enabling high performance, have resulted in an increasing amount of detail being handled by the programmer to achieve that performance.

From a programmer's viewpoint, the complexity of the code required to implement a given algorithm or simulation is a function of the level of detail the programming model exposes to the programmer, the number of decisions and choices to be made, together with the level of detail required to manage performance-related aspects of the underlying hardware.

Developing scalable application codes on such systems requires an understanding and exploitation of the parallelism and locality in the computation. The computation needs to be parallelized such that good load balance is achieved. The distribution of the data amongst the processors needs to take into account the cost of data movement between the processors. In addition, movement of data between the different levels of the memory hierarchy needs to minimized to reduce the overall data movement cost. This is usually achieved by distinguishing the different levels of the memory hierarchy that incur different data movement costs. The programmer optimizes the execution of an application by matching the locality and parallelism identified in the application to the architectural abstraction exposed by the parallel programming model.

Parallel programming models provide a combination of data and control abstractions. The data abstraction divides the addressable memory in the system into units of locality. All elements in the same unit of locality are assumed to incur the same data movement cost. A simplified data abstraction that improves productivity ideally presents a uniform view of the memory in the system. On the other hand, achieving good scalability requires a data abstraction that can be efficiently mapped to the non-uniform deep memory hierarchy in modern parallel systems. This is typically achieved by creating one unit of locality for each processor memory, and distinguishing between access to the data in local memory and to that in non-local memory.

The control abstraction provides mechanisms to identify and express the parallelism in the computation. It also optionally provides mechanisms for automatic load balancing. The abstraction is either computation-centric, with parallelism specified in terms of data or functions used in the computation, or architecture-centric. In an architecture-centric control abstraction a fixed number of control flow units are defined, typically one per processor, and these are allowed to execute in parallel with user managing the synchronization between them. While an architecture-centric control abstraction can be easily mapped to the processors in a parallel system, computation-centric abstractions facilitate ease of programming. In addition, architecture-centric specification of parallelism encourages the programmer to partition the computation with implicit dependences between the tasks in a part. The absence of this information to the runtime makes automatic support for load-balancing a challenging task.

When an application's data does not fit into the collective physical memories of a parallel system, the data is stored on disk. Such data is referred to as *out-of-core* data. Virtual memory has been shown to inefficient in handling out-of-core scientific applications due to a lack of insights into the data access characteristics in the application. Explicit disk I/O mechanisms are used to move the data between the secondary storage and main memory. In programming out-of-core applications, a programmer has to contend with the orchestration of the movement of data between disk and memory, ensuring that the memory utilization does not exceed the size of the available physical memory, and scheduling the computation to operate only on the data in the physical memory. In computations based on the traditional collective disk I/O model, all processes collective move the data between the disks and the distributed memory, with each process subsequently performing communication to move the data into the local memory for processing.

We attempt to improve the performance of an application with limited impact on productivity. For regular loop-based programs operating on dense multi-dimensional arrays, we present an automatic parallelization technique that enables the concurrent start of execution by all processors. This avoids the pipelined startup overhead incurred by schedules generated by prevalent approaches. It also exposes the trade-off between communication volume, the number of communication start-ups, or computation cost and the parallelism in the application. Unlike existing loop transformation frameworks, this approach enables the user to choose between the various costs depending on the application and the balance of computation and communication costs in the target system. Chapter 2 presents the technique and evaluates the approach on stencil codes.

For less structured programs, we propose to reconcile the seemingly conflicting requirements of performance and productivity by presenting the user with multiple interoperable control and data abstractions, each at a different level of detail. This enables a programmer to realize an implementation of an algorithm using a high level abstraction, and incrementally optimize it improve its efficiency and scalability.

A key aspect of our approach to handle parallelism and data locality, including outof-core data, is the organization of the data into blocks that are globally addressable. A block is a subset of data that is stored in a single processor's memory or disk. A block is defined to be the basic unit of locality. The computation is defined in terms of sets of tasks operating on the blocks of data and dependences between them.

When the layout of the blocks does not match the access pattern in the computation, a performance penalty is incurred due to the lack of spatial locality. This is particularly severe in the context of out-of-core data. We present efficient data layout transformation algorithms to transform the blocking of multi-dimensional arrays, when the blocking required for different phases are very different. We first develop an out-of-core matrix transposition algorithm that takes into account the I/O characteristics of the target system. We then present a novel algorithm to solve the out-of-core matrix reblocking problem for multi-dimensional matrices of arbitrary sizes. This is topic of discussion in Chapter **3**.

The programmer specifies a task as a set of data blocks and a function that contains an efficient sequential implementation of an algorithm to process those blocks. The blocking of data ensures efficient data movement, while the tasks provide efficient sequential executions to process interacting blocks. Blocking of data thus enables us to leverage existing work on optimizing sequential computations.

This abstraction provides a computation-centric view of both locality and parallelism, thus presenting a simple abstraction to the user. On the other hand, the explicit specification of the locality and parallelism enables runtime mechanisms that map the data and tasks to the processors in a parallelism to automatically manage locality, dependences, and load balance in the execution of the program. We believe these features can enable the presentation of a high-level programming abstraction without compromising scalability and sequential efficiency.

We demonstrate the benefits of the approach in the context of tensor contractions arising from the quantum chemistry domain in Chapter 4. We present mechanisms for automatic management of load balance, disk I/O, and inter-process communication on the quantum chemistry computations expressed as sets of independent tasks on blocked data stored on disk. The objective is to minimize the volume of disk I/O while balancing the computation amongst the processors.

#### **CHAPTER 2**

## EFFECTIVE AUTOMATIC PARALLELIZATION OF STENCIL COMPUTATIONS

### 2.1 Introduction

Stencil computations represent a practically important class of computations that arise in many scientific/engineering codes. Computational domains that involve stencils include those that use explicit time-integration methods for numerical solution of partial differential equations (e.g., climate/weather/ocean modeling [100], computational electromagnetics codes using the Finite Difference Time Domain method [108]), and multimedia/imageprocessing applications that perform smoothing and other neighbor pixel based computations [45]. There has been some prior work from the computer science community that has addressed performance optimization of stencil computations (e.g., [99, 54, 53, 39]). Since stencil computations are characterized by a regular computational structure, they are amenable to automatic compile-time analysis and transformation for exploitation of parallelism and data locality optimization. However, as elaborated later through an example, existing compiler frameworks have limitations in generating efficient code optimized for parallelism and data locality.

Loop tiling is the key transformation to enable parallelization and data-locality optimization of stencil codes. Much research has been published on tiling of iteration spaces [52, 119, 118, 106, 29, 34, 92, 95, 49, 14, 50, 33, 51, 3]. With few exceptions (e.g., work of Griebl [42, 43]), research on performance optimization with tiling has generally focused on one or the other of the two complementary aspects: (a) data locality optimization [4, 3, 118, 106, 29]; or (b) tile size/shape optimization for parallel execution [34, 92, 9, 49, 14, 50, 33, 51]. Tiling for data locality optimization involves maximization of data reuse, i.e., tiling along directions of the data dependence vectors. But such tiling may result in inter-tile dependences that inhibit concurrent execution of tiles on different processors. To the best of our knowledge, no prior work has addressed in an integrated fashion, the issues of tiling for data locality optimization and load balancing for parallel execution. We first use the simple example of a one-dimensional Jacobi code to illustrate the problem and introduce two approaches we propose to avoid the problem: overlapped tiles and split tiles. As an example of a stencil computation, let us consider the one-dimensional Jacobi code shown in Figure 2.1. Optimizing this stencil computation for reduction of cache misses requires loop fusion and tiling; in order to fuse the two inner loops, loop skewing is needed. Frameworks have been previously proposed for data locality optimization of imperfectly nested loops. Using an approach proposed by Ahmed et. al. [3, 4] the loop nest can be transformed into the one shown in Figure 2.2 by first embedding the iterations in the imperfectly-nested loops into a perfectly-nested iteration space. Loop transformations and tiling can then be applied in the transformed perfectly-nested iteration space. The transformed iteration space can be subsequently translated into efficient code by reducing/eliminating the control overhead [60]. In this chapter, we focus on

```

for t = 0 to T-1

for i = 1 to N-1

S1: B[i] = (A[i-1]+A[i]+A[i+1])/3

for i = 1 to N-1

S2: A[i] = B[i]

```

Figure 2.1: Imperfectly-nested one-dimensional Jacobi

load-balanced parallel execution of tiled iteration spaces that have already been embedded into a perfectly-nested iteration space using a technique such as that developed in [4].

Figure 2.3 shows a single-statement form of the one-dimensional Jacobi code obtained by adding an additional dimension to array *A*. The flow dependences in this code are the same as that of the previously shown version, but there are no anti-dependences. Hence a single statement is sufficient in the loop body instead of a sequence of two statements, for update and copy, respectively, as seen in Figures 2.1 and 2.2. Although such a memoryinefficient code would not be used in practice, it is more convenient to use a singlestatement iteration space in explaining the main ideas in this chapter. However, the developed approach is not restricted to such single-statement loops, but is applicable to general multi-statement stencil codes such as the one in Figure 2.1. The experimental results presented later also use the memory-efficient multi-statement versions.

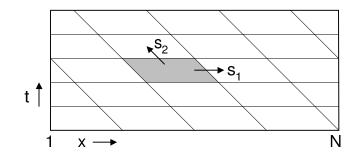

The perfect loop nest of Figure 2.3 has constant dependences (1,0), (1,1), and (1,-1). Tiling for data reuse optimization (e.g. using the approach presented in [2]) results in tiles of shape as shown in Figure 2.4. The horizontal axis corresponds to the spatial dimension, with time along the vertical dimension. Using a sufficiently large tile size along the time dimension facilitates significant data reuse within caches/registers. However, there are inter-tile dependences in the horizontal direction, inhibiting concurrent execution of tiles

```

for t = 0 to T-1

for i = 1 to N

if(i>=1 and i<=N-1)

S1:        B[i] = (A[i-1]+A[i]+A[i+1])/3

if(i>=2 and i<=N)

S2:        A[i-1] = B[i-1]</pre>

```

Figure 2.2: Fused one-dimensional Jacobi

by different processors. However, if the vertical tile size is reduced to one (i.e., tiling is eliminated along the time dimension), all tiles along the spatial dimension (adjoining the x-axis) can be executed concurrently. Thus there is a trade-off between achieving good data reuse and load balancing of parallel execution.

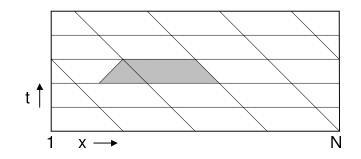

Instead of the *standard* tiling described above, consider the tiling shown in Figure 2.5. Starting with the tiles formed by the same hyperplanes, an additional triangular region is added to the left of the tile, overlapping with the points at the right end of the neighboring tile. With this tiling, the iteration points processed by the tiles are no longer disjoint. Some of the iterations are executed redundantly by two neighboring tiles. This results in an increase in the computation cost. But doing so eliminates the dependence between tiles along the horizontal direction. All processors can start executing in parallel, eliminating the initial processor idling that results with the pipelined parallel execution of tiles in Figure 2.4.

While standard tiling can enhance data locality in this context, overlapped tiling can both improve data locality and eliminate the overhead of pipelined parallelism, at the cost Figure 2.3: Single-statement form of one-dimensional Jacobi

of slightly increased computation time. However, the increased computational cost is independent of tile size. Therefore the fractional computation overhead is inversely proportional to the tile size in the direction of overlapped tiling, and can be made insignificant if a sufficiently large tile size is chosen along the time dimension.

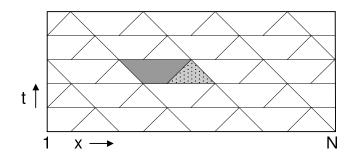

An alternate approach, shown in Figure 2.6, splits the interior of each tile into two subtiles, where the points in only one of the two sub-tiles (shaded) are dependent on points in the neighbor tile, while the points in the other sub-tile are not dependent on any neighboring tile's points, and therefore executable concurrently. With this approach, each standard tile is split into two sub-tiles, and load-balanced concurrent execution is possible as a sequence of two steps: first all non-dependent sub-tiles are concurrently executed and communicate with the neighbor tiles, and then the dependent sub-tiles are all concurrently executed.

The chapter is organized as follows. Section 2 defines the problem addressed in this chapter. In Section 3, we characterize the conditions under which tiled iteration spaces can benefit from overlapped/split tiling. In Section 4, we show how to transform a given tiled iteration space in order for overlapped/split tiling to be applicable. Section 5 discusses code generation and Section 6 analyzes the cost benefits of overlapped tiling. Section 7 provides experimental results that demonstrate the benefits of overlapped/split tiling. In Section 8, we discuss related work and conclude in Section 9 with a summary.

Figure 2.4: Standard tiling for one-dimensional Jacobi.  $s_1$  and  $s_2$  denote the inter-tile dependences.

Figure 2.5: Overlapped tiling for one-dimensional Jacobi

### 2.2 Background and Problem Statement

This section introduces some standard background on the polyhedral model of computation, and defines the problem addressed. Consider a perfectly-nested loop nest with nlevels of nesting. The *iteration space polyhedron* defines an n-dimensional set of points, characterized by a set of bounding hyperplanes and modeled as  $B.I \ge b$  where I is the

Figure 2.6: Split tiling for one-dimensional Jacobi

iteration vector. The rows  $b_i$  of *B* define the normals to the corresponding bounding hyperplanes. For example, the iteration space for the 1-D Jacobi example is

$$\begin{pmatrix} 1 & 0 \\ -1 & 0 \\ 0 & 1 \\ 0 & -1 \end{pmatrix} \cdot \begin{pmatrix} t \\ i \end{pmatrix} \ge \begin{pmatrix} 0 \\ -T+1 \\ 1 \\ -N+1 \end{pmatrix}$$

The dependences in the computation can be represented by a matrix D where each column defines a dependence vector. The dependences in the 1-D Jacobi example are

$$D = \left(\begin{array}{ccc} d_1 & d_2 & d_3\end{array}\right) = \left(\begin{array}{ccc} 1 & 1 & 1 \\ -1 & 0 & 1\end{array}\right)$$

Assume that we are given a set of *tiling hyperplanes* that tile the iteration space. These hyperplanes are represented by a matrix H, where each row represents the normal vector of a tiling hyperplane. For example, the tiling hyperplanes corresponding to Figure 2.4 are represented as

$$H = \left(\begin{array}{c} h_1 \\ h_2 \end{array}\right) = \left(\begin{array}{cc} 1 & 0 \\ 1 & 1 \end{array}\right)$$

A tiling defined by a set of tiling hyperplanes is *legal* if each tile can be executed atomically and there exists a valid total ordering of the tiles. Intuitively, a tiling is legal if no two tiles mutually depend on each other. It can be shown [52] that this validity condition is given by

$$H.D \ge 0$$

A schedule has a *concurrent start* property if all processors can start execution in parallel, without any pipeline start-up delay. Such a schedule is referred to as a concurrent-start schedule.

**Problem Statement.** Consider a given (non-tiled) iteration space in which a concurrentstart schedule is possible. However, for a given tiling of this space defined by a set of tiling hyperplanes, it is possible that the tile dependencies in the corresponding tiled iteration space inhibit concurrent start. We consider the following question: How can concurrent start be achieved in the tiled iteration space? Our first goal is to characterize analytically the situations in which tiling inhibits concurrent start. Next, we develop two approaches, *overlapped* tiling and *split* tiling, that enable concurrent start in the tiled space and recover the load-balancing properties lost due to tiling.

#### 2.3 Inhibition of Concurrent Start

If the original non-tiled iteration space does not have a concurrent start schedule, tiling cannot enable such a schedule. However, if concurrent start is possible in the absence of tiling, the introduction of tiling can potentially inhibit this concurrent start. This section characterizes the conditions under which a non-tiled space supports a concurrent start schedule, and then derives a concurrent start inhibition condition for the tiled space. For simplicity of presentation, the discussion assumes an iteration space with a single statement, but we have defined a general version of the technique for multi-statement iteration spaces.

#### 2.3.1 Concurrent Start in the Non-Tiled Space

First, we describe the condition for the existence of concurrent start in the original nontiled iteration space. Consider, for example, dependence vectors (1,0) and (0,1). Two

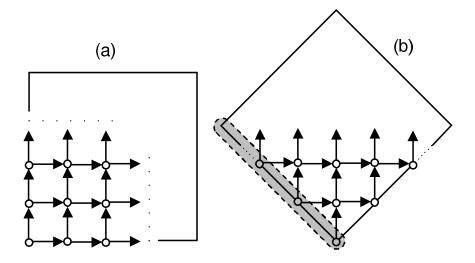

Figure 2.7: Illustration of concurrent-start. Iteration spaces with (1,0) and (0,1) dependencies: (a) concurrent start is not possible (b) concurrent start is possible from the gray boundary.

iteration spaces with these dependences are shown in Figure 2.7. In Figure 2.7(a), the parallel computation has to begin from the origin (0,0) and suffers from pipeline start-up overhead. On the other hand, the iteration space in Figure 2.7(b) can be traversed by all processors in parallel starting from the boundary shown in gray.

In general, the presence of concurrent start in an iteration space depends on the boundaries that define the iteration space polyhedron. An iteration space supports concurrent start if there exists a bounding hyperplane that does not contain a dependence, i.e. carries all dependences. A hyperplane contains a dependence if both the source and destination iteration points of the dependence are contained in the hyperplane. Since the rows  $b_i$  of *B* define the normal vectors of the bounding hyperplanes, this property is represented by the condition

$$\exists b_i \in B : \forall d_i \in D : b_i d_i > 0$$

Note that this condition is independent of the tiling hyperplanes. We will refer to this property as the *point-wise concurrent start condition*. When this condition does not hold, no tiled iteration space can have concurrent start. For the 1-D Jacobi example, the condition holds because the normal vector  $b_1 = (1 \ 0)$  for one of the bounding hyperplanes satisfies  $b_1.d_j > 0$  for all dependence vectors  $d_j$ .

#### 2.3.2 Inhibition of Concurrent Start in the Tiled Space

Next, we consider the condition for the inhibition of the concurrent start condition in the tiled iteration space. Given the tiling hyperplanes and their normal vectors  $h_i \in H$ , we define the *shift vector s<sub>i</sub>* for the hyperplane with  $h_i$  as normal to be a vector connecting two instances of the same hyperplane, while traveling parallel to all other hyperplanes. Clearly, the following holds for the set *S* of shift vectors:

$$\forall s_i \in S : \forall j \neq i : h_j.s_i = 0$$

For the 1-D Jacobi example, we will use shift vectors

$$S = \left(\begin{array}{cc} s_1 & s_2 \end{array}\right) = \left(\begin{array}{cc} 0 & 1 \\ 1 & -1 \end{array}\right)$$

as illustrated in Figure 2.4.

The execution of two adjacent tiles should be ordered if there is a dependence vector  $d_j$  such that for some iteration points  $i_1$  and  $i_2$  related by  $d_j$ , point  $i_1$  is in one of the tiles and point  $i_2$  is in the other one. Note that this is possible only if there is a dependence that passes through the hyperplane that separates the two tiles — in other words, if the following condition holds

$$\exists d_k \in D : h_i.d_k \neq 0$$

When this condition is satisfied for a given hyperplane with  $h_i \in H$ , the shift direction  $s_i$ along that dimension *carries the inter-tile dependence*. For the 1-D Jacobi example, both  $s_1$  and  $s_2$  carry inter-tile dependencies (for example,  $h_1.d_1 > 0$  and  $h_2.d_1 > 0$ ).

The inter-tile dependences can introduce dependence directions that do not exist in the original iteration space. The concurrent start condition is *inhibited in the tiled iteration space*, if for some boundary  $b_i$ , the concurrent start condition is satisfied by the dependences in the original iteration space, but not by the inter-tile dependences in the tiled iteration iteration space. A tiling inhibits concurrent start if

$$\exists b_i \in B, h_i \in H, d_k \in D : b_i D > 0 \land b_i s_i = 0 \land h_i d_k \neq 0$$

When the above condition is true, there exists an inter-tile dependence within a hyperplane parallel to the boundary  $b_i$ , precluding concurrent execution of all the tiles in the boundary. Thus, concurrent start is inhibited even though the original iteration space supports it. This situation occurs for the 1-D Jacobi example due to bounding plane normal  $b_1 = (1 \ 0)$ , tiling hyperplane normal  $h_1 = (1 \ 0)$ , and any dependence  $d_k$  for k = 1...3.

### 2.4 Overlapped Tiling

The basic idea behind overlapped tiling is to eliminate certain inter-tile dependencies by "duplicating" points in the original iteration space. As a result, the same iteration point can be a member of two neighboring tiles (i.e., the tiles can overlap). This section outlines a constructive procedure to determine overlapping tiles that eliminate the inter-tile dependences, which removes the inhibition on concurrent start. The key step is the construction of a *companion hyperplane* that eliminates the dependence along a desired direction. The new tile will not have any incoming dependence along the direction in which the dependence was eliminated.

In standard tiling, a hyperplane with a normal vector  $h_i$  defines two faces of the tile. We will denote these faces as  $h_i(l)$  (the back face) and  $h_i(l+1)$  (the front face). The front face is shared with the subsequent tile along the shift direction defined by shift vector  $s_i$ . The back face  $h_i(l)$  has no incoming dependences if  $h_i.D \ge 0$ . On the other hand, the front face  $h_i(l+1)$ , by the tiling validity condition, does not have any incoming dependences. All dependences between the hyperplanes can be eliminated if the back face of the tile is replaced by an overlapped hyperplane with a normal vector  $h'_i$  such that

$$\forall d_i \in D : h'_i . d_i \leq 0$$

Note that the hyperplanes span the iteration space and any vector in the iteration space; hence, the companion hyperplane can be defined as a linear combination of the existing hyperplanes. Scaling a given hyperplane vector  $h_i$  does not eliminate any additional dependences. In addition, we are interested in the companion hyperplane that forms the back face of the tile. Thus, it is constructed by going "backwards" on the other hyperplanes, represented by a negative linear combination of the hyperplanes, and is given by:

$$h_i.D \ge 0 \Rightarrow h_i' = h_i - \sum_{j \ne i} k_j.h_j \wedge h_i'.D \le 0 \wedge k_j > 0$$

Such a companion hyperplane eliminates dependences along a shift vector. This procedure is repeated for every hyperplane/shift vector that inhibits concurrent start.

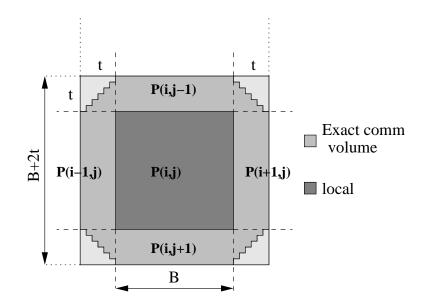

Consider *n*-dimensional Jacobi iteration with an n + 1 dimensional iteration space, and an *n* dimensional data space, with a range of *N* along each dimension. Let *B* be the space tile size along each of the *n* space dimensions. Let *p* be the number of processors organized in an n-dimensional grid.  $B = N/\sqrt[n]{p}$ . Let *t* be the time tile size.

Figure 2.8: Overlapped tiling for two-dimensional Jacobi: top view

The schedule for overlapped tiling requires the processors to cycle to maintain load balance. We illustrate the determination of communication frequency using a simpler variation. Starting from orthogonal tiling, both planes can be swiveled partially to form trapezoid-like tiles for 1-D Jacobi, and a square pyramid for two-dimensional Jacobi, top view for which is shown in Figure 2.8. This overlapped tiling scheme has the same communication volume as the original one, but double the number of startups. However, code generation is simpler for this case due to the absence of the need to cycle. The number of startup's do not matter when the communication volume is higher; this is particularly true for higher dimensional Jacobi (greater than 1) for which the space tile size comes into the volume.

Consider the overlapped tiling scheme that is obtained from orthogonal tiling. The point-wise difference between the coordinates of a given processor and any of its neighbors in the processor space is an *n*-vector, and each of its *n* components being 1, 0, or -1.

Discounting the all zeros case, we have  $3^n - 1$  neighbors. Hence, the number of communication startups per tile (without forwarding) is given by:

$$S_1 = 3^n - 1 \tag{2.1}$$

For example, for three-dimensional Jacobi, we have 8 corners, 12 edges, and 6 faces, i.e., a total of 26 (=  $3^3$ -1) neighbors to send and receive data to/from to compute the overlapped tile.

With communication forwarding, the number of communication startups per tile can be reduced to 2n (one for each of the faces).

$$S_1' = 2n \tag{2.2}$$

Similarly the number of startups for the original schedule without and with forwarding are:

$$S_2 = 2^n - 1 (2.3)$$

$$S_2' = n \tag{2.4}$$

The exact communication volume assuming orthogonal tiling is given by:

$$V = \sum_{i=1}^{n} {n \choose n-i} 2^{i} B^{(n-i)} f(i,t)$$

$$\approx 2nt B^{n-1} \text{ when } t \ll B$$

(2.5)

where

$$f(k,t) = \sum_{i_{n-k+1}=1}^{t-1} \dots \sum_{i_n=1}^{i_{(n-1)}} i_n$$

(2.6)

The communication volume for the original schedule reduces to:

$$V = \sum_{i=1}^{n} {n \choose n-i} B^{(n-i)} f(i,2t)$$

$$\approx 2nt B^{n-1} \text{ when } t \ll B$$

(2.7)

The communication schedule and the data being communication can be quite complex for higher dimensions. Adding a small number of points to the communication volume greatly simplifies code generation. In Figure 2.8, the points in each of the four corners are those that can be added. The total communication volume then becomes:

$$V' = (B+2t)^{n} - B^{n}$$

=  ${}^{n}C_{1}B^{n-1}(2t) + {}^{n}C_{2}B^{n-2}(2t)^{2}$

+ ...+  $(2t)^{n}$  (2.8)

$\approx 2ntB^{n-1}$  if  $t \ll B$

=  $\Theta(tB^{n-1})$  (2.9)

For *n* = 2:

$$V' = 4tB + 4t^2$$

# 2.5 Split Tiling

Overlapped tiling eliminates inter-tile dependences by redundantly computing portions of a tile. While eliminating dependences, this approach increases the overall amount of computation. In this section we leverage the idea of dependence inhibition to develop an alternative approach, referred to as *split tiling*, in order to enable concurrent start without the computation overhead. In split tiling, rather than redundantly computing a portion of the predecessor tile along a dimension, the processor executing the predecessor tile first computes that portion and sends the results to its successor along that dimension. We show that for stencil computations, a tile sub-region can be identified such that this sub-region can be executed in parallel in all tiles. This enables concurrent start. We outline an algorithm that divides a tile into sub-regions and schedules the computation and communication to achieve concurrent start and load-balanced execution in which all processors execute the same amount of work in all the steps in the schedule.

A tile in a stencil computation is bounded by the hyperplane instances:

$$\forall I, B.I \ge b, h_j \in H : h_j.I \ge lo_j, h_j.I \le hi_j$$

where two parallel instances of each hyperplane are defined, one bounding the tile below along that dimension and another bounding the tile from above.

Along a dimension j, dependence inhibition identifies a partner hyperplane such that the region enclosed by the partner hyperplane  $(h'_j)$  in the positive direction  $(h'_j.I \ge lo'_i$  can be computed independently of the rest of the tile. This region was redundantly computed in the overlapped tiling approach.

**Definition 1.** The independent region along a dimension j is denoted by  $\neg j$ . The rest of the tile along that region will be denoted by j.

In the subsequent discussion, it should be clear from the context whether j refers to the dimension or to the complement of the independent region along that dimension.

The region  $\neg j$  is defined by making the partner hyperplane to be bounded from below along that dimension:

$$\forall I, B.I \ge b, h_k \in H, k \neq j : h_k.I \ge lo_k, h_k.I \le hi_k$$

$$\forall I, B.I \ge b : h'_j.I \ge lo'_k, h_j.I \le hi_j$$

Note that the hyperplanes along all the other dimensions remain unchanged.

A tile can be divided into these two regions along each of the dimensions. The various intersections of these regions divides the tile into  $2^k$  tile components for k such dimensions. We only consider dimensions along which there is potential for dependence inhibition, which would eliminate the time dimension. For example, a tile in the 2-D Jacobi code with x and y as the dimensions can be divided into the components  $\neg x \cap \neg y$ ,  $\neg x \cap y$ ,  $x \cap \neg y$ , and  $x \cap y$ .

From the definition of independent region, a tile component  $\neg i \cap ...$  is not dependent on its predecessor along dimension *i*. Thus, the tile component that is the intersection of the independent tile region along all the processors can be computed in parallel, without any communication — that is, all processors can start executing this in parallel, resulting in concurrent start.

Consider the tile component  $i \cap \ldots$ , where all other tile regions are independent. This tile component does not carry any dependence along any dimension other than *i*. The region in the predecessor tile that it depends on is derived as the tile-component with the same hyperplanes along all other dimensions as the tile component, with the hyperplanes along dimension *i* replaced by the lower-bounding hyperplane for this tile becoming the upperbounding hyperplane, and the partner hyperplane for dependent inhibition becoming the lower-bounding hyperplane. This is the tile component  $\neg i \cap \ldots$  Thus, the tile component  $i \cap \ldots$  can be computed once the boundary along *i* computed by  $\neg i \cap \ldots$  in the predecessor tile.

In general, for each dimension *i* along which a tile component is dependent, the inter-tile boundary is computed by the tile component in the predecessor tile obtained by replacing *i* by  $\neg i$  For example, the tile component  $x \cap y$  in the 2-D Jacobi code can be computed after

- 1: If (n==1), say a dimension *x*. Compute  $\neg x$ , send and receive the result along the *x* dimension, compute *x* and return.

- 2: Execute algorithm for (n-1)-dimensional stencil computation for all dimensions except one, say z. Thus all values computed will be for those independent along z (all tile sections have  $\neg z$  as the z dimension component).

- 3: Send all computed values along the z dimension.

- 4: Execute algorithm for n-dimensional stencil computation for all dimensions except z. But this time, all values computed will be dependent for dependent regions along *z*.

Algorithm 2.1: Computation/communication scheduling algorithm for split-tiling

the shared boundary with  $\neg x \cap y$  is received from the predecessor along *x*, and the one with  $x \cap \neg y$  is received from the predecessor along *y*.

Algorithm 2.1 presents a scheduling algorithm with  $2^n - 1$  communication steps for an *n*-dimensional stencil computation. In this recursive formulation, the number of communication steps is given by :

$$L(n) = 2 * L(n-1) + 1$$

with L(1)=1; that is,  $L(n) = 2^n - 1$ . Note that this approach does not incur any addition computation cost. In addition, only inter-tile boundaries in the spatial dimensions are communicated, thus incurring the same communication volume cost as standard tiling.

### **2.6 Code Generation**

In this section, we discuss the generation of the code for the iteration space with the overlapped and split tiles. We describe the derivation of the parameters necessary to utilize the code generation framework described by Ancourt and Irigoin [7].

Each tile in the tiled iteration space is identified by a tile origin. The execution of the tiled iteration space is defined as the traversal of the tiles in terms of their origins, together with the execution of the iterations mapped to each tile as it is traversed.

The origin of the tiled iteration space defined to be the origin of the original iteration space. Given the origin, all the tile origins can be enumerated as linear combinations of the shift vectors. The tile size is defined as the distances between the tile origins along the shift vector, and is embedded in the specification of the shift vector itself.

The matrix of shift vectors specifies the traversal order of the tile origins. The shift vectors are ordered to enable an outer loop along the direction  $b_i$  so that there is parallelism-inner synchronization-outer.

Given the tile origin  $x_0$ , defined equivalently in terms of the shift vectors or as iteration points in the original iteration space, each of the hyperplanes bounding the tiles can be identified by a point in it. For hyperplanes  $h_i$  along which no overlap is identified as necessary, the iteration points x in the iteration space that form this tile satisfy the following conditions:

$$h_i \cdot x \ge h_i \cdot x_0 \wedge h_i \cdot x < h_i \cdot (x_0 + s_i)$$

Note that  $x_0$  is a vertex on all the non-overlapped hyperplanes that form the back face of the tile.  $x_0 + s_i$  is a point on the front face of the tile for all hyperplanes  $h_i$ . Since overlapping does not change the front face, this is also true for hyperplanes that utilize overlap.

When an overlapped hyperplane is identified along a dimension, we replace the back face of the original hyperplane  $h_i$  by an overlapped hyperplane  $h'_i$ . Since  $h'_i$  is constructed from  $h_i$  by only shifting it along the other hyperplanes, the point  $x_0 + \sum_{j \neq i} s_j$  is a valid point on it irrespective of the choice of  $h'_i$ . Thus the boundary conditions for the tile for these hyperplanes is given by:

$$h_{i.x} \ge h_{i.}(x_0 + \sum_{j \neq i} s_j) \land h_{i.x} < h_{i.}(x_0 + s_i)$$

Given the tile origins and their traversals, and the shape of the overlapped tile, the code generation procedure of Ancourt and Irigoin [7] can be used to generate code. The generated code would have n outer tile space loops, each corresponding to a tiling hyperplane, and inner loops enumerating all iterations belonging to a tile. Let us assume that k of the n hyperplanes have been identified for overlapped tiling. Overlapped tiling enables concurrent start along a hyperplane by eliminating any inter-tile dependence along that hyperplane. Hence, the tile space loops corresponding to the remaining n - k hyperplanes carry all inter-tile dependences, and can be run sequentially as the outer loops, and the k tile space loops corresponding to overlapped tiling hyperplanes can all be run in parallel by mapping to a k-dimensional or lower dimensional processor space.

The traversal of tile origins for split tiling is the same as that for standard tiling. The intra-tile code is generated for the various tile components by scanning the polytopes derived by specifying the appropriate hyperplane instances that bound the tile component, as defined earlier. The appropriate hyperplane boundaries between sub-tiles define the data to be communicated between processors for the communication phases, as discussed earlier.

### 2.7 Experimental Evaluation

Both the proposed tiling schemes—overlapped tiling and split tiling—enable loadbalanced tiled execution of stencil codes that inherently satisfy the concurrent-start criterion. The degree of exploited concurrency is the same with both schemes; they differ in the computation/communication overheads relative to standard tiling. With overlapped tiling, there is a small amount of computational overhead and also a small increase in the total communication volume. Split tiling requires no additional redundant computations and requires exactly the same total communication volume as standard tiling, but requires additional messages, i.e., incurs a higher message-startup-cost overhead.

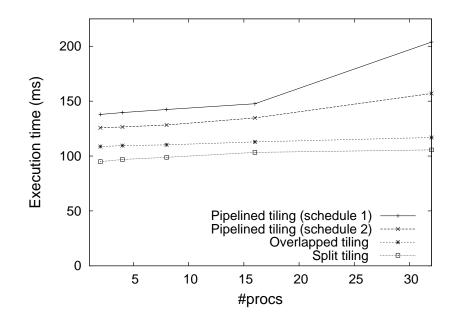

Below, we report experimental results comparing overlapped/split tiling with standard (pipelined) tiling for the one-dimensional Jacobi code. The experiments were conducted on a cluster consisting of 32 compute nodes each of which is a 2.8 GHz dual-processor Opteron 254 (single core) with 4GB of RAM and 1MB L2 cache, running Linux kernel 2.6.9. We used one processor per node in our experiments. The code was compiled using the Intel C Compiler with -O3 optimization flag.

The iteration space of one-dimensional Jacobi has a space dimension and a time dimension. Two versions of pipelined schedule were implemented: (i) one in which the processor space was mapped along the time dimension and time along the space, and (ii) the other one in which the processors were distributed in a block-cyclic fashion to execute tiles along time dimension.

First we conducted experiments to determine the optimal time tile size and space tile size for the two pipelined schedules. The experiments were conducted for 1000 time steps on 32 processors for a total problem size of 64000 elements. The execution times are shown in Figures 2.9 and 2.10. The number of communication startups decreases with an increase in the spatial tile size. This typically results in a decrease in the execution time with an increase in the space tile size. But for larger space tile sizes, the pipeline startup costs increase thus dominating and increasing the execution time. Increase in the time tile size reduces the number of time tiles and hence the number of synchronizations. But larger time tile sizes as in the case of larger space tile sizes increase the pipeline startup costs. Hence an increase in the time tile size decreases the execution time until the pipeline startup costs begin to dominate. The execution times for both the pipelined schedules, as inferred from

the experiments, are minimum for a time tile size of 16 and space tile size of 1000. Hence a time tile size of 16 and space tile size of 1000 were used for subsequent evaluation of the schemes.

For overlapped and split tiling, the space tile size is fixed to be N/nproc, where N is the space dimension size and nproc is the number of processors used for parallel execution. The time tile size is chosen to be 16 to match the choice for the pipelined schedules.

Given these choices of space and time tile sizes, the performance of the four schemes for various problem sizes is shown in Figure 2.11. The split and overlapped tiling schemes result in a linear increase in execution time with problem size, unlike the pipelined tiling solutions. The improvement in execution time achieved by split and overlapped tiling schemes with increase in problem size is due to the better exploitation of data locality. In addition, unlike the pipelined schedules, the communication cost is independent of the problem size.

The improved scalability of the overlapped and split tiling schemes, due to an absence of the pipeline startup cost, is shown in Figure 2.12. The problem size was fixed at 20000 elements per processor. The number of processors was varied to measure the weak scaling capability of the various schemes. A straight line parallel to the x-axis corresponds to linear scaling. The split tiling solution performs best, followed by the overlapped tiling solution. The pipelined schedules suffer from performance degradation with increase in the number of processors.

Figure 2.9: Optimal space and time tile size for pipelined schedule 1

### 2.8 Related Work

Several recent works have presented manual optimizations and experimental studies on stencil computations [54, 53, 39]. Iteration space tiling [52, 119] is a method of aggregating a number of loop iterations into *tiles* where the tiles execute atomically; communication (or synchronization) with other processors takes place before or after the tile but not during the execution of the iterations of a tile. Several works have used tiling for exploiting data locality [4, 3, 118, 106, 29]. Others have addressed the selection of tile shape and size to minimize overall execution time [34, 92, 9, 95, 49, 14]. The size of tiles has an impact on the amount of parallelism and communication: smaller tiles increase parallelism by reducing pipelined startup cost, while larger tiles reduce frequency of communication among processors. This has been studied by a number of researchers [9, 95, 49, 50, 33, 51]. Griebl

Figure 2.10: Optimal space and time tile size for pipelined schedule 2

[42, 43] presents an integrated framework for optimizing data locality and parallelism in the use of tiling; however, pipelining issues are not considered.

Li and Song [77] present techniques to optimize stencil codes through loop skewing and array padding. Strout [] present techniques for data and computation reordering for sparse matrix computations. The optimizations include time tiling for relaxation codes, with tile shapes similar to that derived by our overlapped tiling approach.

The Omega toolkit [59] provides support to compute the exact transitive dependences of tuple relations when possible, if not resort to computing a lower bound. Kelly et al. [61] present an approach to compute transitive closure of parameterized tuple relations and present its applications, including the determination of transitive dependences. Pugh and Wonnacott [91] present techniques to compute both upper and lower bounds of transitive closures. These techniques can be employed to determine the transitive dependences that

Figure 2.11: One-dimensional Jacobi execution time, varying problem size

we are interested in. Wonaccott [121] discusses time skewing to optimize locality of stencil computations. In the parallel context [120], the work presents an approach similar to split tiling discussed here. It does not consider overlapped tiling, or present a characterization of when it is beneficial.

Sawdey and O'Keefe [99] describe TOPAZ the tool that explores the replicated computation of boundary values in the context of SPMD execution of stencil codes, in which the user marks regions of code to be replicated; the tool then analyzes and generates the correct code. This approach helps with reducing communication costs and improving load balance. Adve et al. [1] describe computation partitioning strategies used in the dHPF compiler that exploit replicated computation using the LOCALIZE directive that is available in dHPF. Both these approaches rely on user-specification of replicated computation, unlike our approach to automatic parallelization.

Figure 2.12: One-dimensional Jacobi execution time, varying #procs

### 2.9 Conclusions

Iteration space tiling has received considerable attention motivated by optimizing for data locality as well as by exploiting parallelism for nested loops. The choice of the shape of iteration space tiles may result in inter-tile dependences that inhibit concurrent execution of tiles on different processors, leading to a pipelined start overhead. This chapter has addressed the issue of enhancing concurrency with tiled execution of loop computations with constant dependences. Two approaches, namely *overlapped tiling* and *split tiling* were presented, that enabled the removal of inter-tile dependences, thereby enabling additional concurrency. These techniques expose the trade-off between the communication and computation costs, and the parallelism in the program. Experimental results demonstrated the effectiveness of the proposed schemes on stencil codes.

### **CHAPTER 3**

# DATA LAYOUT TRANSFORMATION FOR DISK RESIDENT ARRAYS

# 3.1 Introduction

Many scientific and engineering applications need to operate on data sets that are too large to fit in the physical memory of a machine. Such data is stored in disk and brought into physical memory for processing as needed. The data is then said to reside *out-of-core* and the program is referred to as an *out-of-core program*.

The bandwidth available to access data in secondary storage is much smaller than from main memory, and this discrepancy is only exacerbated by current technology trends . This necessitates minimization of disk access while maximizing reuse of data already in memory. In addition, the extremely large seek time relative to the per-word transfer time for disk access dictates that I/O be done using contiguous blocks of disk resident data. These concerns can require careful reexamination of an in-memory algorithm to tailor it to the characteristics of secondary storage.

An approach to solving this problem exploits the operating system's virtual memory. The user addresses data in an address space often larger than the physical memory of the machine. The operating system implicitly moves the data from secondary storage to physical memory when it is accessed by the user and replaces other unused data to free up physical memory as needed. Any modified data is written back to disk before being replaced. Since the data movement is done in units of an operating system page, improved disk I/O bandwidth is achieved. While providing a simple abstraction, this approach suffers from several drawbacks. First, the generic page replacement policies in kernels do not exploit the specialized data access patterns exhibited by scientific applications [17]. Second, the virtual memory supported by 32-bit operating systems is still too small compared to the disk space available even in a single hard disk drive. Third, efficient extensions of virtual memory for parallel systems are not available.

An alternative approach commonly employed acknowledges secondary storage as another level of the addressable memory hierarchy and explicitly moves data between main memory and secondary storage. Higher-level abstractions are provided to enable simplified yet efficient data movement where possible.

We focus on disk I/O support to enable simplified yet efficient abstractions to access multi-dimensional arrays stored on disk. I/O libraries like PANDA [102, 109] and DRA [38] use a blocked representation for the disk-based multidimensional arrays to optimize performance of collective I/O operations between arrays located on disk and in the distributed main memory of parallel computers [22].

Thus a disk-based multidimensional array is partitioned into a number of multidimensional blocks or "bricks" and the elements within a brick are linearized using some dimension order. Unlike the dimension-ordered representation typically employed to represent in-memory multidimensional arrays, the bricked representation permits efficient contiguous access as long as the accessed regions mostly contain full bricks.

However, in some programs, the access patterns to some disk-based multidimensional arrays in two successive phases (or the access pattern of the producer and the consumer) are so different that no choice of brick shape will allow for efficient access in both the phases. An example is the out-of-core two-dimensional Fast Fourier Transform (FFT), where the array is accessed by columns in one phase and by rows in the other. The multi-dimensional FFT [8, 10] can be implemented as a series of one-dimensional FFTs, one along each dimension. As another example, consider image data in three and four (including time) dimensions. The production of data from scanning occurs plane by plane. However, examination of the time evolution of a three-dimensional block of data requires a very different access pattern than that by which the data was generated. In isosurface construction in three and four dimensions, the data is typically produced in a row-major format by scanning or simulation. The amount of memory available determines the amount of data generated between writes to disk, and hence limits the blocking possible [58]. In such scenarios the performance of computations operating on the stored data might be greatly improved by transforming the data into a different blocked form to match the application's access pattern.

In this chapter, we present efficient data layout transformation algorithms to transform the blocking of multi-dimensional arrays. We first develop an out-of-core matrix transposition algorithm that takes into account the I/O characteristics of the target system. We then present a novel algorithm to solve the out-of-core matrix reblocking problem for multidimensional matrices of arbitrary sizes.

| System   | Configuration              |             |        |            |  |  |  |  |  |  |  |

|----------|----------------------------|-------------|--------|------------|--|--|--|--|--|--|--|

|          | Processor                  | Memory (MB) | Linux  | Compiler   |  |  |  |  |  |  |  |

| ia64-osc | Dual Itanium-2 (900 MHz)   | 4096        | 2.4.18 | gcc 2.96   |  |  |  |  |  |  |  |

| amd-osc  | Dual Athlon MP (1.533 GHz) | 2048        | 2.4.20 | pgcc 4.0-2 |  |  |  |  |  |  |  |

Table 3.1: Configuration of systems used for I/O characterization

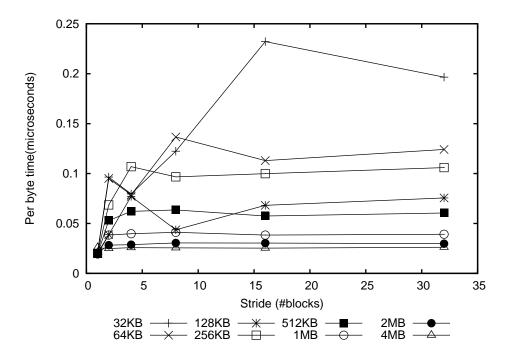

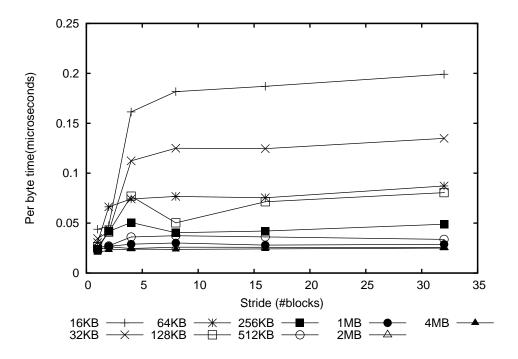

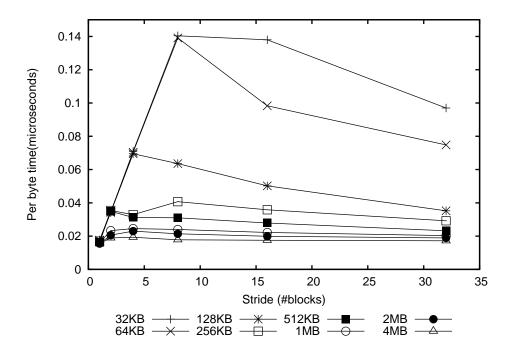

## **3.2** Disk I/O Characterization

Out-of-core algorithms on multi-dimensional arrays, such as out-of-core matrix transposition, involve reading and writing blocks of data at different strides. To understand the variation in performance of the algorithm with respect to these parameters, we studied the variation of read and write times with changes in size and stride of I/O on two clusters at the Ohio Supercomputer Center (OSC) [87]. The configuration of each compute node in these clusters is shown in Table 3.1. Figure 3.1 and Figure 3.2 show the strided read and write times respectively on amd-osc. Figure 3.3 and Figure 3.4 show the strided read and write times respectively on ia64-osc.