## Analysis & Design of Radio Frequency Wireless Communication Integrated Circuits with Nanoscale Double Gate MOSFETs

A dissertation presented to the faculty of the Russ College of Engineering and Technology of Ohio University

> In partial fulfillment of the requirements for the degree Doctor of Philosophy

> > Soumyasanta Laha

May 2015

© 2015 Soumyasanta Laha. All Rights Reserved.

This dissertation titled

Analysis & Design of Radio Frequency Wireless Communication Integrated Circuits with Nanoscale Double Gate MOSFETs

by

### SOUMYASANTA LAHA

has been approved for the School of Electrical Engineering and Computer Science and the Russ College of Engineering and Technology by

Savas Kaya

Professor of Electrical Engineering and Computer Science

Denis Irwin

Dean, Russ College of Engineering and Technology

### ABSTRACT

#### LAHA, SOUMYASANTA, Ph.D., May 2015, Electrical Engineering

Analysis & Design of Radio Frequency Wireless Communication Integrated Circuits with Nanoscale Double Gate MOSFETs (214 pp.)

Director of Dissertation: Savas Kaya

Today's nanochips contain billions of transistors on a single die that integrates whole electronic systems as opposed to sub-system parts. Together with ever higher frequency performances resulting from transistor scaling and material improvements, it thus become possible to include on the same silicon chip analog functionalities and wireless communication circuitry that was once reserved to only an elite class of compound III-V semiconductors. It appears that the last stretch of Moore's scaling down to 5 nm range, these systems will only become more capable and faster, due to novel types of transistor geometries and functionalities as well as better integration of passive elements, antennas and novel isolation approaches. Accordingly, this dissertation is an example to how RF-CMOS integration may benefit from the use of a novel multi-gate transistors called FinFETs or Double Gate Metal Oxide Semiconductor Field Effect Transistors (DG-MOSFETs). More specifically, this research is to validate how the performance of the radio frequency wireless communication integrated circuits can be improved by the use of this novel transistor architecture.

To this end, in this dissertation, a wide range of radio frequency integrated circuits have been investigated in DG-MOSFETs which include Oscillators, On Off Keying (OOK) Modulator, Power Amplifier, Low Noise Amplifier, Envelope Detector, RF Mixer and Charge Pump Phase Frequency Detector. In all cases, the use of DG-MOSFET devices lead to reduction of transistor count and circuit complexity, while also resulting in tunable circuits owing to local back-gate control available in this device structure. Hence this work provides a unique insight as to how modest geometry changes and 3D device engineering may result in significant gains in analog/RF circuit engineering in the last stretch of Moores scaling.

To the memory of my father, Bhanu Kumar Laha and grandfather, Sudhanshu Sekhar Laha

#### **ACKNOWLEDGMENTS**

I wish to express my sincere gratitude to my advisor, Prof. Savas Kaya for his valuable guidance and supervision in the development of the dissertation. He has been always friendly yet rigorous with my research progress which helped me in the achievement of the research goal. His tremendous energy and enthusiasm towards any academic venture is truly commendable and has taught me many lessons for my future endeavor. Also grateful to him for providing the necessary financial support as research assistantship during the course of my research.

I am extremely grateful to my committee members, Prof. Chris Bartone, Prof Jeffrey Dill and Prof. Avinash Kodi for their valuable academic guidance in the final progress of the dissertation. Their familiarity with the ideas, needs of the subject and effective suggestions are a contributing factor to the development of the dissertation.

I also extend my warm gratitude to my external committee members Prof. Sergio Ulloa of Department of Physics and Astronomy and Prof. Martin Mohlenkamp of Department of Mathematics for their inquisitiveness and appraisal towards my work in the last laps of the dissertation.

Special thanks to Prof. Jerrel Mitchel, currently a retired professor, for considering me for the 21 month endowed 'Stocker Research Fellowship' during the admission in his capacity as the Graduate Chair of the department, that stands out to be an important reason to choose the university for my PhD study.

My heartfelt thanks also goes to Prof. David Matolak, for providing me the Teaching Assistantship for two academic years in his capacity as the Graduate Chair of our department. Later, as a collaborator cum mentor of an NSF sponsored research project, his suggestions in weekly meetings have helped me to gain a clear and total understanding of the project. My sincere gratitude goes to the university program of Synopsys and Cadence Design Systems, which helped in carrying out the EDA simulations necessary for the research. My special gratitude goes to Keysight Technologies (Agilent) for providing complementary access to their ADS software. I am also thankful to MOSIS for providing access to 65 nm and 130 nm RF CMOS process technologies from IBM and to Win Semiconductor for access to their III-V pHEMT technology process.

I also remember the wonderful moments that I have spent with all my colleagues during the course of the dissertation.

Finally, I am indebted to my parents, my wife and my brother for their continuous support and motivation towards the progress of this dissertation.

# TABLE OF CONTENTS

| Abstract                              | 3  |  |  |

|---------------------------------------|----|--|--|

| Dedication                            |    |  |  |

| Acknowledgments                       | 6  |  |  |

|                                       |    |  |  |

| List of Tables                        | 12 |  |  |

| List of Figures                       | 13 |  |  |

| 1 Introduction & Motivation           | 19 |  |  |

|                                       | -  |  |  |

| 1.1 Wireless Communication            | 19 |  |  |

| 1.2 Integrated Circuits               | 21 |  |  |

| 1.3 Novel Multi-Gate & 3D Transistors | 22 |  |  |

| 1.4 Research Goals & Accomplishments  | 24 |  |  |

| 1.4.1 Research Goals                  | 24 |  |  |

| 1.4.2 Accomplishments                 | 25 |  |  |

| 1.5 Dissertation Organization         | 28 |  |  |

| 1.6 Analysis & Design Tools           | 29 |  |  |

|                                       |    |  |  |

| 2 Background                          | 32 |  |  |

| 2.1 MOSFET Fundamentals               | 32 |  |  |

| 2.1.1 MOSFET Operation                | 32 |  |  |

| 2.1.2 I-V Characteristics             | 34 |  |  |

| 2.1.3 Complementary MOS Architecture  | 35 |  |  |

| 2.1.4 Power Dissipation               | 36 |  |  |

| 2.1.5 MOSFET Scaling                  | 37 |  |  |

| 2.2 Evolution to Multigate MOSFETs    | 38 |  |  |

| 2.2.1 Limitations of CMOS             | 38 |  |  |

| 2.2.2         Advanced CMOS           | 40 |  |  |

| 2.2.2.1 Strained Silicon              | 41 |  |  |

| 2.2.2.2 SOI Technology                | 42 |  |  |

|                                       | 42 |  |  |

| 2.2.2.3 Multigate MOSFETs             |    |  |  |

| 2.3 DG-MOSFET Basics                  | 44 |  |  |

| 2.3.1 Device Models                   | 47 |  |  |

| 2.3.2 Small Signal Circuit Models     | 49 |  |  |

| 2.4 Microwave Basics                  | 51 |  |  |

| 2.4.1 RF Figure of Merits             | 51 |  |  |

| 2.4.2 Non-Linearity                   | 52 |  |  |

Page

|     |                | 2.4.2.1 Harmonic Distortion                                                                                                   |

|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------|

|     |                | 2.4.2.2 Gain Compression                                                                                                      |

|     |                | 2.4.2.3 Intermodulation                                                                                                       |

|     | 2.4.3          | Noise                                                                                                                         |

|     |                | 2.4.3.1 Randomness and Noise Spectrum                                                                                         |

|     |                | 2.4.3.2 Device Noise                                                                                                          |

|     |                | 2.4.3.3 Noise in Circuits                                                                                                     |

|     | 2.4.4          | Sensitivity & Dynamic Range                                                                                                   |

|     |                | 2.4.4.1 Sensitivity                                                                                                           |

|     |                | 2.4.4.2 Dynamic Range                                                                                                         |

|     | 2.4.5          | Scattering Parameters                                                                                                         |

|     | 2.4.6          | Passives                                                                                                                      |

|     | 2.4.0          | 2.4.6.1 Resistors                                                                                                             |

|     |                | 2.4.6.2 Capacitors                                                                                                            |

|     |                | 2.4.6.3 Inductors                                                                                                             |

|     |                | 2.4.6.4       Microstrip Transmission Lines       70                                                                          |

|     | 2.4.7          | Impedance Matching                                                                                                            |

| 2.5 |                | ss Communication                                                                                                              |

| 2.3 | 2.5.1          |                                                                                                                               |

|     | 2.3.1          |                                                                                                                               |

|     |                | 2.5.1.1Amplitude Shift Keying762.5.1.2Phase Shift Keying77                                                                    |

|     |                | 5 8                                                                                                                           |

| 20  | <b>XX</b> 7° 1 | 2.5.1.3 Orthogonal Frequency Division Multiplexing                                                                            |

| 2.6 |                | ss Transceiver                                                                                                                |

|     | 2.6.1          | Basic Architecture                                                                                                            |

|     | 2.6.2          | System Level Design                                                                                                           |

|     | 2.6.3          | Link Budget Analysis                                                                                                          |

| DG  | MOSEE          | T OOK Transmitter                                                                                                             |

| 3.1 |                | action                                                                                                                        |

| 3.1 |                | ttors                                                                                                                         |

| 5.2 | 3.2.1          |                                                                                                                               |

|     | 3.2.1          |                                                                                                                               |

|     | 3.2.2          | LC Oscillator                                                                                                                 |

| 2.2 |                | Relaxation Oscillator    102                                                                                                  |

| 3.3 |                | $Modulator \dots \dots$ |

| 3.4 |                | Amplifier                                                                                                                     |

|     | 3.4.1          | Power Amplifier Basics                                                                                                        |

|     | 3.4.2          | Power Amplifier Design                                                                                                        |

| ~ ~ | 3.4.3          | Simulation Results                                                                                                            |

| 3.5 | Summa          | ary                                                                                                                           |

| 4  | DG-    | MOSFET OOK Receiver                                     | 120  |

|----|--------|---------------------------------------------------------|------|

|    | 4.1    | Introduction                                            | 120  |

|    | 4.2    | Low Noise Amplifier                                     | 120  |

|    |        | 4.2.1 Low Noise Amplifier Basics                        | 121  |

|    |        | 4.2.2 Quantitative Analysis: CS Source Degeneration LNA | 123  |

|    |        | 4.2.3 LNA Design                                        |      |

|    |        | 4.2.4 LNA Gain Switching                                |      |

|    |        | 4.2.5 Simulation Results                                |      |

|    | 4.3    | Envelope Detector                                       | 138  |

|    | 4.4    | Summary                                                 |      |

| ~  | DC     |                                                         | 1.40 |

| 5  |        | MOSFET Circuits for Coherent Detection                  |      |

|    | 5.1    | Introduction                                            |      |

|    | 5.2    | DG-MOSFET RF Mixer                                      |      |

|    |        | 5.2.1 RF Mixer Theory                                   |      |

|    |        | 5.2.2 RF Mixer Operation                                |      |

|    |        | 5.2.3 Operating Point Analysis                          |      |

|    |        | 5.2.4 Structural Parameters                             |      |

|    |        | 5.2.5 Noise & Linearity Performance                     |      |

|    | 5.3    | DG-MOSFET Phase Frequency Detector                      | 158  |

|    |        | 5.3.1 DG-MOSFET NOR Gate                                | 159  |

|    |        | 5.3.2 Charge Pump PFD                                   | 161  |

|    | 5.4    | Summary                                                 | 166  |

| 6  | REI    | C in Commercial CMOS Technology                         | 160  |

| 0  | 6.1    |                                                         |      |

|    | 6.2    | Transceiver in 65 nm RF CMOS                            |      |

|    | 0.2    | 6.2.1 Transmitter Design                                |      |

|    |        | 6.2.1.1 VCO                                             |      |

|    |        |                                                         |      |

|    |        |                                                         |      |

|    |        |                                                         |      |

|    |        | 6.2.2.1 LNA                                             |      |

|    | ( )    | 6.2.2.2 Envelope Detector                               |      |

|    | 6.3    | Summary                                                 | 1/8  |

| 7  | Con    | clusion & Future Work                                   | 179  |

|    | 7.1    | Conclusions                                             | 179  |

|    | 7.2    | Future Work                                             | 182  |

| Δг | nend   | ix A: Some Wireless Standards                           | 102  |

| Аŀ | penu   |                                                         | 170  |

| Ap | opendi | ix B: Phase Noise Fundamentals & Models                 | 202  |

|                      | 1 1          | • •           |                     | 011       |

|----------------------|--------------|---------------|---------------------|-----------|

| Appendix C: Refereed | publications | s arising out | of the Dissertation | <br>. 211 |

# LIST OF TABLES

| Table             | e                                                                                      | Page  |

|-------------------|----------------------------------------------------------------------------------------|-------|

| 1.1<br>1.2        | Analysis & Design Tools for DG-MOSFET                                                  |       |

| 2.1               | Active Blocks Individual FoMs                                                          | . 86  |

| 3.1               | Performance comparison of different wide band PAs [1]                                  | . 118 |

| 4.1<br>4.2<br>4.3 | 60 GHz LNA Performance Trade-Offs for different $V_{bg}$ s                             | . 136 |

| 5.1               | Optimum $V_{LO}$ for the different structural parameters at $f_{RF} = 2.4 \text{ GHz}$ | . 154 |

# LIST OF FIGURES

| Figu       | re                                                                                    | Page |

|------------|---------------------------------------------------------------------------------------|------|

| 1.1        | Illustration of application of wireless communication in different areas [3], [4] [5] | . 20 |

| 1.2        | [4],[5]                                                                               |      |

|            | y axis, left) [6]                                                                     | . 22 |

| 2.1<br>2.2 | nMOSFET device structure and electrical contacts [7]                                  |      |

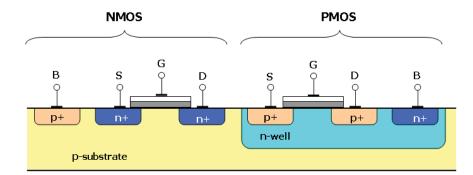

| 2.2        | The basic CMOS device architecture [8]                                                |      |

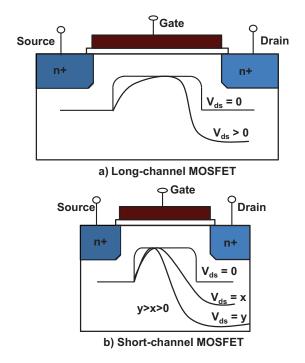

| 2.4        | Band Bending in Long channel & Short channel MOSFETS                                  |      |

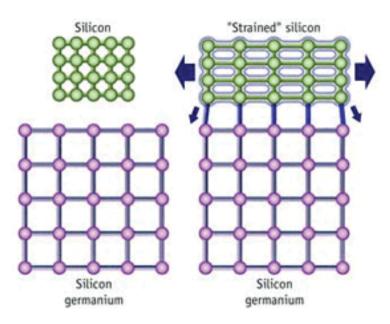

| 2.5        | Biaxial straining of Si by SiGe [9].                                                  |      |

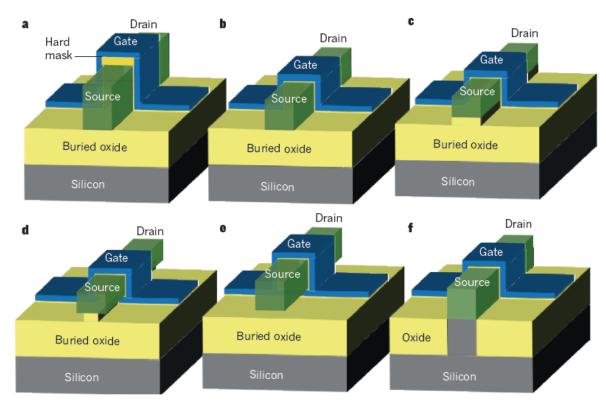

| 2.6        | Types of multigate MOSFET. The various ways in which the gate electrode               |      |

|            | can be wrapped around the channel region of a transistor are shown. a) A              |      |

|            | silicon-on-insulator (SOI) fin field-effect transistor (FinFET). b) SOI Tri-gate      |      |

|            | MOSFET. Channel control is applied from three sides of the device c) SOI $\pi$ -      |      |

|            | gate MOSFET. Channel control is improved over the tri-gate MOSFET shown               |      |

|            | in b since the electric field from the lateral sides of the gate exerts some control  |      |

|            | on the bottom side of the channel. d) SOI $\Omega$ -gate MOSFET. The gate control of  |      |

|            | the bottom of the channel region is better than in the SOI $\pi$ -gate MOSFET. e)     |      |

|            | SOI gate-all-around MOSFET. Channel control is applied from all four sides            |      |

|            | of the device. f) A bulk tri-gate MOSFET. Channel control is applied from             |      |

|            | three sides of the device. In this case, there is no buried oxide underneath the      | . 43 |

| 2.7        | device [6]                                                                            |      |

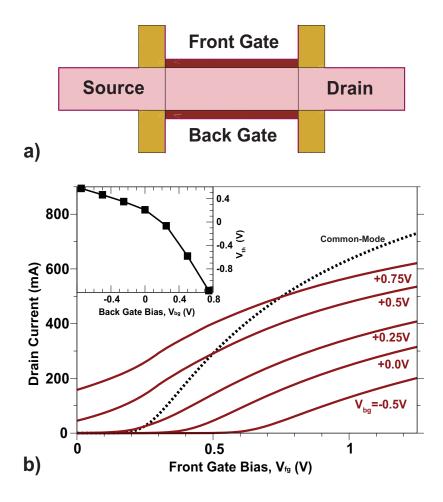

| 2.7        | a) The generic DG-MOSFET device structure. b) $I_D$ - $V_{fg}$ characteristics of an  | . 44 |

| 2.0        | n-type Independent and Common Mode DG ( $V_{bg} = V_{fg}$ ) transistors. The inset    |      |

|            | shows the resulting shift in the front gate threshold                                 | . 45 |

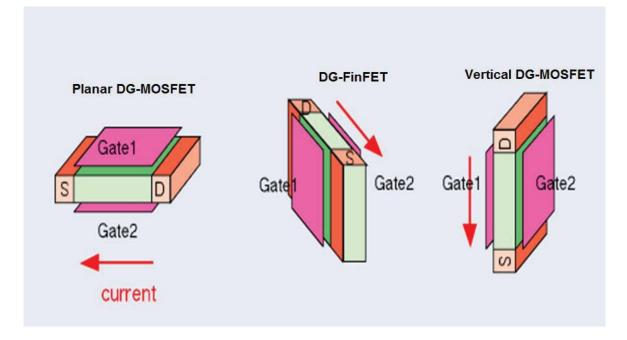

| 2.9        | The three different varieties of DG-MOSFET. The difference lies in the                | . тЈ |

| 2.7        | direction of flow of electric current in the channel of the transistor [11]           | . 47 |

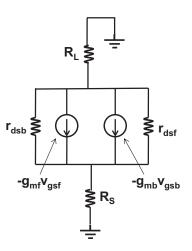

| 2.10       | Simple Small Signal Circuit Model for DG-MOSFET.                                      |      |

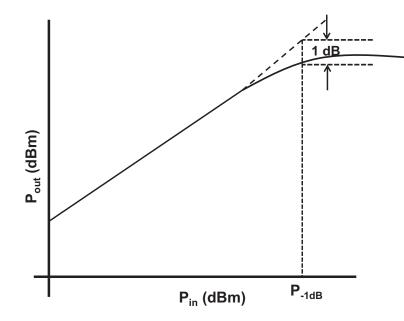

|            | 1-dB Compression point.                                                               |      |

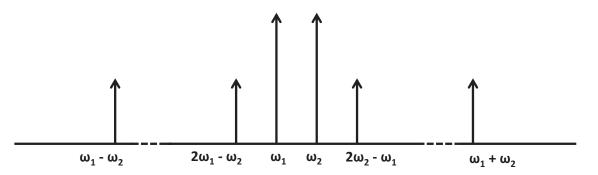

|            | Intermodulation Components in two tone test.                                          |      |

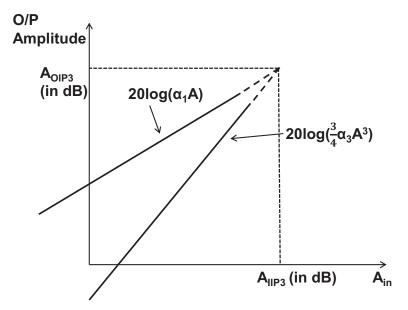

|            | Third Order Intercept Point (in terms of voltage).                                    |      |

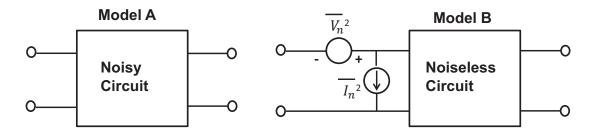

|            | Input-referred noise.                                                                 |      |

| 2.15       | Illustration of Incident & Reflected waves at the input and output.                   | . 63 |

| 2.16 | Resistor equivalent circuit.                                                       | 64  |

|------|------------------------------------------------------------------------------------|-----|

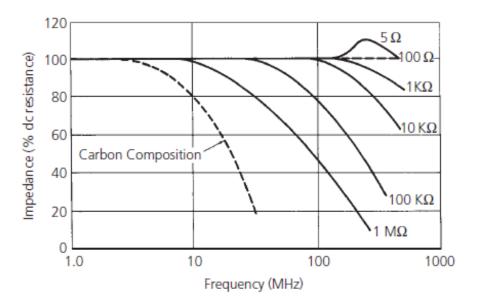

|      | Frequency characteristics of metal-film and carbon-composition resistors [12].     | 65  |

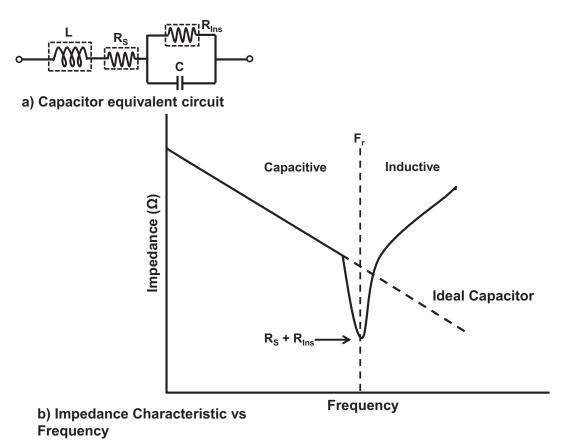

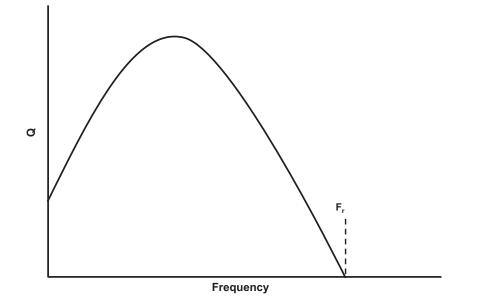

|      | a) Capacitor equivalent circuit. b) Impedance characteristic vs. frequency         | 66  |

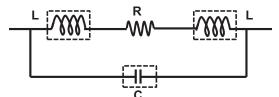

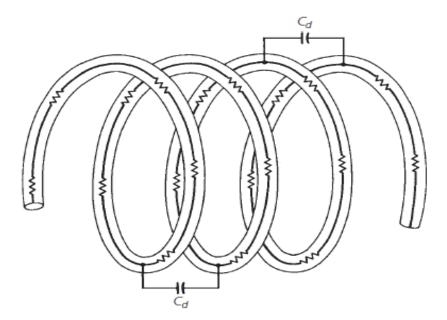

|      | Distributed capacitance and series resistance in an inductor [12].                 | 67  |

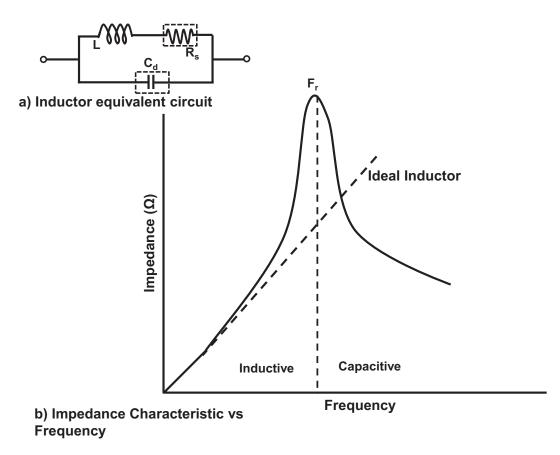

|      | a) Inductor equivalent circuit. b) Impedance characteristic vs. frequency for a    |     |

|      | practical and an ideal inductor.                                                   | 68  |

| 2.21 | Q versus frequency of an inductor.                                                 | 69  |

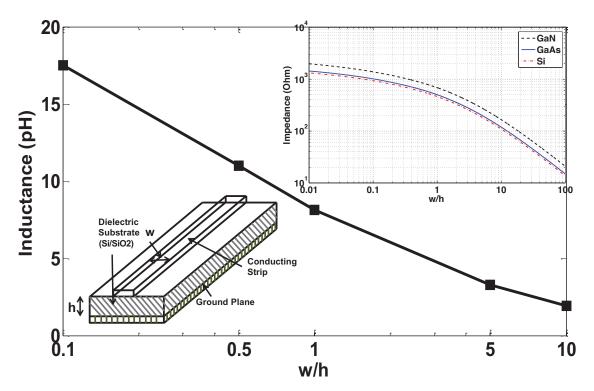

|      | The inductance versus microstrip aspect ratio (w/h) at $1 = 50 \ \mu$ m. The inset |     |

|      | plot shows the resulting characteristic impedance of the microstrips TL on         | - 1 |

| 0.00 | alternative substrates.                                                            | 71  |

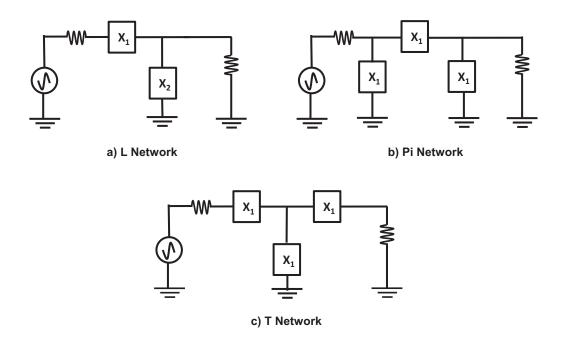

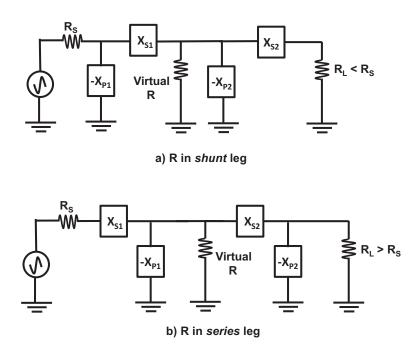

|      | Impedance Matching of L-network, Pi-Network & T-network.                           | 74  |

|      | Two series-connected L networks for lower Q applications                           | 75  |

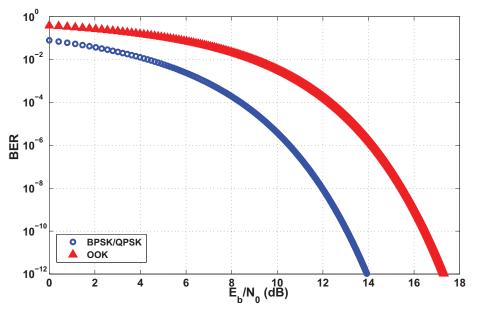

|      | Bit Energy to Noise Density ratio $(E_b/N_o)$ for different modulation schemes     | 77  |

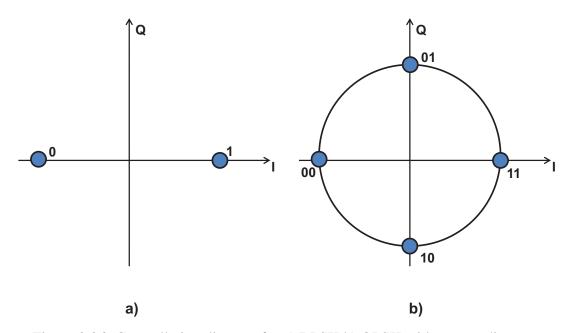

|      | Constellation diagram for a) BPSK b) QPSK with gray coding                         | 78  |

| 2.27 | a) Single carrier modulation with high-rate input. b) OFDM with multiple           | ~ ~ |

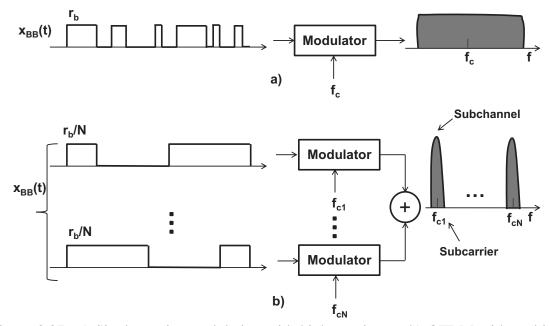

| • •  | carriers.                                                                          | 80  |

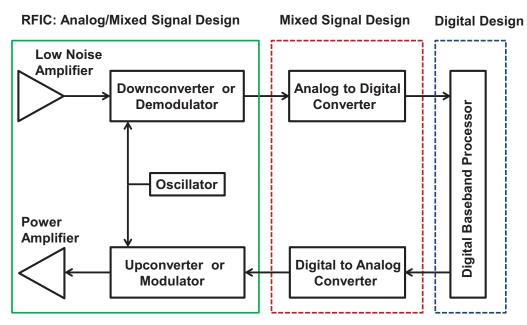

|      | The generic wireless transceiver architecture.                                     | 81  |

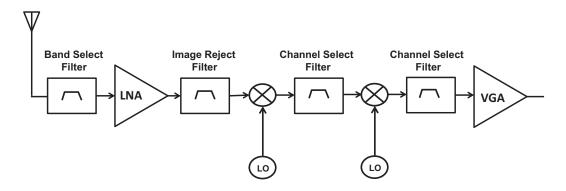

|      | The receiver schematic.                                                            | 83  |

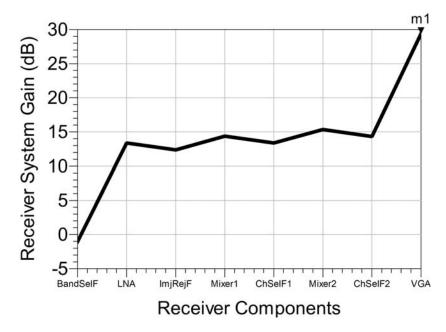

| 2.30 | The simulated gain of the receiver chain. The marker 'm1' indicates the final      | ~ ~ |

| 0.01 | gain achieved in the receiver system.                                              | 85  |

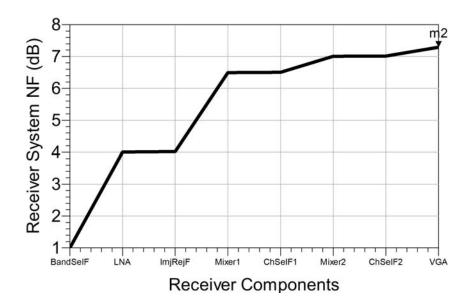

| 2.31 | The simulated NF of the receiver chain. The marker 'm2' indicates the final        | 0.7 |

| 0.00 | NF achieved in the receiver system.                                                | 85  |

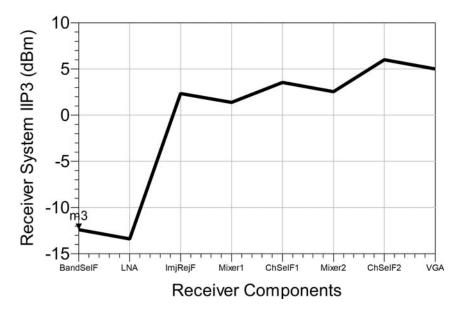

| 2.32 | The simulated $IIP_3$ of the receiver chain. The marker 'm3' indicates the final   | 0.0 |

| 0.00 | $IIP_3$ in the receiver system                                                     | 86  |

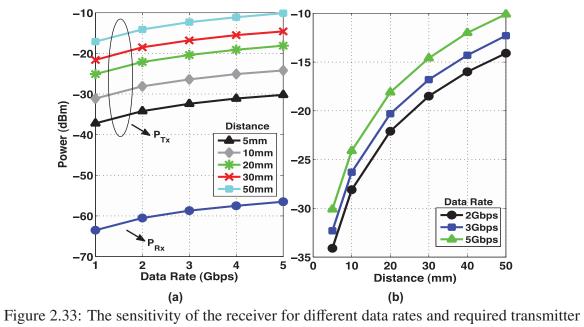

| 2.33 | The sensitivity of the receiver for different data rates and required transmitter  | 0.0 |

|      | power levels for different propagation distance as well as data rates              | 88  |

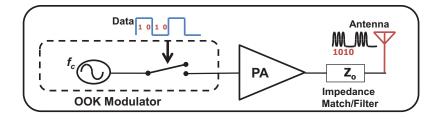

| 3.1  | The OOK Transmitter Block Diagram.                                                 | 90  |

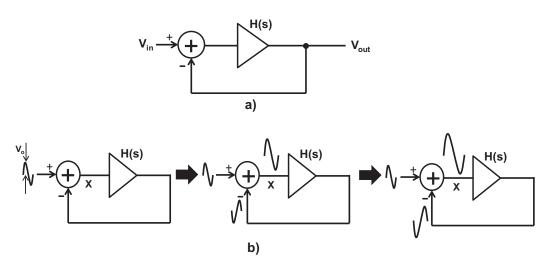

| 3.2  | a) Feedback System b) Evolution of oscillatory system with time. $\ldots$ .        | 90  |

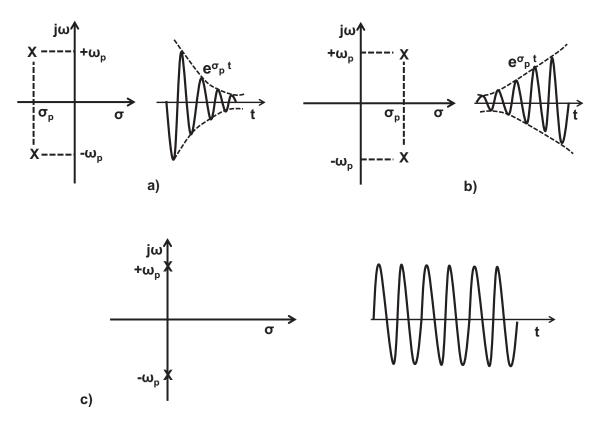

| 3.3  | Time domain response of a system versus the position of poles: a) Stable with      |     |

|      | decaying amplitude of oscillation/not oscillating b) Unstable with increasing      |     |

|      | amplitude of oscillation. c) Unstable with constant amplitude of oscillation       |     |

|      | (Desired)                                                                          | 93  |

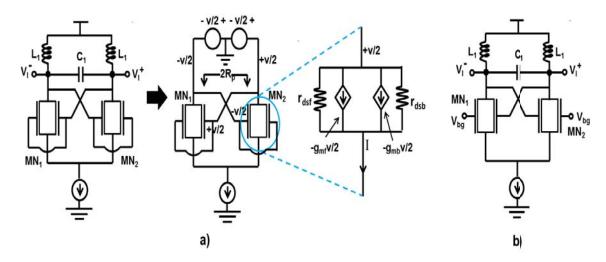

| 3.4  | a) The negative resistance LC oscillator in common mode DG-MOSFET. At              |     |

|      | resonance, the LC tank becomes resistive only and the latch circuit acts as        |     |

|      | negative resistance to nullify its effect. The small signal analysis of a DG-      |     |

|      | MOSFET is focussed to study the criterion for oscillation. b) The independent      |     |

|      | mode tunable DG-MOSFET LC oscillator [13]                                          | 94  |

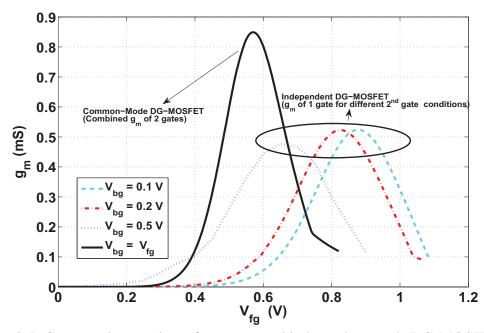

| 3.5  | Comparative $g_m$ plots of common and independent mode DG-MOSFETs [13].            | 96  |

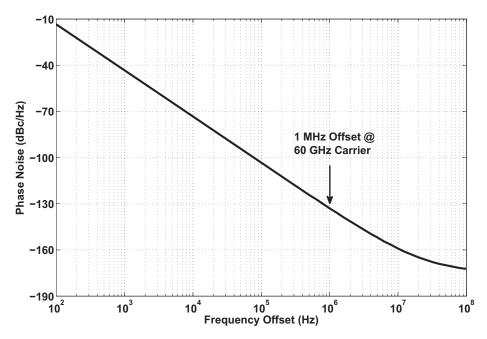

| 3.6  | The phase noise of the LC oscillator at 60 GHz. The phase noise at 1 MHz           |     |

|      | offset is observed at -133 dBc/Hz in the linear time variant model [13]            | 97  |

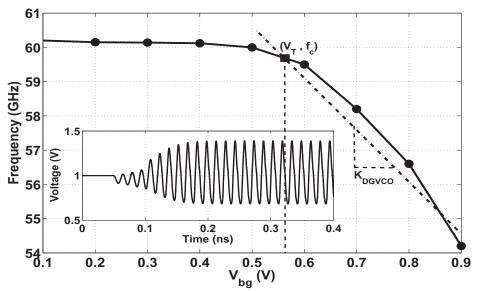

| 3.7   | The frequency tuning with back gate bias for the independent mode LC                                         |

|-------|--------------------------------------------------------------------------------------------------------------|

|       | Oscillator. Inset: The output waveform of the DG-MOSFET LC oscillator                                        |

|       | at 60 GHz [13]                                                                                               |

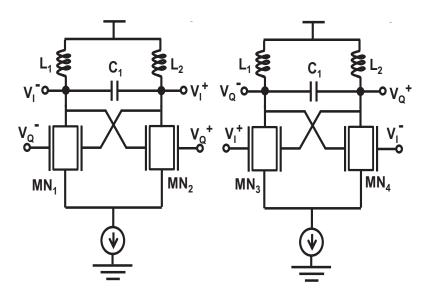

| 3.8   | The LC quadrature oscillator implemented with only four DG-MOSFETs in                                        |

|       | independent DG mode configuration [13]                                                                       |

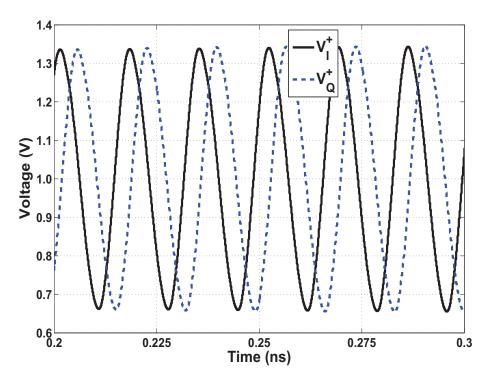

| 3.9   | The voltage swing of the DG-MOSFET LC quadrature oscillator. The waves                                       |

|       | are generated at 90° phase difference at a frequency of 60 GHz [13] 100                                      |

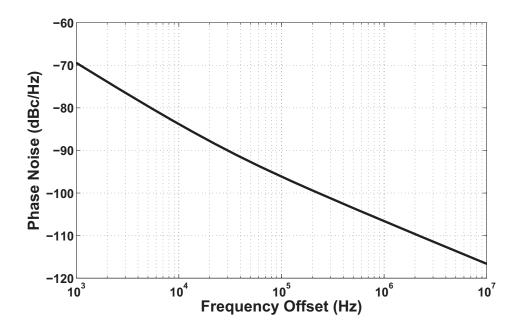

| 3.10  | The phase noise of the quadrature LC oscillator at 60 GHz. The phase noise at                                |

|       | 1 MHz offset is observed at -107 dBc/Hz in the linear time variant model [13]. 101                           |

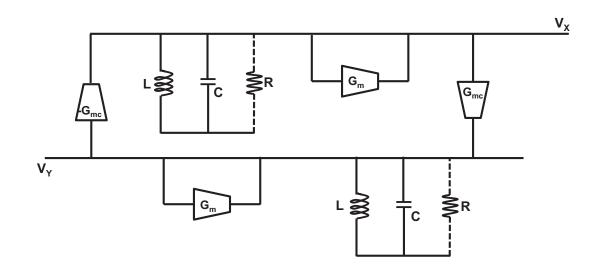

| 3.11  | Linear model for the negative resistance Quadrature Voltage Control Oscillator                               |

| 0.11  | [13]                                                                                                         |

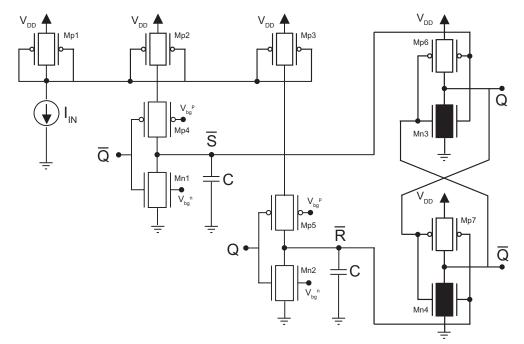

| 3 1 2 | The dual-input S/R latch relaxation oscillator circuit built using DG-MOSFETs                                |

| 5.12  | [14], [15]                                                                                                   |

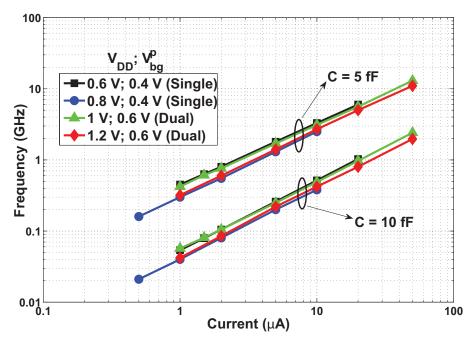

| 3 1 3 | The 'crude frequency tuning' of the oscillator, varying $I_{in}$ for two different                           |

| 5.15  | capacitances [14]. $\ldots$ |

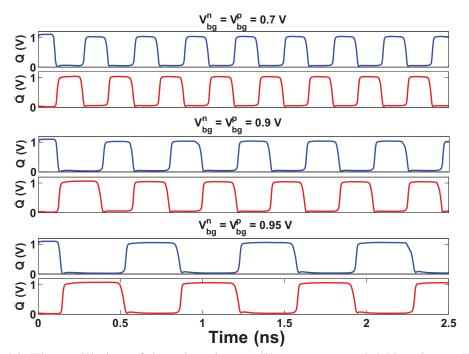

| 2 1 / | The oscillation of the relaxation oscillator at $V_{DD} = 1.1$ V and $I_{in} = 70 \ \mu$ A                   |

| 5.14  |                                                                                                              |

|       | for three back gate biases. The tuning characteristics is evident from altering                              |

| 2 15  | frequency with back gate bias                                                                                |

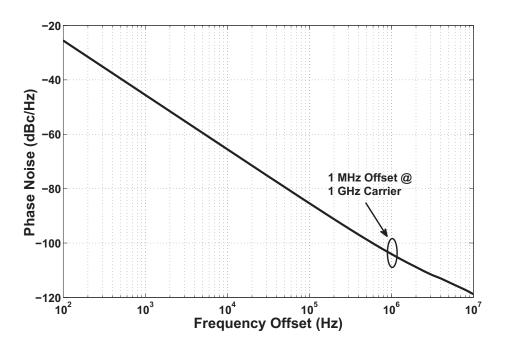

| 3.13  | The phase noise of the oscillator at 1 GHz. The 1 MHz offset is observed at                                  |

| 2.16  | -104  dBc/Hz                                                                                                 |

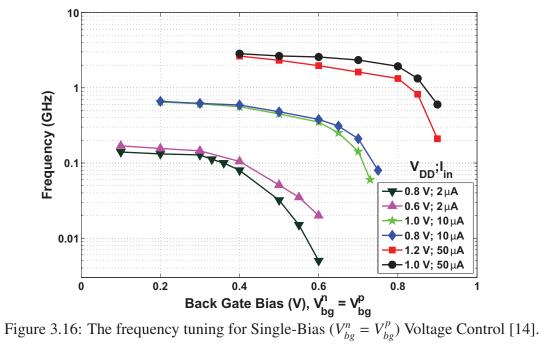

|       | The frequency tuning for Single-Bias $(V_{bg}^n = V_{bg}^p)$ Voltage Control [14] 107                        |

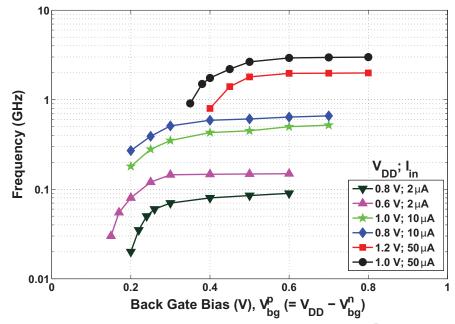

| 3.17  | The frequency tuning for Dual-Bias $(V_{bg}^n = V_{DD} - V_{bg}^p)$ Voltage Control [14] 107                 |

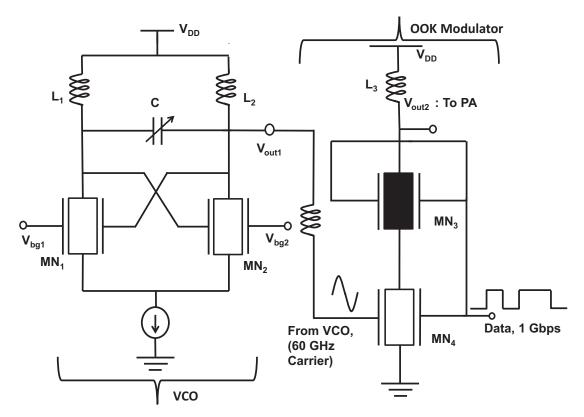

| 3.18  | The OOK Modulator circuit with the VČO. The DG-MOSFET OOK Modula-                                            |

|       | tor uses only two DG-MOSFET for modulation and switching [14], [16] 108                                      |

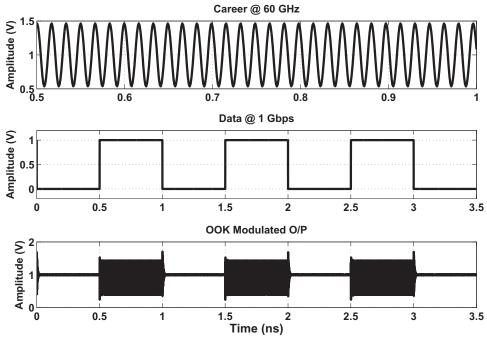

| 3.19  | The OOK modulated output for a carrier frequency of 60 GHz and data rate of                                  |

|       | 1 Gbps. The input data sequence resembles 50% duty cycle [14], [16] 109                                      |

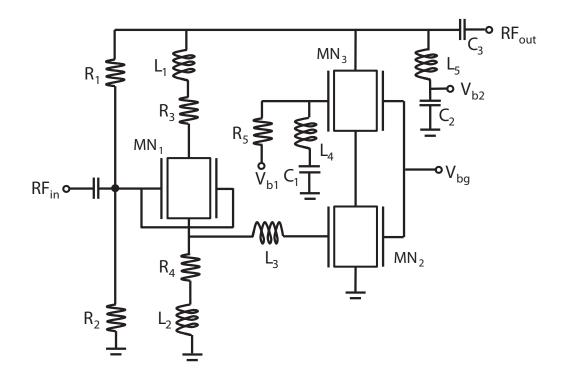

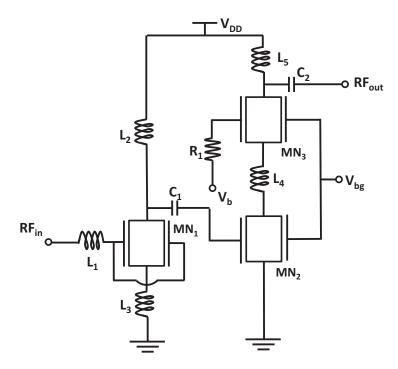

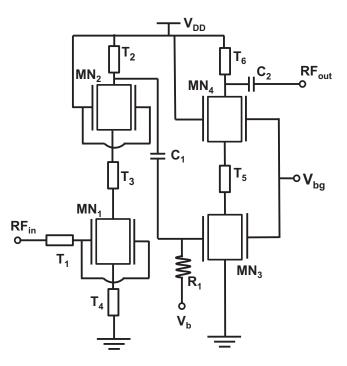

| 3.20  | The DG MOSFET based power amplifier circuit in modified darlington                                           |

|       | cascode configuration. Transistors $MN_1$ operates in the symmetric mode while                               |

|       | $MN_2$ and $MN_3$ operate in independent mode with the back gates used for                                   |

|       | dynamic tuning [14], [1]                                                                                     |

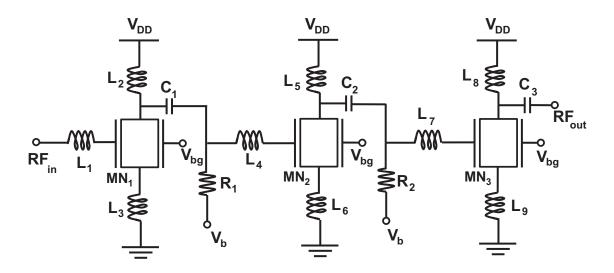

| 3.21  | The three stage DG MOSFET based power amplifier circuit. All the three                                       |

|       | transistors operate in the independent mode [14], [1]                                                        |

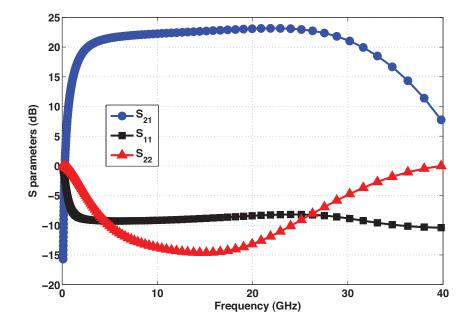

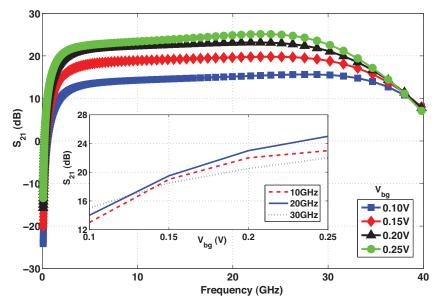

| 3.22  | The S parameters which provide the gain $(S_{21})$ and reflection losses $(S_{11} \&$                        |

|       | $S_{22}$ ) of the power amplifier. This is measured for $V_{bg} = 0.2$ V [14], [1] 113                       |

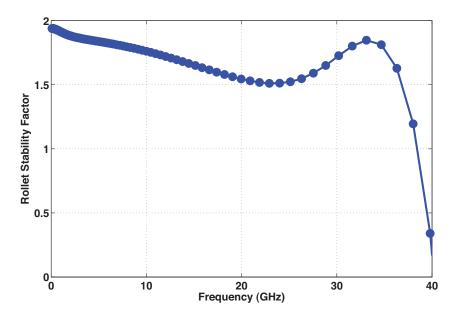

| 3.23  | The rollet stability factor (K) is above unity in the operating range of 2 - 32                              |

|       | GHz verifying the amplifier to remain unconditionally stable in this range. K                                |

|       | drops below unity beyond ~ 38 GHz [14], [1]                                                                  |

| 3.24  | The back gate dependence of the gain is clearly evident. The gain changes by                                 |

|       | ~ 10 dB in the tuning range of $V_{bg}$ . Inset: Gain variation with $V_{bg}$ at different                   |

|       | frequencies [14], [1]                                                                                        |

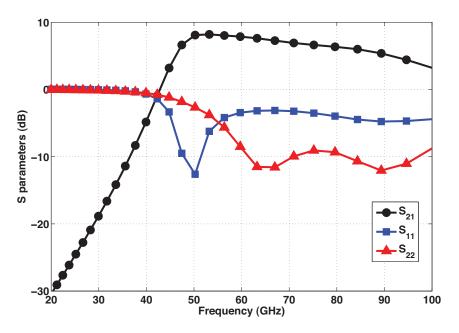

| 3.25  | The S parameters which provide the gain $(S_{21})$ and reflection losses $(S_{11} \&$                        |

|       | $S_{22}$ ) of the power amplifier. This is also measured for $V_{bg} = 0.2$ V [14], [1] 116                  |

|       |                                                                                                              |

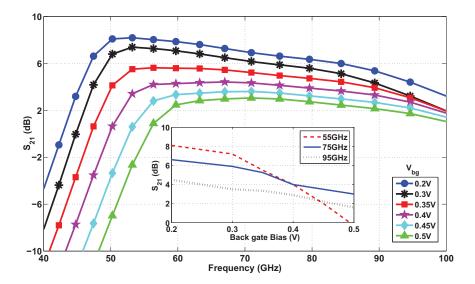

| 3.26 | The back gate dependence of the gain is clearly evident. The gain changes by $\sim 6 \text{ dB}$ in the tuning range of $V_{bg}$ . Inset: Gain variation with $V_{bg}$ at different |      |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|      | frequencies [1], [14]                                                                                                                                                               | 116  |

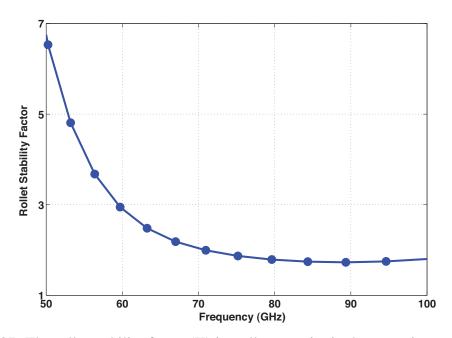

| 3.27 | The rollet stability factor (K) is well over unity in the operating range of 60 -                                                                                                   |      |

|      | 90 GHz verifying the amplifier to remain unconditionally stable in the range                                                                                                        |      |

|      | [1], [14]                                                                                                                                                                           | 117  |

| 4.1  | OOK Receiver block diagram.                                                                                                                                                         |      |

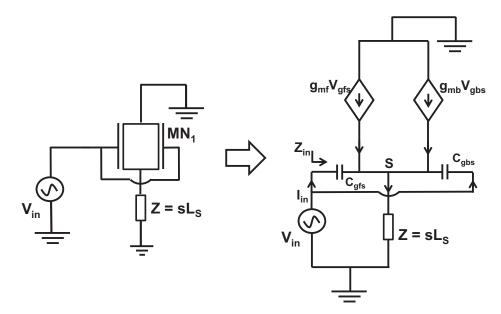

| 4.2  | Small Signal Equivalent of the DG-MOSFET with parasitics                                                                                                                            | 123  |

| 4.3  | The area comparison of a simple CS cascode LNA in single gate MOSFET and DG MOSFET.                                                                                                 | 124  |

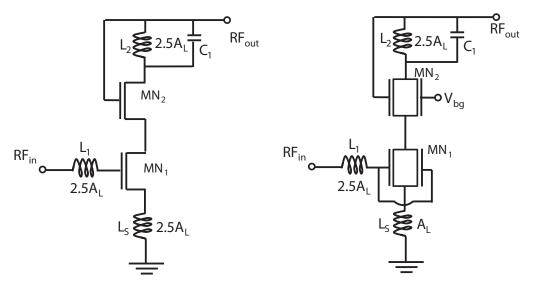

| 4.4  | The DG MOSFET based LNA in common source cascode configuration.                                                                                                                     |      |

|      | Transistors $MN_1$ operates in the symmetric mode while $MN_2$ and $MN_3$ operate                                                                                                   |      |

|      | in the independent mode with the back gates used for dynamic tuning[2], [14]                                                                                                        | 125  |

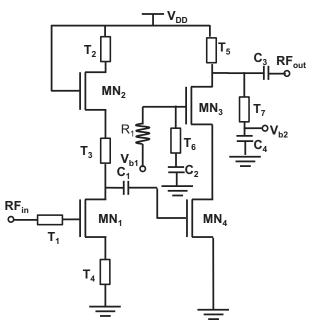

| 4.5  | The DG MOSFET based LNA in common source cascode configuration.                                                                                                                     |      |

|      | Transistors $MN_1$ and $MN_2$ operate in the symmetric mode while $MN_3$ and                                                                                                        |      |

|      | $MN_4$ operate in the independent mode with the back gates used for dynamic                                                                                                         |      |

|      | tuning. Unlike the 60 GHz LNA, in this circuit, the inductors are replaced by                                                                                                       |      |

|      | microstrip transmission lines.                                                                                                                                                      | 128  |

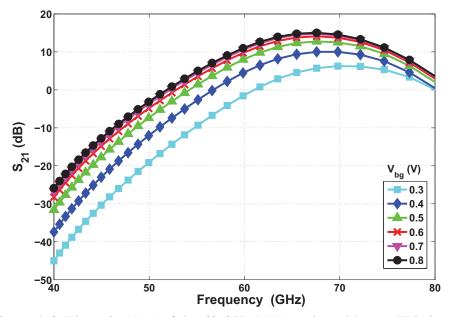

| 4.6  | The gain ( $S_{21}$ ) of the 60 GHz LNA varies with $V_{bg}$ . This is measured for $V_{bg} = 0.2 \text{ M} \pm 0.9 \text{ M} \pm 1.41$                                             | 120  |

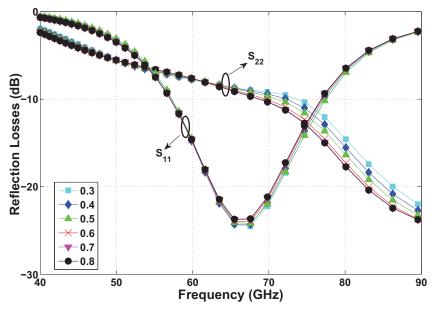

| 4.7  | 0.3 V to 0.8 V [14]                                                                                                                                                                 | 130  |

| 4./  | different $V_{bg}$                                                                                                                                                                  | 121  |

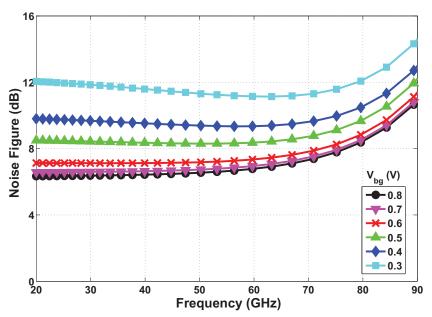

| 4.8  | The noise figure dependence on $V_{bg}$ of the LNA is evident. The NF changes by                                                                                                    | 151  |

| 7.0  | 4.3 dB in the tuning range of $V_{bg}$ at 65 GHz [14].                                                                                                                              | 132  |

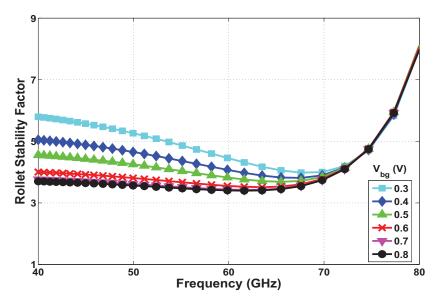

| 4.9  | The value of $K > 1$ , as one of the necessary condition, indicates the                                                                                                             | 102  |

| ,    | unconditional stability of the circuit.                                                                                                                                             | 133  |

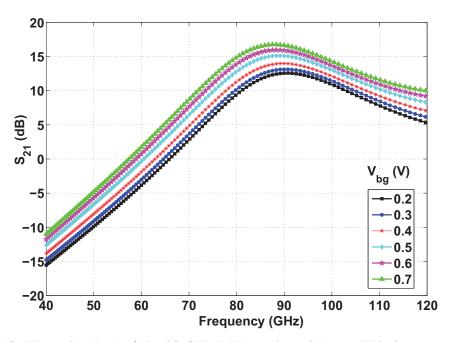

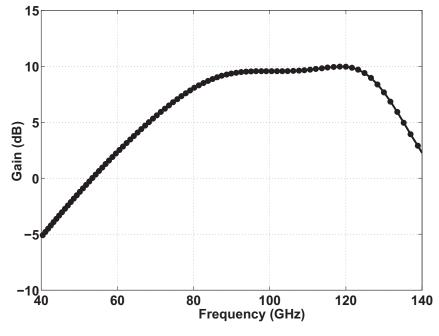

| 4.10 | The gain (S <sub>21</sub> ) of the 90 GHz LNA varies with $V_{bg}$ . This is measured for $V_{bg}$ =                                                                                |      |

|      | 0.2 V to 0.7 V                                                                                                                                                                      | 134  |

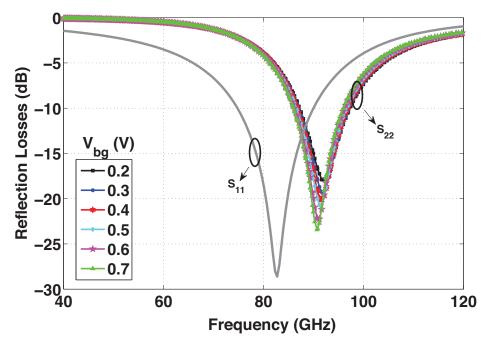

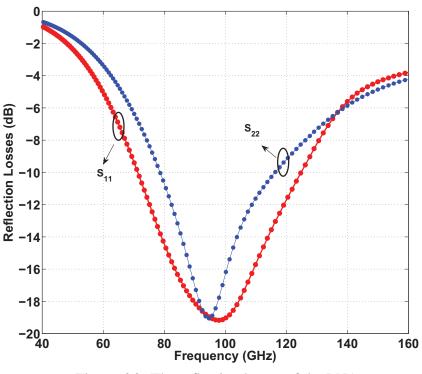

| 4.11 | The input and output return losses of the 90 GHz LNA ( $S_{11}$ and $S_{22}$ ) for                                                                                                  |      |

|      | different $V_{bg}$                                                                                                                                                                  | 135  |

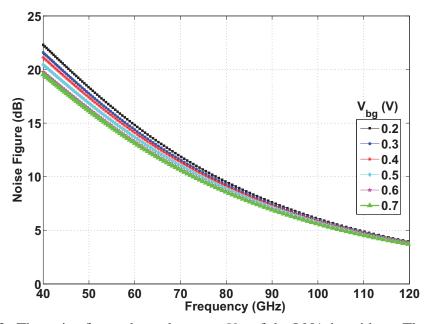

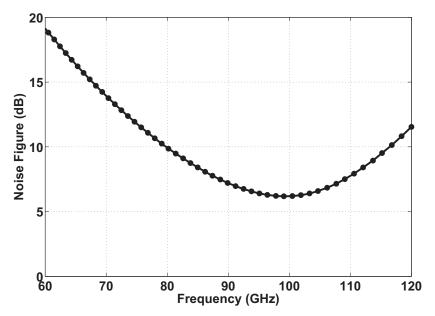

| 4.12 | The noise figure dependence on $V_{bg}$ of the LNA is evident. The NF changes by                                                                                                    |      |

|      | 1.5 dB in the tuning range of $V_{bg}$ at 90 GHz                                                                                                                                    | 135  |

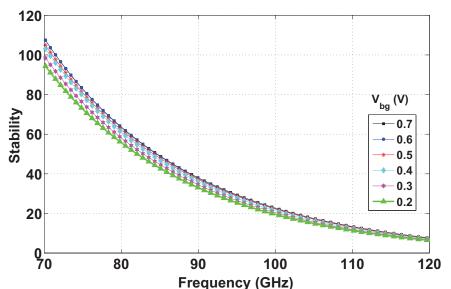

| 4.13 | The value of $K > 1$ , as one of the necessary condition, indicates the                                                                                                             |      |

|      | unconditional stability of the circuit.                                                                                                                                             | 136  |

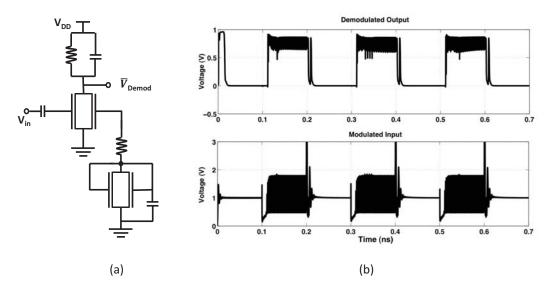

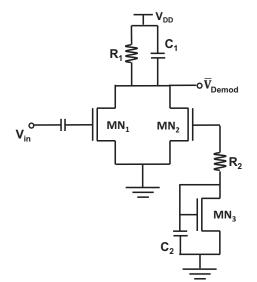

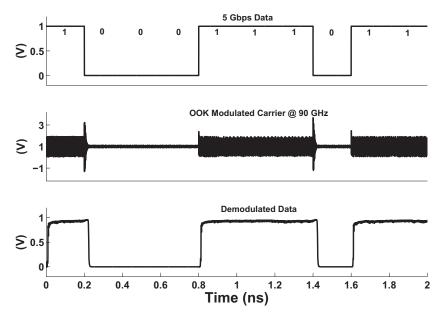

| 4.14 | a) Envelope Detector Circuit with only two DG MOSFETs. b) The modulated                                                                                                             |      |

|      | input consisting of the both the carrier and data and the recovered demodulated                                                                                                     | 100  |

|      | output consisting only of data sans the carrier [17]                                                                                                                                | 139  |

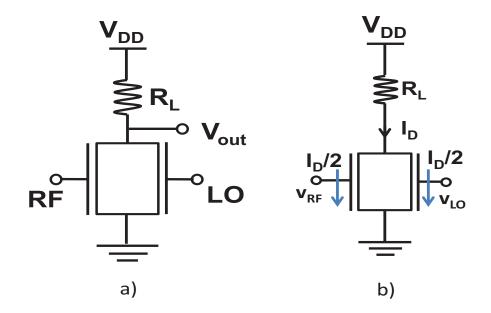

| 5.1  | DG-MOSFET a) RF Mixer Circuit b) Analysis for Non-Linearity                                                                                                                         | 1/1/ |

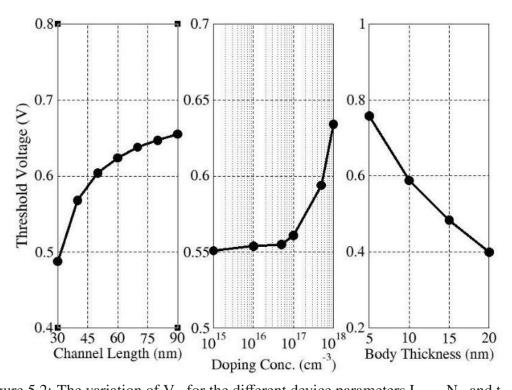

| 5.2  | The variation of $V_T$ for the different device parameters $L_{gate}$ , $N_A$ and $t_{Si}$ [18]                                                                                     |      |

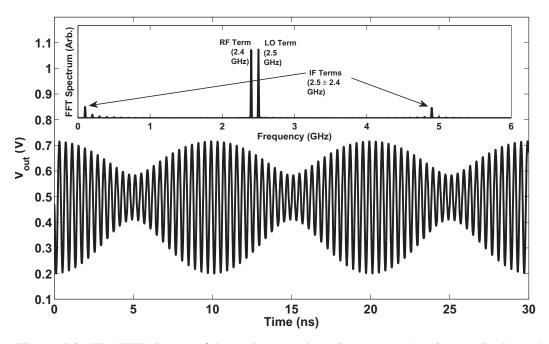

| 5.2  | The FFT (inset) of the voltage at the mixer output (main panel) shows both the                                                                                                      | 1 70 |

| 2.2  | sum & difference terms as well as additional higher order harmonics [18]                                                                                                            | 148  |

|      |                                                                                                                                                                                     |      |

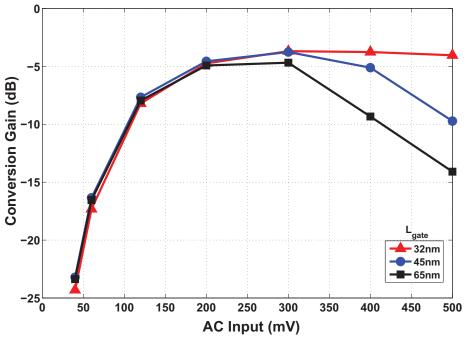

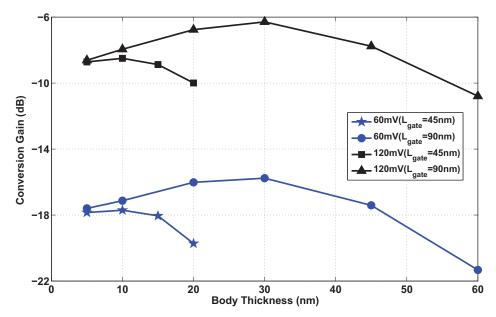

| 5.4           | Variation of conversion gain with $v_{lo}$ for different $L_{gates}$ [18]                         |       |

|---------------|---------------------------------------------------------------------------------------------------|-------|

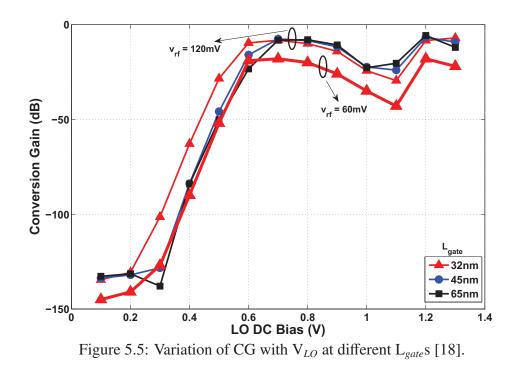

| 5.5           | Variation of CG with $V_{LO}$ at different $L_{gate}$ s [18]                                      | . 150 |

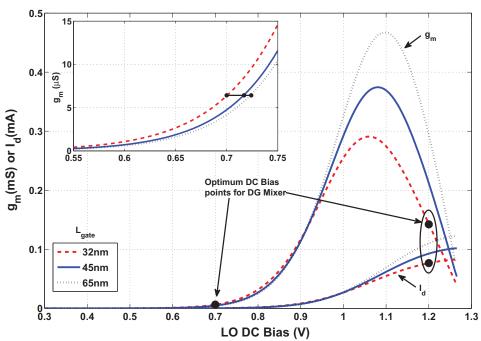

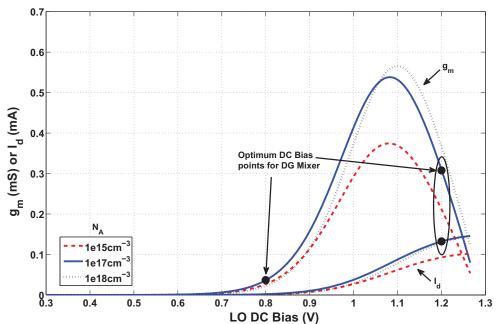

| 5.6           | Transconductance $(g_m)$ & drain current $(I_d)$ over DC bias for different $L_{gate}$ s.         |       |

|               | Out of two optimum bias points, the lower one at 0.7 V (32nm) is chosen for                       |       |

|               | better stability and power efficiency [18].                                                       | . 151 |

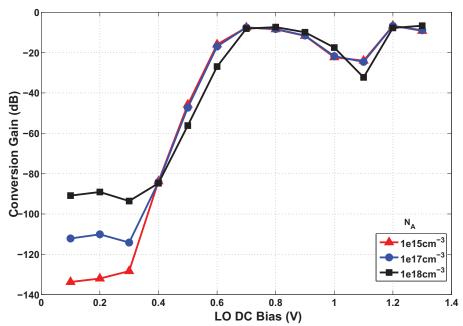

| 5.7           | Variation of CG with $V_{LO}$ at different N <sub>A</sub> s. The $V_{LO}$ has a weak correlation  |       |

|               | with different $N_A s$ [18].                                                                      | . 152 |

| 5.8           | Transconductance $(g_m)$ & drain current $(I_d)$ over DC bias for different N <sub>A</sub> s. Out |       |

|               | of two optimum bias points, the lower one at 0.8 V (1e17cm <sup>-3</sup> ) is chosen for          |       |

|               | better stability and power efficiency [18].                                                       | . 153 |

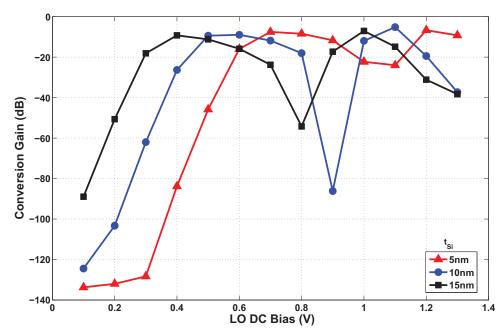

| 5.9           | Variation of CG with $V_{LO}$ at different $t_{Si}$ s. The strong correlation of $V_{LO}$ with    |       |

|               | different $t_{Si}$ can be noted. There is a shift of 0.4 V in the $V_{LO}$ for the optimum        |       |

|               | CG in moving from 15 nm to 5 nm [18]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                | . 154 |

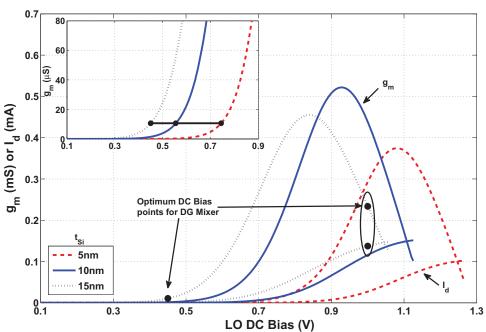

| 5.10          | Transconductance $(g_m)$ & drain current $(I_d)$ over $V_{LO}$ for different $t_{Si}$ s. Out of   |       |

|               | two optimum bias points, the lower one at 0.45 V (15nm) is chosen for better                      |       |

|               | stability and power efficiency [18]                                                               | . 155 |

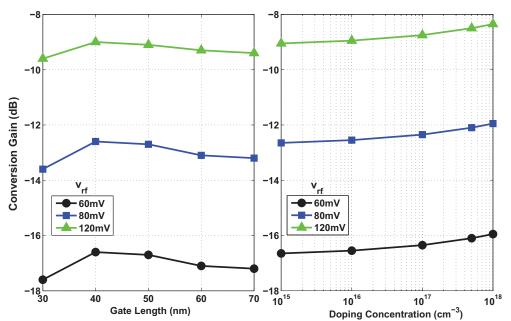

| 5.11          | Dependence of CG on the gate length ( $L_{gate}$ s) & doping concentration ( $N_A$ ) for          |       |

|               | different AC Inputs. The weak correlation of these two parameters on the CG                       |       |

|               | is clearly evident [18].                                                                          | . 156 |

| 5.12          | Dependence of CG on the body thickness $(t_{Si})$ for different AC Inputs. CG                     |       |

| 0.112         | varies with $L_{gate}$ because of short channel effects [18]                                      | . 157 |

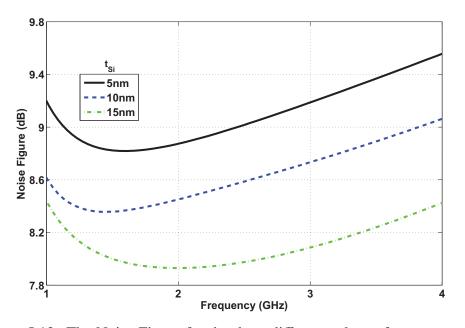

| 5.13          | The Noise Figure for the three different values of $t_{Si}$ s are measured against                |       |

| 0110          | frequency [18].                                                                                   | . 158 |

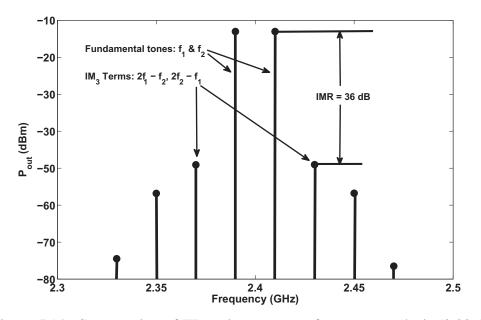

| 5.14          | Computation of IIP <sub>3</sub> using two tone frequency analysis (2.39 GHz and 2.41              |       |

|               | GHz) around 2.4 GHz [18].                                                                         | . 159 |

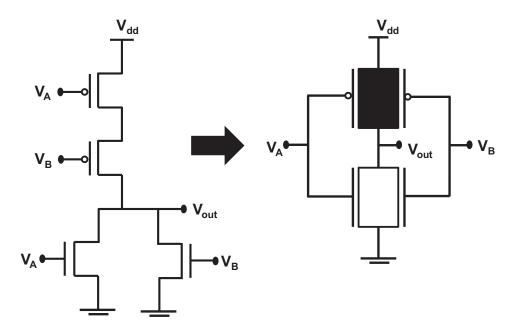

| 5.15          | 2-Input NOR Logic Gate in Conventional CMOS and its equivalent in DG-                             |       |

| 0110          | MOSFET. Two transistors are required in the DG-MOSFET. The PMOS in                                |       |

|               | DG-MOSFET is kept at a high- $V_T$ symbolized by a filled transistor [14], [19].                  | 160   |

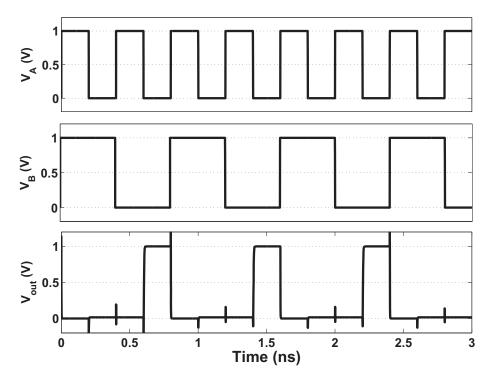

| 5.16          | 2-Input DG-MOSFET NOR Logic waveform as simulated in HSPICE for $V_{DD}$                          | . 100 |

| 0.10          | $= 1 V [14], [19], \dots, \dots, \dots, \dots, \dots, \dots, \dots, \dots, \dots, \dots$          | 161   |

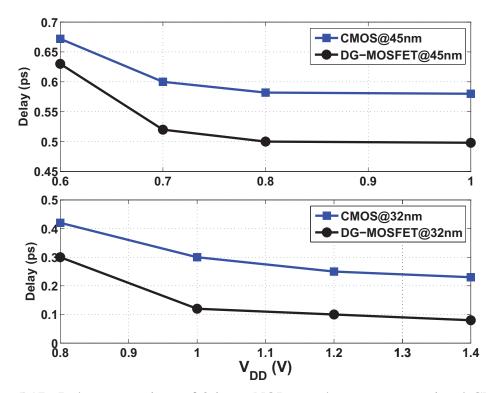

| 5 17          | Delay comparison of 2-input NOR gate between conventional CMOS and DG-                            | . 101 |

| 0.17          | MOSFET for different supply voltages [14], [19]                                                   | 162   |

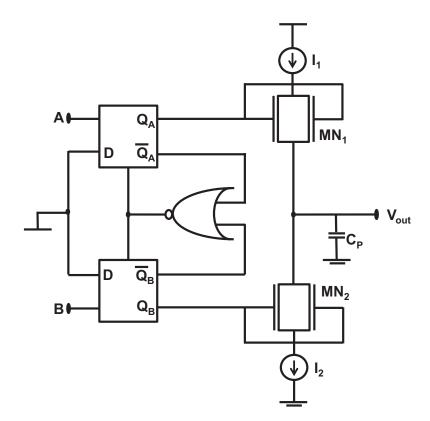

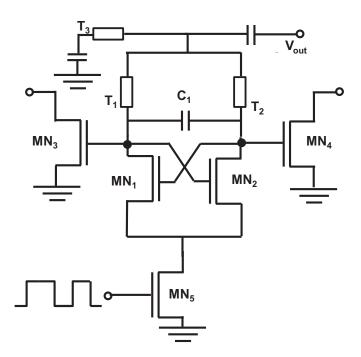

| 5 18          | The Charge Pump PFD circuit implemented with DG-MOSFETs [14], [19].                               |       |

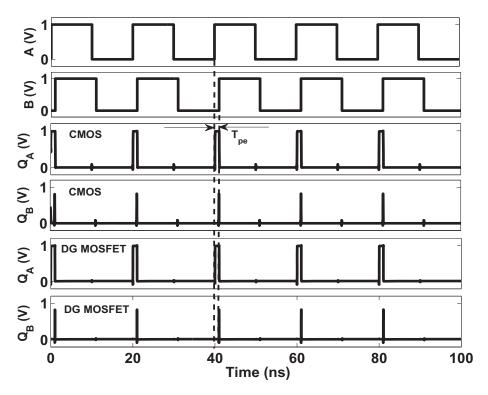

|               | Phase error characteristics of two pulses A & B for conventional CMOS and                         | . 105 |

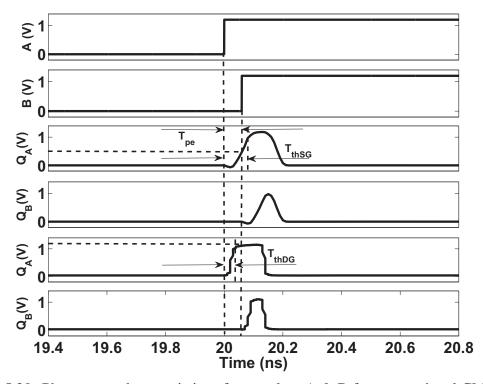

| 5.17          | DG-MOSFET for a phase error of 1 ns [14], [19]                                                    | 164   |

| 5 20          | Phase error characteristics of two pulses A & B for conventional CMOS and                         | . 101 |

| 0.20          | DG-MOSFET for a phase error of 60 ps at 32 nm gate length. ( $T_{thDG} \le T_{pe} \le$            |       |

|               | $T_{thSG}$ [14], [19]                                                                             | 165   |

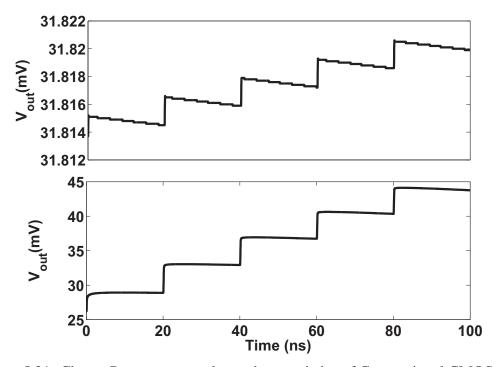

| 5 21          | Charge Pump output voltage characteristics of Conventional CMOS and DG-                           | . 105 |

| J. <u>4</u> 1 | MOSFET when $T_{thDG} \le T_{pe} \le T_{thSG}$ [14], [19]                                         | 166   |

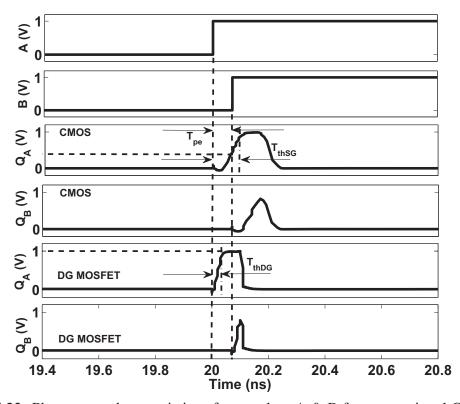

| 5 22          | Phase error characteristics of two pulses A & B for conventional CMOS and                         | . 100 |

| 5.22          | DG-MOSFET for a phase error of 80 ps at 45 nm gate length. ( $T_{thDG} \le T_{pe} \le$            |       |

|               | $T_{thSG}$ [14], [19]                                                                             | 167   |

|               | $I_{mSG}[1^{17}], [17]$                                                                           | . 107 |

| 6.1         | Push-Push VCO with OOK Modulation in 65 nm CMOS                                    | 171 |

|-------------|------------------------------------------------------------------------------------|-----|

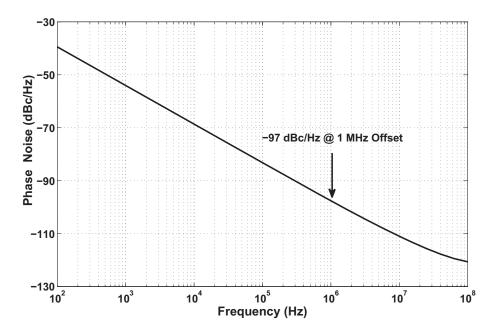

| 6.2         | The phase noise of the VCO. The Push Push VCO configuration has a phase            |     |

|             | noise of -97 dBc/Hz at 1 MHz offset                                                | 172 |

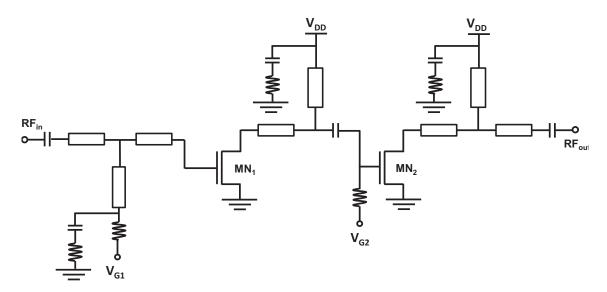

| 6.3         | Power Amplifier circuit in 65 nm CMOS.                                             |     |

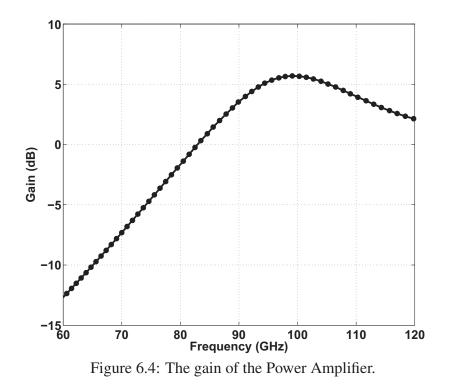

| 6.4         | The gain of the Power Amplifier.                                                   | 173 |

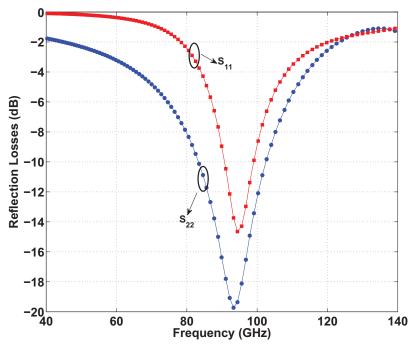

| 6.5         | The reflection losses of the Power Amplifier.                                      | 174 |

| 6.6         | Low Noise Amplifier circuit in 65 nm CMOS.                                         | 175 |

| 6.7         | The gain of the LNA.                                                               | 175 |

| 6.8         | The reflection losses of the LNA                                                   | 176 |

| 6.9         | The noise figure of the LNA.                                                       |     |

| 6.10        | The Envelope Detector in 65 nm CMOS                                                |     |

| 6.11        | The verification of OOK demodulation.                                              | 178 |

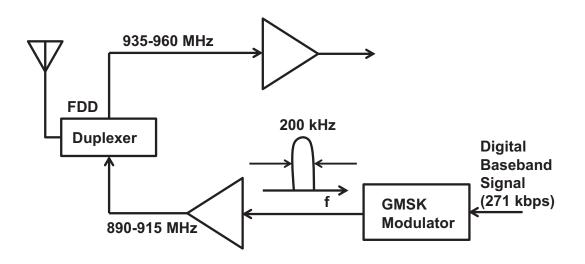

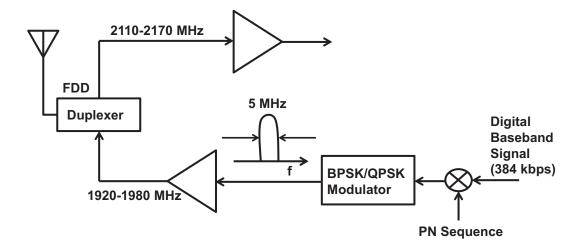

| A.1         | GSM air interface.                                                                 | 198 |

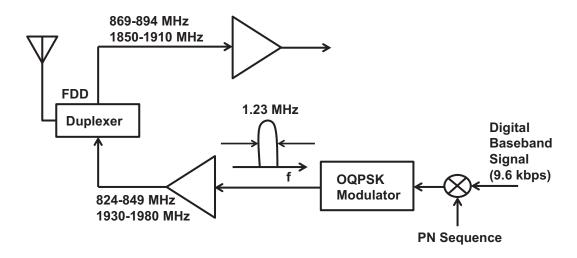

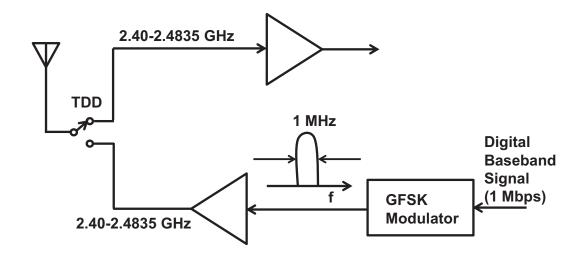

| A.2         | CDMA (IS-95)air interface.                                                         |     |

| A.3         | WCDMA (IMT-2000)air interface.                                                     |     |

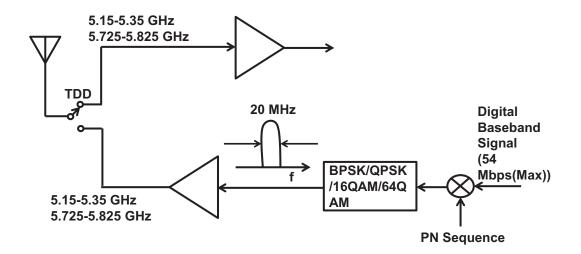

| A.4         | Bluetooth air interface.                                                           |     |

| A.5         | IEEE 802.11a air interface.                                                        |     |

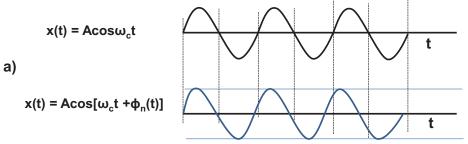

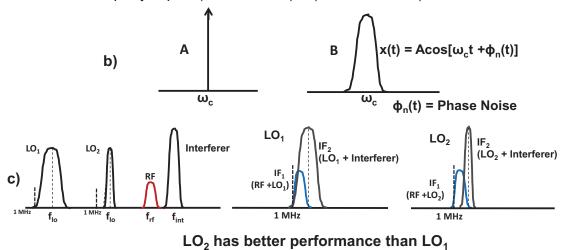

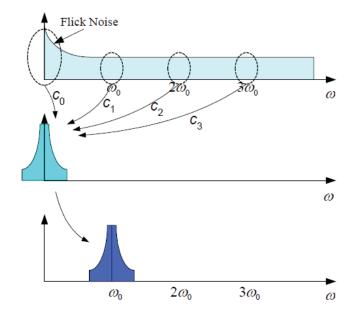

| <b>B</b> .1 | a) Illustration of the definition phase noise b) Illustration of the importance of |     |

|             | the phase noise.                                                                   | 203 |

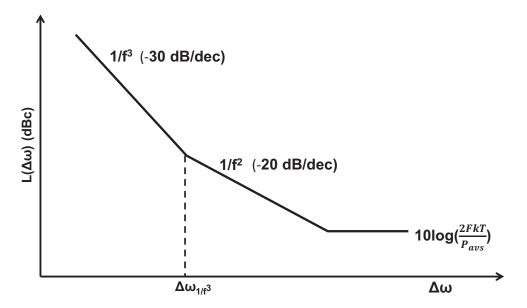

| B.2         | Plot of the phase noise of an oscillator versus offset from carrier showing        |     |

|             | different noise regions.                                                           | 204 |

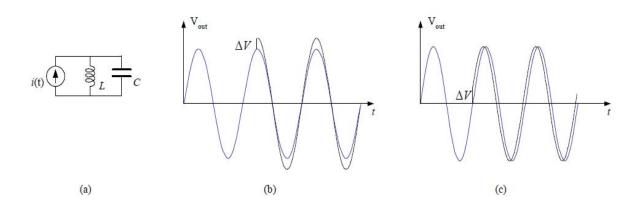

| B.3         | Impulse injected into an ideal LC tank (a) at the peak (b) and the zero crossing   |     |

|             | (c) [20]                                                                           | 205 |

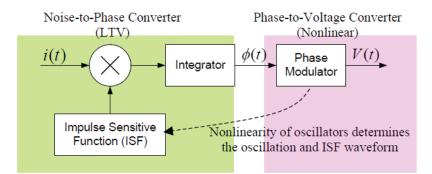

| B.4         | Block diagram of the LTV phase noise model [20].                                   | 207 |

| B.5         | Conversion of noise to phase fluctuations and phase-noise sidebands [20]           | 209 |

## **1** INTRODUCTION & MOTIVATION

#### 1.1 Wireless Communication

Wireless communications today impact and enable a plethora of applications. Among these, the mobile-cellular industries is the backbone of wireless communication and the most promising. In the last few years, the global subscription in mobile-cellular communication has exceeded the number of wireline telephone subscriptions. The worldwide mobile-cellular subscription in 2014 has reached 6.915 billion [21], which is almost equal to the world population of 7.1 billion. This remarkable figure speaks for itself the importance of mobile-cellular services and wireless communication, in general. Today's mobile-cellular handset is no more a device for voice communication but a wholesome digital personal assistant where multimedia products are consumed via wireless communications links ranging from wireless data transfer and high-speed internet access. These features are collectively termed as the fourth-generation (4G) cellular and paved the way for the migration of conventional mobile phones to smart-phones. These smart-phones and 4G have played together an important socio-economic role in motivating research in new wireless signal processing methods and currently research is undergoing towards fifthgeneration (5G) cellular, where speed is the primary ingredient intended for ultra fast data communications and internet.

Besides the mobile-cellular telephony, other contexts for wireless communications also exist which are primarily centered around different wireless technologies such as Zigbee, Bluetooth, wireless local area network (WLAN) systems, wireless personal area network (WPAN) systems, wireless metropolitan area network (WMAN) systems etc. [21]. These wireless technologies provide the framework for a variety of applications, which include, wideband internet access, local telephony service, wireless data transfer of high-speed entertainment content of high-definition video and high-quality audio. Similar to 4G, these

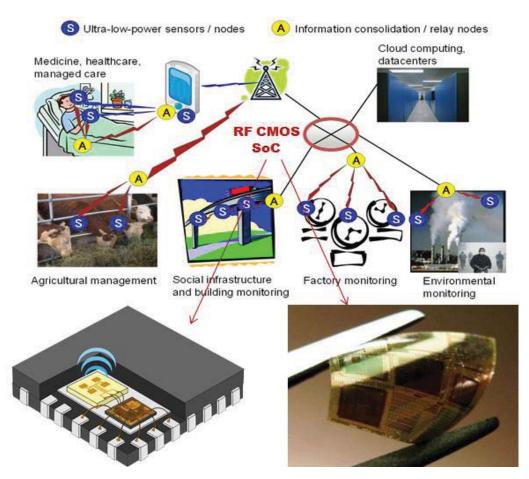

Figure 1.1: Illustration of application of wireless communication in different areas [3], [4],[5].

technologies have spurred significant research in signal coding, transmission, processing as well as hardware development for wireless. In Fig. 1.1, the application of wireless communication in various segments is demonstrated.

Finally, another trend in wireless communication industry is the incessant search for more bands and bandwidth in data links serving content-rich and dynamic multi-media systems, which can only be found at higher speeds > 10 GHz. In fact it is anticipated that 0.1 to 0.5 THz wireless circuits will be readily achievable using standard Silicon materials and CMOS devices. Since, a great majority of circuits and systems developed in this

dissertation operate around 60-100 GHz, our work is at the forefront of this strategically important research area that is likely the final territory, besides optical applications, not conquered by silicon integrated circuits. Work described here is especially relevant and useful for devices and systems currently smaller yet booming segment of wireless communications industry. Particularly, in the spirit of Fig. 1.1, it can be related to the framework of solutions for hig-capacity, low cost, on and off chip wireless data links in conventional computational platforms as well as futuristic highly-connected networks of 'internet of things' with many distributed and non-conventional data collection, processing and analysis systems.

#### **1.2 Integrated Circuits**

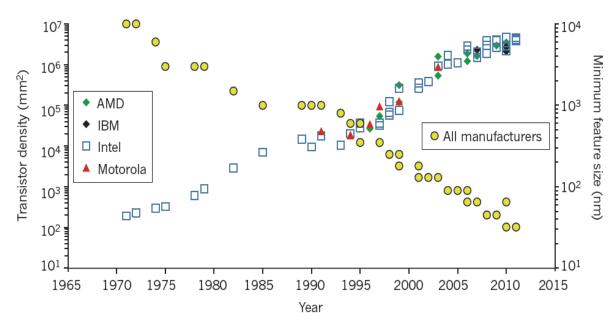

As we explore hierarchically the context and motivation for this work, next important fact to realize is that today's nanochips contain billions of transistors on a single die that integrates whole electronic systems as opposed to sub-system parts. This can be observed from the Fig. 1.2. Together with ever higher frequency performances resulting from transistor scaling and material improvements, it thus become possible to include on the same silicon chip analog functionalities and communication circuitry that was once reserved to only an elite class of compound III-V semiconductors [14]. It appears that in the last stretch of Moore's scaling down to 5 nm range, only limited by fabrication at atomic dimensions and fundamental physics of conduction and insulation, nanochips will only become more capable and faster, due to novel types of transistor geometries and functionalities as well as better integration of passive elements, antennas and novel isolation approaches [14].

Hence our circuit design efforts have been largely framed within system-on-chip (SoC) and/or fully-integrated single-chip solutions in which we use a single technology platform (CMOS) in its currently available or projected future forms (Double Gate MOSFET) to

Figure 1.2: The evolution of transistor gate length (minimum feature size) and the concentration of transistors in microprocessors with time. Between the years 1970 and 2011, the gate length of MOSFETs shrank from 10  $\mu$ m to 28 nm (yellow circles; y axis right), and the number of transistors per mm<sup>2</sup> increased from 200 to over 1 million (diamonds, triangles and squares represent data for the four main microprocessor manufacturers [Motorola (Currently Freescale)]; y axis, left) [6].

implement all necessary digital, analog and mixed-signal system blocks. This approach not only lowers cost and easier to fabricate, it is also the natural conclusion given the fact that Moores scaling is likely to take systems into 0.1-0.5 THz range in clock speed or carrier frequencies [14].

#### 1.3 Novel Multi-Gate & 3D Transistors

As device scaling aggressively continues down to sub-22nm scale, MOSFETs built on Silicon on Insulator (SOI) substrates with ultra-thin channels and precisely engineered source/drain contacts have started to replace conventional bulk devices [22], [23]. Such SOI MOSFETs are built on top of an insulation (SiO<sub>2</sub>) layer, reducing the coupling capacitance between the channel and the substrate as compared to the bulk CMOS [23]. The other advantages of an SOI MOSFET include higher current drive and higher speed, since doping-free channels lead to higher carrier mobility [23]. Additionally, the thin body minimizes the current leakage from the source to drain as well as to the substrate, which makes the SOI MOSFET a highly desirable device applicable for high-speed and low-power applications [23]. However, even these redeeming features are not expected to provide extended lifetime for the conventional MOSFET scaling below 22nm and more dramatic changes to device geometry, gate electrostatics and channel material are required. Such extensive changes are best introduced gradually, however, especially when it comes to new materials [23].

Therefore it is still the novel 3D transistor geometries with multi gates and highly optimized electrostatic design and doping landscape, rather than integration of brand new materials such as graphene or paradigm shifts such as spintronics, that is driving transistor development and evolution. Thus in this dissertation, we have also used this very fact as a guideline in research and largely focused on novel multi-gate (double-gate) transistor architecture as the building blocks of novel circuits intended for high-capacity, low-cost, highly integrated wireless solutions mentioned earlier. It is this focus on 3D transistor geometry and electrostatic design [23], rather than novel materials, that make the multi-gate (i.e double, triple, surround) MOSFETs as one of the most suitable candidates for the next phase of evolution in Si MOSFET technology [6]-[10].

Hence, research explained in this dissertation not only incorporates practical considerations and latest trends in systems and circuits aspects, it also includes competitive device elements that will most likely define the next, and final, decade of Moores scaling, making this work quite relevant and interesting for years to come.

#### 1.4 Research Goals & Accomplishments

#### **1.4.1 Research Goals**

Based on trends and backdrop provided above, the primary objective of this research is to establish the DG-MOSFET, popularly known as FinFETs, as a better and viable alternative to bulk CMOS in the design of next generation wireless communication integrated circuits operating at radio frequencies. Due to commercial unavailability of the DG-MOSFET technology, this has been verified in academic SPICE models by industry standard computer simulations and/or developing small signal quantitative models and/or qualitative analysis of the various wireless communication circuits. Besides wireless communication, which has been the primary target of the research, these novel circuits are equally suited for applications in satellite communications/navigation, sensor networks and ultra low power wireless body area networks (Fig. 1.1), which are also research directions with extremely large market implication and societal significance.

To fulfill this prime objective and explore novel circuitry, our design efforts have included the following elements which are the building blocks to many electronic systems, not just wireless communication circuits. The circuits investigated include [14]:

- Oscillators (LC, Quadrature and Relaxation)

- OOK Modulators

- Power Amplifiers

- Low Noise Amplifiers

- RF Mixers

- OOK Demodulator/Envelope Detectors

- Charge Pump Phase Frequency Detector

As a product of the primary objective, we have the following specific research goals that define this dissertation:

- Design of ultra-low power non-coherent OOK transciever (TRx) based on DG-MOSFET transistor. Such TRxs are known for their simplicity as well as lowpower, compact architecture that is most applicable to our target applications: ultrashort range and extremely efficient (low energy/per transmitted bit) fully integrated wireless data links.

- Design of critical system blocks operating in 60-100 GHz range, such as power amplifiers (PA), low-noise amplifiers (LNA), mixers, oscillators, envelope and charge pump phase frequency detectors, which are found in all types of coherent and non-coherent communication systems, using DG-MOSFET devices. This objective greatly broadens the applicability of the novel circuits developed in this circuit beyond OOK TRx applications.

- Illustration of industry-level design capability and proof-checking of developed system blocks using state-of-the-art CAD design tools and academically available 65 nm CMOS technology platform. In the absence of practically available DG-MOSFET technology at the writing of this dissertation, design of 65 nm CMOS technology kit available via MOSIS academic foundry is to be used to achieve this objective, providing myself and our research group with unique know-how to implement actual chips for a given technology.

#### 1.4.2 Accomplishments

The research establishes DG-MOSFET as an effective and viable alternative to single gate CMOS technology in the design of radio frequency analog integrated circuits mostly in the 60-100 GHz range. Besides several device advantages of DG-MOSFET over conventional CMOS, the current flag bearer of the semiconductor technology, and described in the next chapter, this research brings out several advantages of DG-MOSFETs in the radio frequency analog circuits domain. Although previous attempts have been successfully made in the design of digital and memory circuits with DG-MOSFETs, no detailed and focussed attempts have been made prior to this work to establish the viability of DG-MOSFET in the design of the radio frequency analog integrated circuits which finds application in wireless communication among others. The specific accomplishments of this research for different radio frequency integrated circuits are as follows:

Oscillators:

- A more lenient oscillatory criterion of common mode DG-MOSFET based LC oscillator than conventional CMOS is analyzed quantitatively.

- An independent mode DG-MOSFET LC Voltage Controlled Oscillator (VCO) is designed in which the voltage controls the oscillation frequency via the back gate bias of the DG-MOSFETs without the requirement of any MOS varactors as needed in single gate conventional CMOS for voltage control of the oscillation frequency thus making the circuit more compact.

- Qualitatively analyzed and verified through simulation a new formulation of the voltage controlled characteristic of the DG-MOSFET LC oscillator.

- Designed the DG-MOSFET LC quadrature oscillator with reduced transistor count from eight in conventional CMOS to four in the DG-MOSFET version, enabling faster performance by reducing parasitics as well as area usage.

- A novel DG-MOSFET based relaxation oscillator is designed in which the comparator circuit required in conventional CMOS is omitted by utilizing back gate

biasing of the DG-MOSFET, making the circuit faster as well as area and power efficient.

- The voltage controlled operation of the relaxation oscillator is demonstrated in addition to the existing current-controlled oscillation operation. The voltage controlled operation aids in high precision frequency tuning, a feature not possible in conventional CMOS based current-controlled relaxation oscillator.

- Through computer simulation verified a better or comparable phase noise performance than CMOS for all the DG-MOSFET oscillators.

**OOK Modulator:**

• A novel area efficient single DG-MOSFET modulator is designed. A second highthreshold DG-MOSFET is added for better switching operation than CMOS owing to strict channel control.

Power Amplifier:

- Established the adaptive gain tuning capability of DG-MOSFET without any additional transistors for power efficient applications.

- Through simulation verified better or comparable performance metrics of DG-MOSFET power amplifiers compared to CMOS and other III-V technology alternatives.

Low Noise Amplifier:

• Emphasized the area efficiency of the common source inductive degeneration Low Noise Amplifier (LNA), the most widely used LNA topology, via quantitative small signal modelling.

- Verified the gain switching of the DG-MOSFET LNA without any additional transistors, making the circuit much faster and area efficient compared to CMOS.

- Through simulation verified better or comparable performance metrics of DG-MOSFET LNAs compared to CMOS and other III-V technology devices.

Envelope Detector:

• Designed an envelope detector based on two DG-MOSFETs.

#### RF Mixer:

- Developed the analytical verification of the single DG-MOSFET RF Mixer operation.

- Analysed a novel bias optimization technique for DG-MOSFET RF Mixer.

Charge Pump Phase Frequency Detector:

• Analyzed through computer simulations, DG-MOSFET to be a better alternative for dead zone avoidance in phase locked loops.

#### OOK TRx in 65 nm RF CMOS:

• Apart from this accomplishments with DG-MOSFETs, in this research a power efficient, high bandwidth OOK transceiver (TRx) in 65 nm RF CMOS technology from IBM in the 60-100 GHz range for on-chip network applications is also implemented. This helped to develop the know-how to design and simulate commercial mm-wave CMOS circuits using industry-grade software and analysis tool.

#### **1.5** Dissertation Organization

In the following, we describe the general organization and structure of the chapters making up this dissertation work.

- Chapter 2 reports the necessary background of MOS technology, DG-MOSFET device, microwave fundamentals and wireless communication.

- Chapter 3 reports the research on DG-MOSFET non-coherent OOK transmitter, which include both the LC and relaxation oscillators, OOK Modulator and Power Amplifiers.

- Chapter 4 reports the research on DG-MOSFET non-coherent OOK receiver, which include the LNA and Envelope Detector.

- Chapter 5 reports the research on DG-MOSFET RF mixer primarily used for down conversions in coherent receivers. It also reports the research on DG-MOSFET Charge Pump Phase Frequency detector which is also used for coherent detection in receiver.

- Chapter 7 reports an extended comparative research onto an OOK TRx design in commercial 65 nm RF CMOS technology from IBM.

- Chapter 8 reports on the conclusion and future work of the dissertation.

#### **1.6 Analysis & Design Tools**

The technologies and simulators used in the analysis and design of the transceiver (TRx) circuits in DG-MOSFET are tabulated in this section. The ASU PTM FinFET models [26] and UFDG Model [27] are used to investigate the characteristics of the novel circuits. It should be noted only the technologies reported in this dissertation are mentioned. For instance, the work on Power Amplifier and the 60 GHz Low Noise Amplifier have been done also at ASU PTM 32 nm FinFET technology and published in [16] and [2] respectively, however not reported in the dissertation and hence not mentioned in Table 1.1.

The work in Chapter 6 on OOK TRx design with commercial CMOS has been implemented using the 65 nm RF CMOS technology from IBM. The different circuit blocks used in the design of the TRx are elucidated in Table 1.2.

| TRx Circuit                               | Technology                                   | Simulator            |

|-------------------------------------------|----------------------------------------------|----------------------|

| LC Oscillator                             | ASU PTM 32 nm FinFET                         | Synopsys HSPICE RF   |

| Relaxation Oscillator                     | UFDG Model                                   | UFDG SPICE Simulator |

| OOK Modulator                             | ASU PTM 32 nm FinFET                         | Synopsys HSPICE RF   |

| Power Amplifier                           | ASU PTM 45 nm FinFET                         | Synopsys HSPICE RF   |

| Low Noise Amplifier (60<br>GHz & 90 GHz)  | ASU PTM 45 nm & 32 nm<br>FinFET respectively | Synopsys HSPICE RF   |

| Envelope Detector                         | ASU PTM 45 nm FinFET                         | Synopsys HSPICE RF   |

| RF Mixer                                  | UFDG Model                                   | UFDG SPICE Simulator |

| Charge Pump Phase Fre-<br>quency Detector | ASU PTM 32 nm & 45 nm<br>FinFET              | Synopsys HSPICE      |

Table 1.1: Analysis & Design Tools for DG-MOSFET

| TRx Circuit             | Technology    | Simulator         |

|-------------------------|---------------|-------------------|

| LC Oscillator+OOK Modu- | 65 nm RF CMOS | Cadence SpectreRF |

| lator                   |               |                   |

| Power Amplifier         | 65 nm RF CMOS | Cadence SpectreRF |

| Low Noise Amplifier     | 65 nm RF CMOS | Cadence SpectreRF |

| Envelope Detector       | 65 nm RF CMOS | Cadence SpectreRF |

Table 1.2: Analysis & Design Tools for RF CMOS

### 2 BACKGROUND

#### 2.1 MOSFET Fundamantals

#### 2.1.1 MOSFET Operation

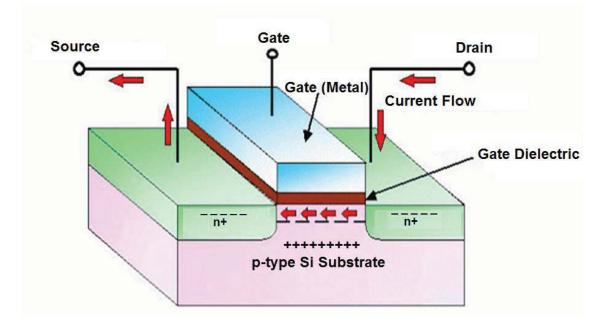

Before proceeding to DG-MOSFET, a short description of its predecessor, the conventional single gate MOSFET is hereby provided. Fig. 2.1 illustrates a single gate conventional MOSFET. The following points are easy to understand on the principle of operation of an n-channel MOSFET.

- Initially, the two terminals, drain and source are electrically isolated and hence there is no net flow of charge, no current, and the MOSFET is switched off

- The diffusion between electrons and holes results in recombination and thus depletes away most mobile charges in the junction region and results in a built-in electric field to be established, that counters further diffusion, making both the source and drain region electrically isolated from the substrate.

- When a positive voltage is applied at the gate minority electrons starts accumulating at the substrate beneath the oxide layer due to vertical electric field established. Thus electron density can rise significantly in this top section of silicon right next to the oxide interface, as compared to bulk of the body of MOSFET, resulting in the formation of a channel layer between source and drain contacts. Due to relatively small gate bias, this regime is called weak inversion.

- As the inversion proceeds (gate become more positive in an n-MOSFET), the electrons from both the source and drain starts appearing in the substrate and populates beneath the gate at the uppermost surface of the substrate. The transistor is now in strong inversion.

Figure 2.1: nMOSFET device structure and electrical contacts [7].

- The gate voltage at which an inversion channel is just formed is known as the threshold voltage.

- As the gate voltage is increased further, more and more electrons starts accumulating at the channel and simultaneously, a potential difference applied between the drain and source determines the flow of current in the channel along with the gate voltage. Thus the drain current is a function of two voltages.

- As the drain source voltage increases further, the potential difference between gate and silicon is reduced, and the vertical field effect is weakened, thus at the drain end of channel inversion is weakened or the channel is 'pinched off'.

- After the channel gets pinched off, the drain current ceases increasing with the drain source voltage and becomes almost constant. This is called the saturation region.

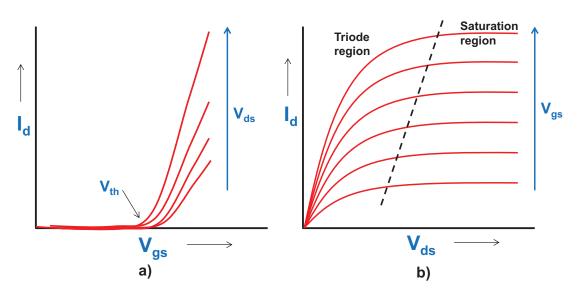

Figure 2.2: The MOSFET I-V Characteristics a)  $I_d$ - $V_{gs}$  b)  $I_d$ - $V_{ds}$ .

#### 2.1.2 I-V Characteristics

As informed in the earlier section, the drain current,  $I_d$  is function of two voltages, the gate-source voltage and the drain-source voltage. The  $I_d$  for an nMOS is thus given as [28],

$$I_d = \mu_n C_{ox} \frac{W}{L} [(V_{gs} - V_{th}) V_{ds} - \frac{1}{2} V_{ds}^2]$$

(2.1)

Here,  $\mu_n$  is the mobility of charge carrier (electron here),  $C_{ox}$  is the capacitance of the insulating oxide layer, W & L are width and length of the MOSFET respectively. The gate-source voltage, drain-source voltage and the threshold voltage are given by  $V_{gs}$ ,  $V_{ds}$  &  $V_{th}$  respectively. The voltage term,  $V_{gs} - V_{th}$  is called the overdrive voltage and  $\frac{W}{L}$  is the aspect ratio of the device. At saturation,  $V_{ds} = V_{gs} - V_{th}$ , therefore, eqn. (2.1) can be written as,

$$I_{dmax} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th})^2$$

(2.2)

If  $V_{ds} \leq V_{gs} - V_{th}$ , the device operates in the active or triode region. In this region, when,  $V_{ds} \ll V_{gs} - V_{th}$ , eqn. (2.1) reduces to,

$$I_d = \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th}) V_{ds}$$

$$\tag{2.3}$$

Figure 2.3: The basic CMOS device architecture [8].

The drain current becomes a linear function  $V_{ds}$  for a fixed gate-source voltage and the transistor behaves as a resistor following Ohm's law. In Fig. 2.2a & b, the  $I_d$ - $V_{gs}$  &  $I_d$ - $V_{ds}$  characteristics are illustrated respectively.

#### 2.1.3 Complementary MOS Architecture

In complementary MOS (CMOS) technologies, both nMOS and pMOS transistors are utilized and operated in tandem. The pMOS and nMOS devices are be fabricated in the same wafer or substrate. Hence, one device type is placed on a 'local substrate' usually called a 'well'. In most conventional bulk MOSFET of today's processes, the pMOS device is fabricated in an n-well. The n-well must be connected to a potential such that the source/drain junction always remain reverse biased under all conditions [28]. This is to ensure the source/drain junction does not create and act as a diode in forward biased. In most circuits n-well is tied to the positive supply voltage. Similarly for the nMOS the p-substrate is connected to the ground. This is illustrated in Fig. 2.3.

The two most essential features of CMOS devices are immunity to high noise and low static power consumption (ideally zero). Since one transistor of the pair is always off, the series combination consumes significant power only momentarily when switching between on and off states [8]. Consequently, CMOS devices do not create as much waste heat

as other forms of logic during static operation such as NMOS or transistor-transistor logic (TTL). They usually have some standing current even when not switching state [8]. CMOS also allows a high concentration of logic functions on a chip, since transistors are typically the smallest element of gate-controlled switching and takes less space than resistors [8]. Another important advantage of CMOS is scalability and is discussed later in the section.

#### 2.1.4 Power Dissipation

The power dissipation in CMOS comes from two components. The static dissipation which arises due to non-ideal circumstances such as [28],

- subthreshold conduction through OFF transistors

- tunneling current through gate oxide

- leakage through reverse-biased diodes (p-n junctions formed between source/drain and substrate)

- contention current in ratioed circuits

Dynamic dissipation is due to

- charging and discharging of load capacitances arising out of transistor switching

- short circuit current while both PMOS and NMOS networks are partially ON

The static power dissipation is a serious concern in sub-32 nm devices and among other reasons, the mitigation to this led to the development of advanced CMOS devices [28].

The subthreshold leakage current responsible for static power dissipation during transistor OFF state is given as [29],

$$I_{d_{subth}} = K.e^{(\frac{(V_{gs}-V_{th})q}{nkT}}(1-e^{\frac{-qV_{ds}}{kT}})$$

(2.4)

where K is a process dependent constant [29]. The tunneling current through gate oxide is caused by carriers tunneling through a classically forbidden energy barrier [30]. Ideally the reverse biased p-n junction between source/drain and substrate will not conduct any current. However, a small amount of current flows due to minority carriers resulting in static power dissipation.

The average power dissipation in any CMOS circuit can be written as [28],

$$P_{av} = \frac{1}{T} \int_0^T i_{supply}(t) V_{supply}$$

(2.5)

The primary source of dynamic dissipation is charging of the load capacitance. Suppose a load  $C_L$  is switched between the supply,  $V_{DD}$  and GND at an average frequency  $f_{sw}$ . Over time T, load is charged and discharged  $Tf_{sw}$  times. In one complete charge/discharge cycle, a total charge of  $Q = CV_{DD}$  is transferred between  $V_{DD}$  and GND. Now the average dynamic power dissipation can be written from eqn. 2.5,

$$P_{dyn} = \frac{V_{DD}}{T} \int_{0}^{T} i_{DD}(t)$$

(2.6)

Taking the integral of the current over the interval T, the total charge delivered during time T is,

$$P_{dyn} = \frac{V_{DD}}{T} [T f_{sw} C V_{DD}] = C V_{DD}^2 f_{sw}$$

(2.7)

Therefore, the higher the number of switching events, the greater the dynamic power consumption.

### 2.1.5 MOSFET Scaling

The scalability of MOSFET in CMOS architecture is one of the primary reason that CMOS became the most dominant technology to be implemented in analog/digital VLSI chips. The ideal scaling theory follows three rules [28]:

• All lateral and vertical dimensions are reduced by  $\alpha$ .

- The supply and threshold voltages are reduced by  $\alpha$ .

- All the doping levels are increased by  $\alpha$ .

The drain current in eqn.(2.2) following the above rules can be rewritten as,

$$I_{dmax,scaled} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{gs} - V_{th})^2 \frac{1}{\alpha}$$

(2.8)

The current capability of the transistor drops by a factor of  $\alpha$ . The same result applies for the drain current in the triode region too. The advantage of scaling however lies in the reduction of capacitances and power dissipation. The total channel capacitance is written as,

$$C_{ch,scaled} = \frac{1}{\alpha} WLC_{ox}$$

(2.9)

The power goes down by a factor of  $\alpha^2$ .

However as we go down in technology, there are serious consequences with scaling and the effects are discussed in the next section.

#### 2.2 Evolution to Multigate MOSFETs

#### 2.2.1 Limitations of CMOS

One of the fundamental limits in mixed-signal (digital & analog) CMOS circuit design is the intrinsic gain possible through a single transistor, which is determined by the ratio of transconductance  $g_m$  (ratio of output current to input voltage) over output conductance  $g_{ds}$ (the device's capacity to shunt its own current to ground or to 'steal useful signal intended for the load at the output) [31]. In CMOS, from the 250 nm to the 45 nm node, this ratio  $g_m/g_{ds}$  has decreased from 15 to 5 due to an increased  $g_{ds}$ . An extrapolation for 10 nm technology leads to an intrinsic gain close to unity. Moreover, even if we can make gate lengths so small, there are other requirements for proper scaling. From fabrication point of view an oxide thickness  $t_{ox}$  of around 1 nm is required for the 10 nm node to allow

Figure 2.4: Band Bending in Long channel & Short channel MOSFETS

sufficient channel control via the gate [31]. Since 1 nm corresponds to just a few atomic layers, further reduction of  $t_{ox}$  is difficult from a gate leakage, noise, and process variation point of view [31].