# A HANDS-ON SECURITY COURSE

by

# ANDREW HENNESSY

Submitted in partial fulfillment of the requirements

for the degree of Master of Science

Department of Electrical Engineering and Computer Science

CASE WESTERN RESERVE UNIVERSITY

May 2017

# CASE WESTERN RESERVE UNIVERSITY SCHOOL OF GRADUATE STUDIES

We hereby approve the thesis of

# Andrew Hennessy

candidate for the degree of Master of Science\*.

Committee Chair

Dr. Kenneth Loparo

Committee Member

Dr. Francis Merat

Committee Member

Dr. Gregory Lee

Date of Defense

April 6, 2017

\*We also certify that written approval has been obtained

for any proprietary material contained therein.

# Contents

| Li       | st of           | Tables                                  | v    |

|----------|-----------------|-----------------------------------------|------|

| Li       | st of           | Figures                                 | vi   |

| A        | cknov           | wledgments                              | viii |

| A        | bstra           | nct                                     | x    |

| 1        | Intr            | roduction                               | 1    |

|          | 1.1             | Other Courses at Different Universities | 2    |

|          | 1.2             | Organization of the Thesis              | 3    |

| <b>2</b> | Lab             | ooratory Environment                    | 4    |

|          | 2.1             | Equipment and Tools Needed              | 5    |

|          | 2.2             | Experimental Board                      | 6    |

|          |                 | 2.2.1 Purpose-Designed Board            | 6    |

|          |                 | 2.2.2 Off-the-shelf Boards              | 18   |

| 3        | $\mathbf{Syll}$ | labus                                   | 20   |

|          | 3.1             | Prerequisites                           | 20   |

|          | 3.2             | Credit Hours                            | 20   |

|          | 3.3             | Course Description                      | 20   |

|          | 3.4             | Key Concepts                            | 21   |

|   | 3.5                                                                                      | Course Requirements                        | 21                                                                                                         |

|---|------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------|

|   | 3.6                                                                                      | Student Expectations                       | 21                                                                                                         |

|   | 3.7                                                                                      | Lecture Schedule                           | 22                                                                                                         |

|   | 3.8                                                                                      | Grading                                    | 22                                                                                                         |

|   | 3.9                                                                                      | Student Conduct and Academic Integrity     | 23                                                                                                         |

|   | 3.10                                                                                     | Expected Outcomes                          | 23                                                                                                         |

| 4 | Lab                                                                                      | #1: Buffer Overflows                       | <b>24</b>                                                                                                  |

|   | 4.1                                                                                      | Objectives                                 | 24                                                                                                         |

|   | 4.2                                                                                      | Assignment                                 | 24                                                                                                         |

|   |                                                                                          | 4.2.1 Introduction                         | 24                                                                                                         |

|   |                                                                                          | 4.2.2 Instructions                         | 25                                                                                                         |

|   | 4.3                                                                                      | Assignment Files                           | 26                                                                                                         |

|   | 4.4                                                                                      | Solutions                                  | 29                                                                                                         |

|   |                                                                                          |                                            |                                                                                                            |

| 5 | Lab                                                                                      | #2: Diffie-Hellman Key Exchange            | 32                                                                                                         |

| 5 | <b>Lab</b><br>5.1                                                                        | #2: Diffie-Hellman Key Exchange Objectives | <b>32</b><br>32                                                                                            |

| 5 |                                                                                          |                                            |                                                                                                            |

| 5 | 5.1                                                                                      | Objectives                                 | 32                                                                                                         |

| 5 | 5.1                                                                                      | Objectives        Assignment               | 32<br>32                                                                                                   |

|   | 5.1<br>5.2                                                                               | Objectives                                 | 32<br>32<br>33<br>33                                                                                       |

| 5 | 5.1<br>5.2<br>Lab                                                                        | Objectives                                 | 32<br>32<br>33<br>33<br><b>3</b> 3<br><b>3</b> 4                                                           |

|   | <ul><li>5.1</li><li>5.2</li><li>Lab</li><li>6.1</li></ul>                                | Objectives                                 | <ul> <li>32</li> <li>32</li> <li>33</li> <li>33</li> <li>34</li> </ul>                                     |

|   | 5.1<br>5.2<br>Lab                                                                        | Objectives                                 | 32<br>32<br>33<br>33<br><b>34</b><br>34<br>34                                                              |

|   | <ul><li>5.1</li><li>5.2</li><li>Lab</li><li>6.1</li></ul>                                | Objectives                                 | <ul> <li>32</li> <li>32</li> <li>33</li> <li>33</li> <li>34</li> <li>34</li> <li>34</li> <li>34</li> </ul> |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>Lab</li> <li>6.1</li> <li>6.2</li> </ul>              | Objectives                                 | 32<br>32<br>33<br>33<br><b>34</b><br>34<br>34<br>34<br>35                                                  |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>Lab</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> </ul> | Objectives                                 | 32<br>32<br>33<br>33<br><b>34</b><br>34<br>34<br>34<br>35<br>36                                            |

|   | <ul> <li>5.1</li> <li>5.2</li> <li>Lab</li> <li>6.1</li> <li>6.2</li> </ul>              | Objectives                                 | 32<br>32<br>33<br>33<br><b>34</b><br>34<br>34<br>34<br>35                                                  |

|    |      | 6.4.2 AES Exercise                   | 38 |

|----|------|--------------------------------------|----|

| 7  | Lab  | #4: Bus Snooping                     | 39 |

|    | 7.1  | Objectives                           | 39 |

|    | 7.2  | Assignment                           | 39 |

|    |      | 7.2.1 Introduction                   | 39 |

|    |      | 7.2.2 Instructions                   | 40 |

|    |      | 7.2.3 References and Further Reading | 42 |

|    | 7.3  | Solution                             | 42 |

| 8  | Lab  | #5: Reverse Engineering              | 45 |

|    | 8.1  | Objectives                           | 45 |

|    | 8.2  | Assignment                           | 45 |

|    |      | 8.2.1 Introduction                   | 45 |

|    |      | 8.2.2 Instructions                   | 46 |

|    |      | 8.2.3 Deliverables                   | 47 |

|    | 8.3  | Solution                             | 48 |

| 9  | Lab  | #6: Physically Unclonable Functions  | 49 |

|    | 9.1  | Objectives                           | 49 |

|    | 9.2  | Assignment                           | 49 |

|    |      | 9.2.1 Introduction                   | 49 |

|    |      | 9.2.2 Instructions                   | 50 |

|    |      | 9.2.3 References                     | 51 |

| 10 | Fina | al Project & Paper                   | 52 |

|    | 10.1 | Objectives                           | 52 |

|    | 10.2 | Final Paper                          | 52 |

|    | 10.3 | Final Project                        | 53 |

| 10.3.1 Introduction $\ldots$ | 53 |

|---------------------------------------------------------------------------------------------------------------|----|

| 10.3.2 Part 0: Project Proposal                                                                               | 53 |

| 10.3.3 Part 1: Building the Project                                                                           | 54 |

| 10.3.4 Part 2: Attacking the Project                                                                          | 54 |

| 10.3.5 Part 3: Defending the Project                                                                          | 54 |

|                                                                                                               |    |

| 11 Results & Conclusion                                                                                       | 55 |

| 11.1 Results                                                                                                  | 55 |

| 11.1.1 Fall 2014                                                                                              | 55 |

| 11.1.2 Fall 2015                                                                                              | 58 |

| 11.2 Conclusion $\ldots$                                                                                      | 61 |

| A Proposed SAGES Course                                                                                       | 62 |

| B Layout Files                                                                                                | 66 |

| Bibliography                                                                                                  | 75 |

# List of Tables

| 2.1  | The Bill of Materials for the purpose-designed board                  | 8  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Pin Mapping between the Custom Board, the Arduino Leonardo and        |    |

|      | the native pin names                                                  | 15 |

| 2.3  | Pin Mapping between the Custom Board and the native pin names for     |    |

|      | the CPLD and microcontroller.                                         | 16 |

| 7.1  | The contents of an $I^2C$ transaction between the microcontroller and |    |

|      | the accelerometer                                                     | 43 |

| 8.1  | Example Bill of Materials for the assignment.                         | 47 |

| 11.1 | The sequence of assignments for the Fall 2014 version                 | 56 |

| 11.2 | The sequence of assignments for the Fall 2015 version                 | 58 |

| A.1  | Tentative, proposed, schedule for the SAGES course                    | 63 |

| B.1  | The Pick-n-Place file for automated component placement               | 74 |

# List of Figures

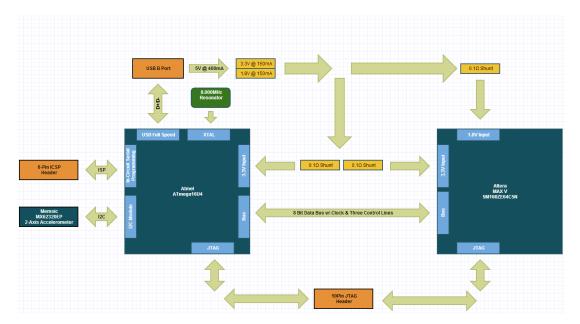

| 2.1 | The block diagram of the purpose-designed board                           | 7  |

|-----|---------------------------------------------------------------------------|----|

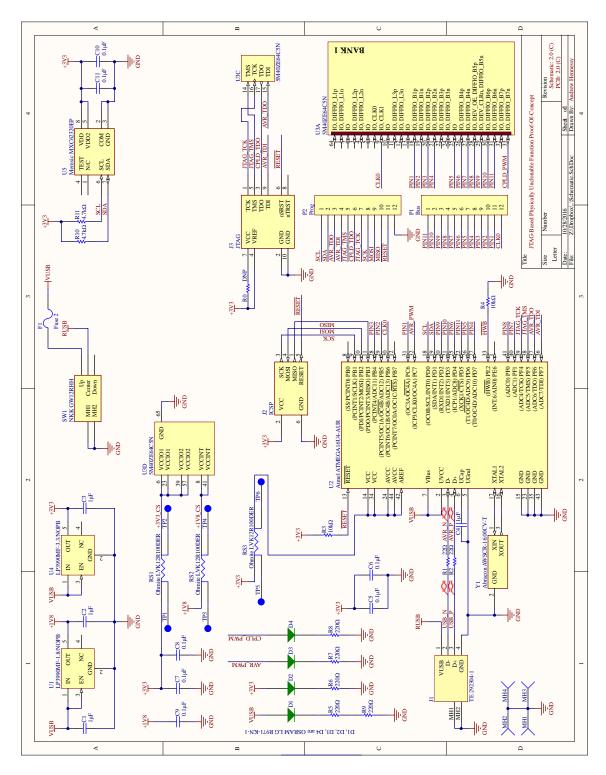

| 2.2 | The PCB layout of the purpose-designed board in Altium Designer           | 7  |

| 2.3 | The Arduino IDE when it is first opened                                   | 14 |

| 2.4 | The data the default application sends to the computer. $\ldots$ .        | 16 |

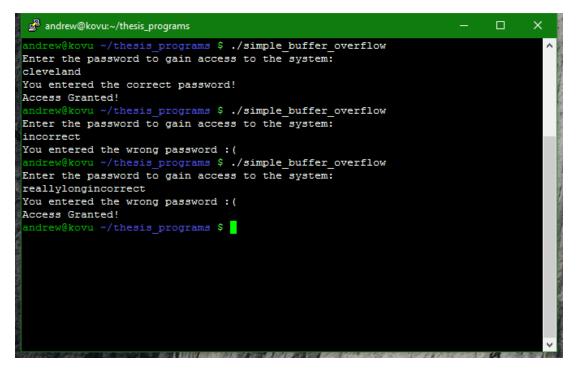

| 4.1 | The expected output of "simple_buffer_overflow.c"                         | 30 |

| 4.2 | The expected output of "pointer_buffer_overflow.c" $\ldots \ldots \ldots$ | 31 |

| 6.1 | The output of "aes_example.c" with three different length arguments.      | 38 |

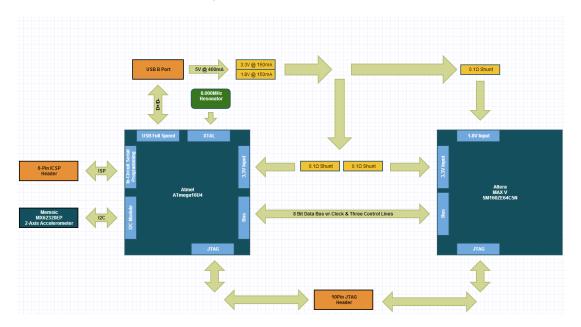

| 7.1 | Block diagram of the demo Printed Circuit Board (PCB)                     | 40 |

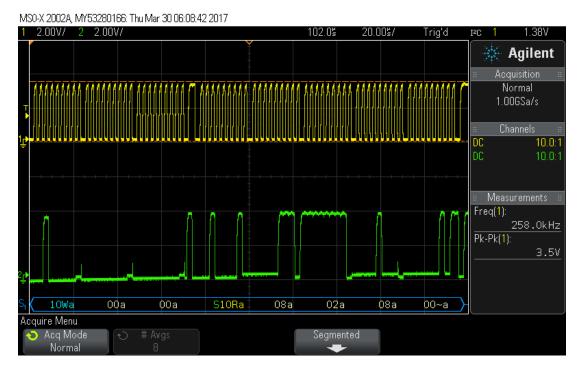

| 7.2 | The screen of an Agilent MSO 2002A configured to decode I2C data          |    |

|     | and to trigger on a I2C start bit. It should be noted that the measured   |    |

|     | frequency of Channel 1 is incorrect. The correct value is 400.0<br>kHz    | 43 |

| 8.1 | Block diagram of the demo Printed Circuit Board (PCB)                     | 46 |

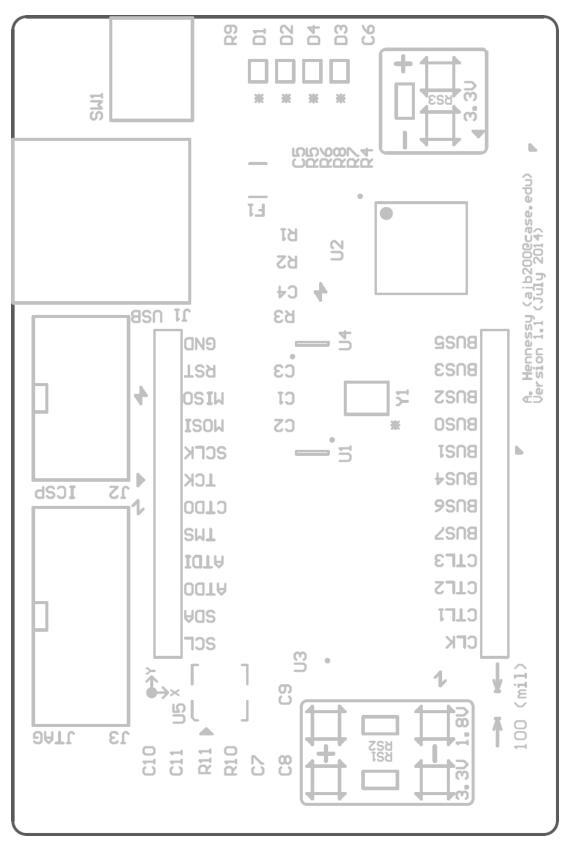

| B.1 | The schematic of the purpose-built board                                  | 67 |

| B.2 | The top silk screen graphic.                                              | 68 |

| B.3 | The top soldermask graphic.                                               | 69 |

| B.4 | The top copper graphic.                                                   | 70 |

| B.5 | The bottom copper graphic.                                                | 71 |

| B.6 | The bottom soldermask graphic                                             | 72 |

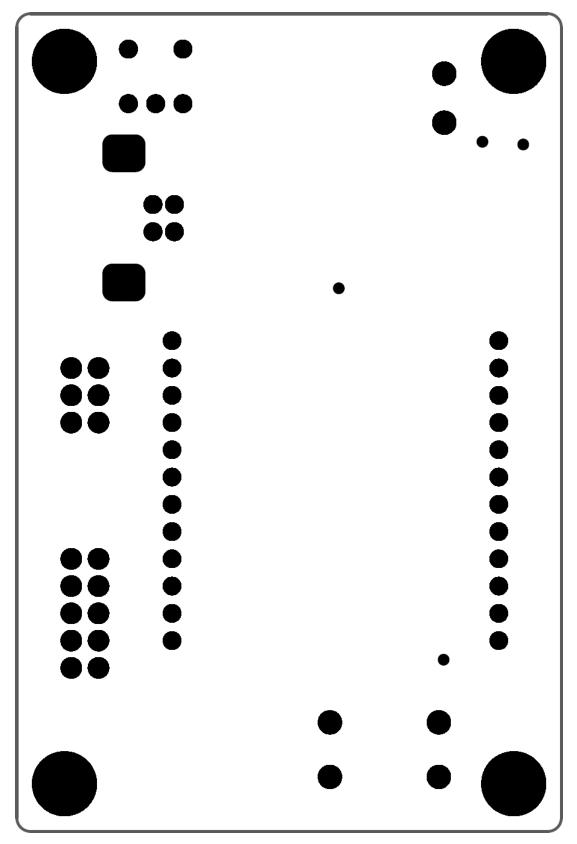

| B.7 The drill locations | 3 | 73 |

|-------------------------|---|----|

|-------------------------|---|----|

# Acknowledgments

The first person that requires acknowledgment is Dr. Kenneth Loparo, without whom this thesis would likely not exist. He was always willing to drop what he was doing and offer an open chair to listen to and assist with my issue *du jour* as well as offering a gentle nudge every once in a while to keep me on track. He also had enough faith in me to allow me to teach an untested course to twenty-five undergraduate students over two semesters. Secondly, without Dr. Francis Merat's seemingly unending knowledge of Case Western's bureaucracy and history I would have been stuck multiple times. Thirdly, Dr. Gregory Lee, whose guidance and experience enabled me to make my course better than it otherwise would have been.

Additionally, I would like to thank one of my cohorts over at Cleveland State University, Chirayu Shah, for providing the basis of two of the software-based assignments that I built upon.

I would also like to thank the innumerous people who let me bounce ideas off of their shoulders during the brainstorming sessions for this course. Without their open ears this course would have turned out very differently.

This material is based upon work supported by the National Science Foundation under Grants No. 1603480 and 1520306. Any opinions, findings, and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the National Science Foundation.

Finally, without my family's support and encouragement none of this would have

ever been possible.

#### A Hands-On Security Course

Abstract

#### by

#### ANDREW HENNESSY

In today's world almost every transaction, whether it's monetary or the exchange of information, passes through a computer system at some point it its journey. These transactions are secured using numerous forms of encryption to both protect the information as well as ensuring the integrity of the parties involved.

These security methods are currently taught in classrooms with chalkboards full of equations without a thought to how the methods are practically implemented, leaving students confused as to how these equations and concepts relate to the physical or virtual worlds

This thesis provides the basis of a laboratory course that enables students to easily learn about the modern implementations of security in a controlled environment using common tools such as a digital multimeter and an oscilloscope, providing both a theoretical and practical setting for student enrichment.

This course was piloted at Case Western Reserve and the student response was overwhelmingly positive.

# Chapter 1

# Introduction

Almost everything we do on a computer has to be secured in one fashion or another. Historically, communications between two parties were secured by a number of different methods, ranging from wax seals to padlocks and even to primitive cyphers. The direct analogy to physical security in the digital world is encryption. However, like wax seals — which can be opened without detection — and locks — which can be pried open — encryption can be defeated in a number of different ways. This thesis explores how encryption can be broken by attacking, "hacking," with two different approaches: attacking the implementation of the encryption in software and by attacking the hardware that the encryption algorithms run on.

As it stands now, encryption technologies and methods are rarely taught at the undergraduate level, with often only one or two courses offered at the graduate level. These courses are typically through the Mathematics Department instead of through an engineering department. These courses are usually taught at the theoretical level, ignoring and purposely leaving out implementation details. This leads to an oftrepeated adage that states, "one should never implement their own encryption system, they should let the professionals handle it." This statement, however, implicitly instructs users to treat an encryption algorithm as a black box, a statement which runs orthogonal to that of an educational institutions's philosophy.

## 1.1 Other Courses at Different Universities

While researching this class and creating the required coursework for students to preform, a small handful of other courses at different universities were discovered with the same goal as the course described in this thesis. It is difficult to find full details on these courses due to the increasing trend of courses being locked behind a password-protected Learning Management System, such as Blackboard, Moodle and Canvas.

One such course that was found, and not locked behind such a system, was CSCI: 4974 and 6964: Hardware Reverse Engineering taught during the Fall 2014 semester at the Rensselaer Polytechnic Institute (RPI) by Dr. Bülent Yener and his TA, Andrew Zonenberg[11].

Their course focused entirely on attacking the hardware that an encryption algorithm runs on and they were able to go more in-depth with equipment and methods such as decapping an Integrated Circuit (IC), as well as invasive attacks on hardware with tools such as a Focused Ion Beam (FIB) setup to modify IC's and Scanning Electron Microscope (SEM) to reverse engineer the schematics of an IC.

As it's title suggests, this course focuses entirely on the hardware of a system and how it can be attacked, with little regard to potential software vulnerabilities. In addition, while Case Western Reserve has a facility that owns a SEM and FIB machine, budgetary and course-sequence concerns precluded the use of these machines in the way that the RPI course used them. One of the design criteria for the course described in this thesis was that it should be available to the highest number of students possible and not have external prerequisite dependencies. The consequence of this decision is that the advanced labs that the RPI course was able to include, such as the aforementioned IC reverse engineering lab, could not be included in this course.

## 1.2 Organization of the Thesis

This thesis is divided into four broad parts. The first part contains the introductory material — this introduction, Chapter 1 — as well as Chapter 2, which discusses the equipment that is needed to do the experiments documented in this thesis.

The second part, Chapters 3–10 discuss in detail each of the six experiments that compose the course on Integrated Security. It starts with Chapter 3, which provides a sample syllabus for the class. Then, the chapters for the experiments are typically further subdivided into two sections. The first section is a short description of what the students are expected to have learned following the conclusion of the experiment. The other section in each chapter is the assignment that is given to the students to complete, along with any necessary support files. Solutions to questions that are asked in the assignment are provided, however several assignments ask students to write a program to accomplish the task. Due to the large variety of possible answers, solutions to programming exercises are not provided.

The next part, Chapter 11 discusses the feedback received by students when this course was offered twice, in the Fall of 2014 as well as the Fall of 2015 as well as changes that were made as a consequence of that feedback.

The last part of this thesis is comprised of a two appendices. The first appendix describes an alternate version of the course described in this thesis re-framed as a freshman English class. The second appendix contains all of the necessary technical documentation that is needed to construct more copies of the purpose built board that is described in Chapter 2.

# Chapter 2

# Laboratory Environment

One aspect that sets this curriculum apart from others in the field is that all of the experiments and laboratory exercises are done on an embedded device, as opposed to using either a desktop computer or what is unfortunately becoming the norm, having no hands-on labs at all. The advantages of this approach are numerous, students are able to interact with hardware in situations that they might not otherwise be able to as well as seeing how changes in the firmware affect the fundamental operation of the hardware.

The drawback of this approach is that a certain amount of initial capital investment is needed to teach this course. This course was designed around using a general purpose circuits laboratory without the need for specialized equipment outside of what is needed for an introductory sophomore-level circuits course. For example, at Case Western Reserve University sophomore engineering students take a course titled ENGR 210: Introduction to Circuits and Instrumentation to satisfy part of their engineering breadth requirement. This course has a mandatory weekly laboratory session in a purpose-build teaching laboratory, the Sears Undergraduate Circuits Lab, that has the following equipment:

• HP 33120A Function Generator

- HeTest 3005F Dual Rail Power Supply

- HP 34401A or Keithley 2000 Digital Multi Meter

- Agilent MSO 2002A Digital 2 Channel Mixed-Signal Oscilloscope

This is typical of the level of equipment that is available in most engineering schools.

## 2.1 Equipment and Tools Needed

For the described security-centric class this array of expensive test equipment is not necessarily needed. Since the security class is a predominantly digital class and not an analog design class, the function generator and the power supply are not needed. The digital multi meter is only needed for one experiment — the reverse engineering experiment — and a generic multimeter is all that is required.

Of the laboratory experiments elaborated on in later chapters only the experiments for snooping on a bus (Chapter 7) and reverse engineering (Chapter 8) require an oscilloscope. The rest of the experiments only require an embedded software development board, as discussed in the next section.

This course was designed to use a Keysight MSO 2002A oscilloscope, which is one step above the base model 2000 series oscilloscope. It has a bandwidth of 70 MHz, a maximum sample rate of 2 GS/s, a memory depth of one million points and two analog channels with eight digital channels, with a MSRP of \$2,059[15]. Additional to the oscilloscope itself the course is designed to take advantage of the segmented memory upgrade (\$307) as well as the  $I^2C$  and SPI hardware decoders (\$500). For an institution gearing up to offer an electronics lab for the first time, outfitting a number of workstations with oscilloscopes and PC's might not be possible for some budgets.

A less expensive alternative that has been verified to work with all of the assign-

ments is the Saleae Logic 8. This is a more basic option than a full-blown oscilloscope, yet it has all of the features needed for this class. The bandwidth of the Saleae is 25 MHz with a maximum sample rate of 100 MS/s and a memory depth that is solely based on the attached computer amount of RAM, since the Logic 8 has no display or storage of its own and entirely relies on an attached computer. The Logic 8 has eight dual-purpose digital or analog inputs and the device's software automatically handles the decoding of  $I^2C$  and SPI bus signals, all for a MSRP of \$219, not that much more than a modern collegiate level textbook (and in some cases less)[21]. It would be resaonable to require students to purchase their own pocket-sized oscilloscope for this class instead of requiring an actual laboratory oscilloscope.

## 2.2 Experimental Board

The majority of the hardware experiments for this course are designed to run on a development board with a cross-compilation environment set up on a computer. For this class, a Printed Circuit Board (PCB) has been custom-designed for ease-of-use and completeness. Alternatively, an off-the-shelf board, such as an Arduino Uno R3, can be used although not all experiments, as they currently exist, will be able to be completed on an off-the-shelf board.

#### 2.2.1 Purpose-Designed Board

Once the experiments were sketched out and preliminary designs were finished it became apparent that no currently existing off-the-shelf development board would be suited to the tasks necessary for this course. A new development board would have to be designed and manufactured.

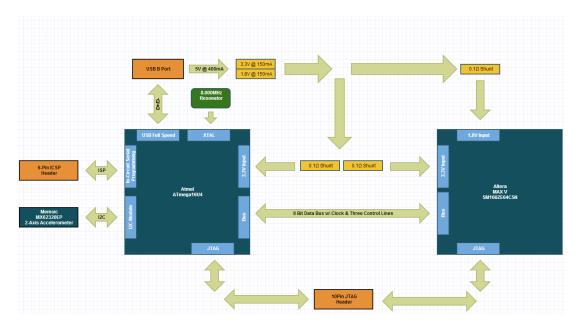

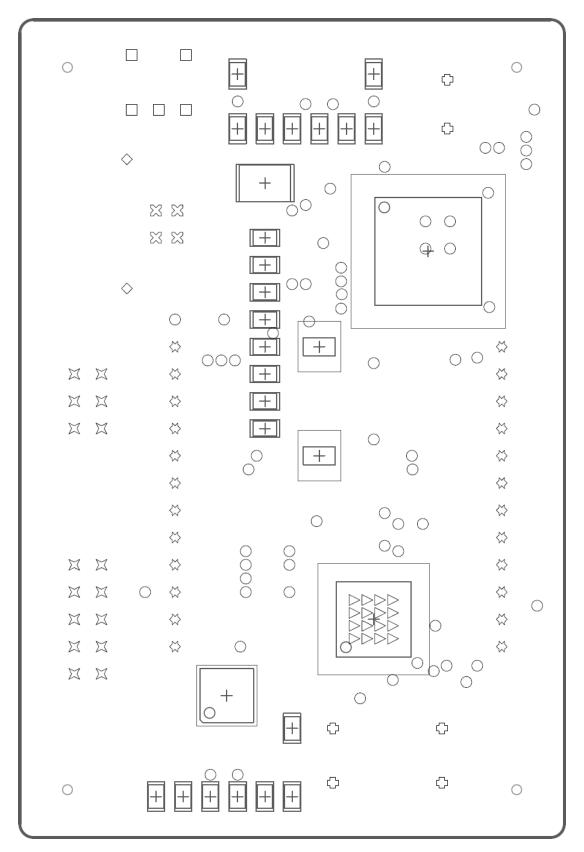

Figure 2.1: The block diagram of the purpose-designed board.

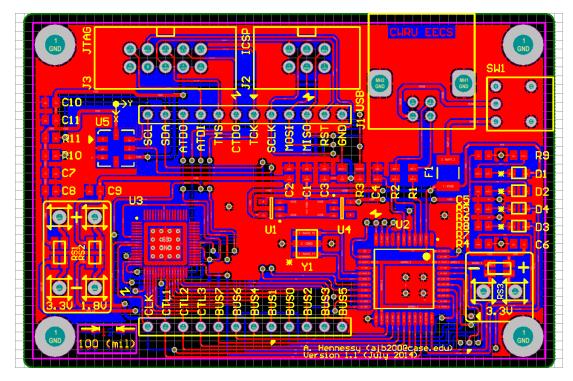

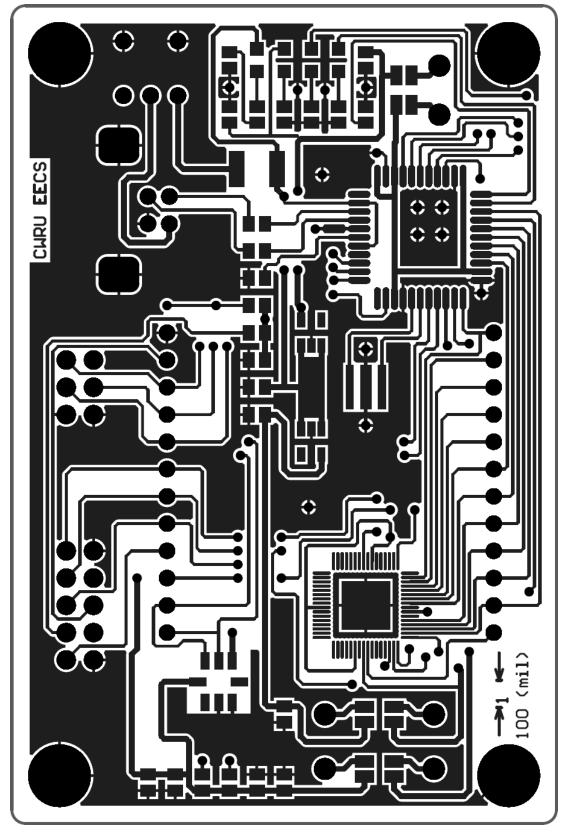

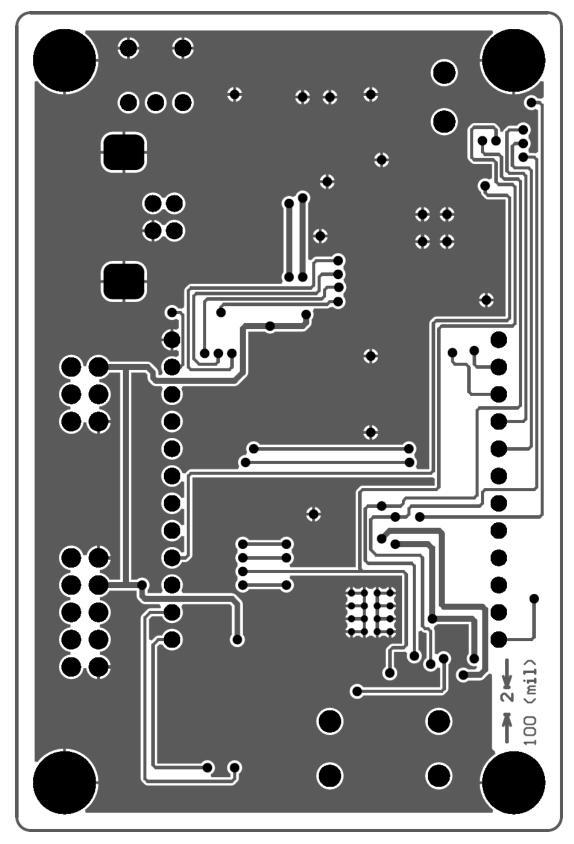

Figure 2.2: The PCB layout of the purpose-designed board in Altium Designer.

| C0805C105Z4VACTU           C0805C104Z4VACTU           LG R971-KN-1           C0805C104Z4VACTU           LG R971-KN-1           0ZCG0050AF2           KUSBXHT-BS1N-O-HRF           30306-6002HB           30310-6002HB           30310-6002HB           vity         9-146285-0-14           le         CRCW080522R0FKEA           le         CRCW080522R0FKEA           le         CRCW0805220RFKEA           le         CRCW0805220RFKEA           le         CRCW0805220RFKEA           le         CRCW0805220RFKEA           le         CRCW08054K70FKEA           le         LVK12R100DER           founts         LP3990MF-1.8/N0PB           founts         LP3990MF-3.3/N0PB           founts         LP3990MF-3.3/N0PB           MXC62320EP         MXC62320EP                                                                                                                                                                                                                                                           | RefDes                       | Manufacturer      | Model              | Description                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------|--------------------|--------------------------------------------|

| IKemetC0805C104Z4VACTUOSRAMLG R971-KN-1OSRAMLG R971-KN-1Del Fuse0ZCG0050AF2KyconKUSBXHT-BS1N-O-HRF3M30306-6002HB3M30310-6002HB3M30310-6002HB3M30310-6002HB3M30310-6002HBTE Connectivity9-146285-0-14Vishay DaleCRCW080522R0FKEAVishay DaleCRCW080522R0FKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW0805220RFKEAVishay DaleTexas InstrumentsLP3990MF-1.8/NOPBAtmelAtmel5M160ZE64C5NAtmeiTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | C1, C2, C3, C4               | Kemet             | C0805C105Z4VACTU   | Ceramic 0805 1uF Capacitor, Y5V, 16V       |

| OSRAMLG R971-KN-1Bel Fuse0ZCG0050AF2KyconKUSBXHT-BS1N-O-HRFXycon80306-6002HB3M30306-6002HB3M30310-6002HB3M30310-6002HB3M30310-6002HBTE Connectivity9-146285-0-14Vishay DaleCRCW080522R0FKEAVishay DaleCRCW080522R0FKEAVishay DaleCRCW080522R0FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEATexas InstrumentsLP3990MF-1.8/NOPBMemsicMXC62320EPMemsicMXC62320EPMemsicMXC62320EP                                                                                                                                                                                                                                                                                                                                                                                                                                                       | C5, C6, C7, C8, C9, C10, C11 | Kemet             | C0805C104Z4VACTU   | Ceramic 0805 0.11uF Capacitor, Y5V, 16V    |

| Bel Fuse $0ZCG0050AF2$ KyconKUSBXHT-BS1N-O-HRF $3M$ $30306-6002HB$ $3M$ $30306-6002HB$ $3M$ $30310-6002HB$ TE Connectivity $9-146285-0-14$ Vishay Dale $CRCW080522R0FKEA$ Vishay Dale $CRCW080522R0FKEA$ Vishay Dale $CRCW080522R0FKEA$ Vishay Dale $CRCW080522RFKEA$ Vishay Dale $CRCW080522RFKEA$ Vishay Dale $CRCW080522RFKEA$ Vishay Dale $CRCW08054K70FKEA$ NKK $CR12RHH$ Texas Instruments $LP3990MF-1.8/N0PB$ Atmel $5M160ZE64C5N$ Atmel $5M160ZE64C5N$ Memsic $MXC62330EP$ Memsic $MXC62330EP$                                                                                                                                                                                                                                                                                                                                                                                                                                         | D1, D2, D3, D4               | OSRAM             | LG R971-KN-1       | 0805 Green LED                             |

| KyconKUSBXHT-BS1N-O-HRF $3M$ $30306-6002HB$ $3M$ $30306-6002HB$ $3M$ $30310-6002HB$ $3M$ $30310-6002HB$ $TE$ Connectivity $9-146285-0-14$ $V$ ishay Dale $CRCW080522R0FKEA$ $V$ vishay Dale $CRCW080522RFKEA$ $V$ vishay Dale $CRCW080522RFKEA$ $V$ vishay Dale $CRCW0805220RFKEA$ $V$ vishay Dale $CRCW0805220RFKEA$ $V$ vishay Dale $CRCW08054K70FKEA$ $V$ vishay Dale $LVK12R100DER$ $V$ vishay Dale $CRCW08054K5A$ $V$ vishay Dale $LVK12R100DER$ <td< td=""><td>ГЧ</td><td>Bel Fuse</td><td>0ZCG0050AF2</td><td>500mA PTC Fuse</td></td<>    | ГЧ                           | Bel Fuse          | 0ZCG0050AF2        | 500mA PTC Fuse                             |

| 3M $30306-6002HB$ $3M$ $30310-6002HB$ $3M$ $30310-6002HB$ $TE$ Connectivity $9-146285-0-14$ $V$ ishay Dale $CRCW080522R0FKEA$ $V$ ishay Dale $CRCW080522RFKEA$ $V$ ishay Dale $CRCW0805220RFKEA$ $V$ ishay Dale $CRCW080524K70FKEA$ $V$ ishay Dale $LVK12R100DER$ <t< td=""><td>J1</td><td>Kycon</td><td>KUSBXHT-BS1N-O-HRF</td><td>USB Type B Plug</td></t<> | J1                           | Kycon             | KUSBXHT-BS1N-O-HRF | USB Type B Plug                            |

| 3M $30310-6002HB$ TE Connectivity $9-146285-0-14$ Vishay Dale $0.146285-0.14$ Vishay Dale $CRCW080522RFKEA$ Vishay Dale $CRCW080510K0FKEA$ Vishay Dale $CRCW0805220RFKEA$ Vishay Dale $CRCW08054K70FKEA$ NKK $CRCW08054K70FKEA$ Atmel $LP3990MF-1.8/NOPB$ Atmel $5M160ZE64C5N$ Atmera $5M160ZE64C5N$ Memsic $MXC62320EP$ Memsic $MXC62320EP$ Abracon $AWSCR-16.00CV-T$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | J2                           | 3M                | 30306-6002HB       | 2x3 0.1" Header (ISCP)                     |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | J3                           | 3M                | 30310-6002HB       | 2x5 0.1" Header (JTAG)                     |

| Vishay DaleCRCW080522R0FKEAVishay DaleCRCW080510K0FKEAVishay DaleCRCW080510K0FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEANKKCRCW08054K70FKEATexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAtmel5M160ZE64C5NAthera5M160ZE64C5NMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | P1, P2                       | TE Connectivity   | 9-146285-0-14      | 1x14 0.1" Header (Debug)                   |

| Vishay DaleCRCW080510K0FKEAVishay DaleCRCW0805220RFKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEANKKCW12R100DERNKKGW12R100DERTexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAtmel5M160ZE64C5NAhrea5M160ZE64C5NMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R1, R2                       | Vishay Dale       | CRCW080522R0FKEA   | 22 Ohm Resistor, 1/8W, 1%, 0805            |

| Vishay DaleCRCW0805220RFKEAVishay DaleCRCW08054K70FKEAVishay DaleCRCW08054K70FKEANKKLVK12R100DERNKKGW12RHHTexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAtmel5M160ZE64C5NAltera5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R3, R4                       | Vishay Dale       | CRCW080510K0FKEA   | 10  kOhm Resistor, 1/8W, 1%, 0805          |

| Vishay DaleCRCW08054K70FKEAOhmiteLVK12R100DERNKKGW12RHHTexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAtmel5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R5, R6, R7, R8, R9           | Vishay Dale       | CRCW0805220RFKEA   | 220 Ohm Resistor, 1/8W, 1%, 0805           |

| OhmiteLVK12R100DERNKKKUX12R1HHTexas InstrumentsCW12RHHTexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAtmel5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R10, R11                     | Vishay Dale       | CRCW08054K70FKEA   | 4.7 Ohm Resistor, 1/8W, 1%, 0805           |

| NKKGW12RHHTexas InstrumentsLP3990MF-1.8/NOPBAtmelATMEGA16U4-AURAltera5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | RS1, RS2, RS3                | Ohmite            | LVK12R100DER       | 0.1 Ohm Resistor, $1/2W$ , $0.5%$ , $1206$ |

| Texas InstrumentsLP3990MF-1.8/NOPBAtmelAtmelAtmelATMEGA16U4-AURAltera5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMensicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SW1                          | NKK               | GW12RHH            | SPDT Switch                                |

| AtmelAtmelATMEGA16U4-AURAltera5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U1                           | Texas Instruments | LP3990MF-1.8/NOPB  | 1.8V LDO Voltage Regulator                 |

| Altera5M160ZE64C5NTexas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U2                           | Atmel             | ATMEGA16U4-AUR     | 8-Bit Microcontroller                      |

| Texas InstrumentsLP3990MF-3.3/NOPBMemsicMXC62320EPAbraconAWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | U3                           | Altera            | 5M160ZE64C5N       | 160 Element CPLD                           |

| Memsic MXC62320EP<br>Abracon AWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U4                           | Texas Instruments | LP3990MF-3.3/NOPB  | 3.3V LDO Voltage Regulator                 |

| Abracon AWSCR-16.00CV-T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | U5                           | Memsic            | MXC62320EP         | 2 Axis Accelerometer                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Y1                           | Abracon           | AWSCR-16.00CV-T    | 16 MHz Resonator                           |

# Table 2.1: The Bill of Materials for the purpose-designed board.

## CHAPTER 2. LABORATORY ENVIRONMENT

#### Design of the Board

A block diagram of this board can be seen in Fig. 2.1. The overall architecture of the board includes a master microcontroller (MCU) which receives data from a sensor (an accelerometer in this case) and can perform off-chip Digital Signal Processing (DSP) on a Complex Programmable Logic Device (CPLD) that is attached to the MCU. This design was chosen to be as flexible as possible in order to emulate emerging Internet of Things (IoT) devices. The only element missing from this board is a means of wireless communication, although this can be added later by using the debugging extension headers.

A completed version of the purpose-designed board can be seen in Fig. 2.2. In the figure the layer colors are as follows: Red is Top Copper, Blue is bottom Copper, Yellow is Top Silkscreen and Green/Grey are Holes. The Bill of Materials for the board can be seen in Table 2.1.

The Atmel ATMEGA16U4 was chosen for this board. It is eight bit microcontroller that uses a modified Harvard architecture RISC core. That is to say user and program data are treated as the same by the core, which carries the designation 'AVR' by its manufacturer. The ATMEGA16U4 has 16 KB of flash available to store code as well as 1.25 KB SRAM to store program state during execution. The chip also has 512 bytes of Electrically Erasable Programmable Read-Only Memory, which while not used in any of the experiments for this course, is able to store data across a power cycle. The ATMEGA32U4 is a drop in replacement for the ATMEGA16U4 which doubles the amount of flash to 32 KB, the SRAM to 2.5 KB and the EEPROM to 1 KB. The ATMEGA16U4 was chosen for this board over the ATMEGA32U4 primarily due to availability restrictions on the ATMEGA32U4 when the PCB was sent out for fabrication and assembly, but also to save approximately 40% in parts cost[4].

The AVR Core is well supported by several different compilers and, as we will discuss later in this section, is the foundation for the popular Arduino software suite and development board. In fact, this board can easily emulate the popular Arduino Leonardo development board, which makes programming it by students even easier.

One standout feature of the Atmel ATMEGA16U4 is that it has integrated support for the Universal Serial Bus (USB) standard. The microcontroller supports creating a number of virtual USB endpoints, one of which can be used to emulate a standard serial port. If the ATMEGA16U4 did not support this feature, communication with a host computer would have to go through a more complex translation between the microcontroller's serial port and an external Integrated Circuit that supports translating between both standards.

The other half of this board, so to speak, is the CPLD. The CPLD that was chosen for this board was the Altera MAX V 5M160ZE64C5N. The 5M160ZE64C5N has a hundred and sixty Logic Elements that can be configured to emulate any basic hardware device, including basic DSP functions[2].

As mentioned previously, many embedded devices collect data with an array of sensors then process that data using a separate DSP chip, all controlled by a microcontroller. A standalone DSP chip was not chosen for this board primarily due to cost and complexity. The Altera 5M160ZE64C5N is \$3.51[7] in quantities and a simple DSP chip starts at \$30[10]. Furthermore, a standalone DSP chip requires multiple power rails and potentially off-chip DRAM and assorted other interfaces. Adding support for those would have exponentially increased the cost to manufacture and assemble this simple board. Furthermore, DSP software stacks are heinously complicated, not to mention expensive and proprietary, causing the core focus of this course — how hardware and software interact to learn about embedded security to become shifted towards labs in "how to set up the DSP software".

A similar rationale can be given for why a simpler CPLD was used instead of a more expensive, complex, and powerful Field Programmable Gate Array (FPGA). While a FPGA can be used for more extensive emulation of DSP tasks than a CPLD can, it carries drawbacks, such as increased power and physical space.

After this board went into production and before this thesis was written, Altera announced the MAX 10 FPGA series which does away with the complicated power trees that FPGAs are known for and replaces it with a single power supply rail[1]. A revision to this board could be made that replaces the MAX V CPLD in favor of the newer MAX 10 FPGA, leaving students able to implement more realistic emulation DSP filters.

One downside to using Altera products is the required expensive, external, programmer, which Altera trademarks as the USB-Blaster series. The official USB-Blaster is \$300[9], while licensed clones are \$50[8]. A counterfeit programmer can be had for \$3 on E-Bay[12], although using a known counterfeit device carries ethical concerns, which would be amplified by the irony of doing so in a security class. It is possible to license the USB-Blaster technology from Altera for a cost of \$5,000 per design[20], although in our case it would require an additional microcontroller and FPGA that are more powerful than the ones on our board, further driving up the cost of the board for the students.

The board has programming connections for both Atmel's In-Circuit Serial Programming (ICSP) interface (Connector J2 in Fig. 2.2) as well as the standard Joint Test Action Group IEEE 1149.1 testing and debug interface (Connector J3 in Fig. 2.2). The Atmel ATMEGA16U4 can be programed by both interfaces but the Altera 5M160ZE64C5N can only be programmed through the JTAG interface. The JTAG chain in this board is set so that the first device on the chain is the microcontroller than the second and final device on the chain is the CPLD.

To provide feedback to the user visually there are four green LEDs situated on the right-hand side of the board, as can be seen in Fig. 2.2. The top-most LED, D1, lights up any time that there is 5 Volts applied to the USB socket. The second LED down, D2, is illuminated whenever the power switch (SW1) is turned on and the voltage regulators are providing 3.3V for the rest of the board. The next LED in the stack, D4, is connected to the CPLD to provide user-configurable notification. The final LED, D3, is connected to the microcontroller to serve a similar purpose. By default the two programmable LEDs are designed to light up whenever there is motion in the X- or Y-direction, as sensed by the accelerometer.

The Memsic MXC62320EP accelerometer was chosen for several different reasons. One of the biggest reasons is that the  $I^2C$  communication protocol to read the sensor's data is extremely simple — there are not dozens of registers that need to be precisely programmed to ensure proper operation. This chip simply outputs the current acceleration on two axes when asked[17]. This makes the assignments for bus snooping (Chapter 7) and reverse engineering (Chapter 8) simpler than they would otherwise be while still teaching students valuable lessons. Secondly the physical package of the device is big enough and the pin spacing is large enough not to require special (i.e. expensive) handling for automated assembly. An additional benefit is that the PCB can be finished in a cheaper HASL (Hot Air Solder Leveling) instead of more expensive process, such as ENIG (Electroless Nickel Immersion Gold), which would have been needed if an accelerometer in a QFN package was selected.

One note is that between the production of this board several years ago and the writing of this thesis is that the Memsic MXC62320EP has been discontinued in favor of a replacement that has a higher range and a lower noise floor[18]. Physically and electrically the newer version appears to be a drop in replacement so future revisions of the board could easily switch to the newer product.

The PCB was designed to be as small as possible to minimize manufacturing costs. The end result is a two-layer PCB that is 3" wide and 2" tall with components only on the top. Passive components, such as resistors and capacitors, were arranged in long lines all facing the same direction to make potential hand assembly faster, easier, and the potential for mistakes less. For such a simple design two layers is all that is needed. A four layer board, adding in a layer for ground and a layer for the power supply, would be completely unnecessary. Additionally, having two layers helps make the reverse engineering assignment (Chapter 8) not a cruelly complicated endeavor. The most difficult to solder package on the board is the Altera 5M160ZE64C5N CPLD which has a pin pitch of 0.4 mm and an exposed pad on the bottom of the device. To solder this package either a reflow oven would need to be used or a hole could be placed to allow a soldering iron to access the exposed pad.

To keep the board from potentially shorting out on a table top four ANSI 4-40 holes were put on the extreme corners of the board to attach metal standoffs that elevate the board off of the surface it is resting on. The holes (and thus standoffs) are grounded to allow the board to be easily grounded, potentially alleviating any Electrostatic Discharge (ESD) issues.

The board was designed to allow easy access to all signals, for both the reverse engineering assignment (Chapter 8) and the bus snooping assignment (Chapter 7). To that end every signal between the microcontroller, the CPLD, the accelerometer as well as both of the programming interfaces were broken out to two standard 0.1" pitch headers for easy connection to an oscilloscope or logic analyzer.

The final feature of this board was put in for a homework assignment that ended up not being implemented in this course. Three 0.1  $\Omega$  sense resistors are located in series with the supply lines for the microcontroller and both of the CPLD's power rails. These resistors are located after any bulk bypass capacitance and as such can be used to perform dynamic power analysis on the microcontroller and CPLD. Software Development Experience

Figure 2.3: The Arduino IDE when it is first opened.

As mentioned previously the purpose-built board by default can easily emulate an Arduino Leonardo and is indistinguishable from other Arduinos to the Arduino IDE. When the board is plugged into a computer the USB-to-Serial Port drivers install automatically and transparently for recent versions of Windows and the board can then be programmed through the Arduino IDE to accomplish the end goal of the user.

One note is that the Arduino Leonardo does not use the pin numbering that the purpose-built board uses. Table 2.2 serves as a map between the two pin numbering schemes as well as the name of the pins that the ATMEGA16U4 uses internally.

There is an eleven bit bidirectional bus that connects the microcontroller to the CPLD along with a dedicated clock line. The bus was designed to allow for an eight bit data bus as well as three out-of-band general purpose signaling lines. The clock line is attached to one of the microcontroller's Pulse Width Modulation (PWM)

| ATMEGA16U4 | Arduino                   | Custom Board              |

|------------|---------------------------|---------------------------|

| PB4        | Pin # 8                   | Pin # 3                   |

| PB5        | Pin # 9                   | Pin # 2                   |

| PB6        | $Pin \ \# \ 10$           | Pin # CLK                 |

| PC6        | Pin # 11                  | Pin # 1                   |

| N/A        | N/A                       | CPLD_LED                  |

| PC7        | $Pin \ \# \ 13$           | AVR_LED                   |

| PD0        | $\operatorname{Pin} \# 3$ | $I^2C$ SCL                |

| PD1        | $\operatorname{Pin} \# 2$ | $I^2C$ SDA                |

| PD2        | Pin # 0                   | Pin # 9                   |

| PD3        | Pin # 1                   | Pin # 10                  |

| PD4        | Pin # 4                   | Pin # 6                   |

| PD5        | TXLED                     | Pin # 11                  |

| PD6        | $Pin \ \# \ 12$           | Pin # 5                   |

| PD7        | Pin # 6                   | Pin # 4                   |

| PF0        | $Pin \ \# \ A5$           | Pin # 8                   |

| PF1        | Pin # A4                  | $\operatorname{Pin} \# 7$ |

Table 2.2: Pin Mapping between the Custom Board, the Arduino Leonardo and the native pin names.

outputs, which allows for an easy adjustable clock frequency for the CPLD.

One of the aforementioned disadvantages is that the Altera 5M160ZE64C5N CPLD does not have a plug-and-play programming experience. A separate external programming adapter is required, although once attached the programmer has no issues programming the CPLD with the user's custom application like any other FPGA or CPLD programmed through Altera's Quartus II software. Table 2.3 serves as a guide for which pins on the microcontroller are connected to which pins on the CPLD.

#### **Default Application**

For the laboratory experiments in this course, with special regard to the bus snooping (Chapter 7) assignment, a default application is run on the custom board.

This default application performs the following actions in a loop:

- 1. Query the accelerometer for the current X- and Y-axis acceleration.

- 2. Send the data to the CPLD to be filtered through a FIR filter.

| ATMEGA16U4 | Custom Board   | CPLD Bank | CPLD Pin Number |

|------------|----------------|-----------|-----------------|

| PB4        | Pin # 3        | 1         | 20              |

| PB5        | Pin # 2        | 1         | 19              |

| PB6        | Pin # CLK      | 1         | 9               |

| PC6        | Pin # 1        | 1         | 18              |

| N/A        | CPLD_LED       | 1         | 33              |

| PC7        | AVR_LED        | N/A       | N/A             |

| PD0        | $I^2C$ SCL     | N/A       | N/A             |

| PD1        | $I^2C$ SDA     | N/A       | N/A             |

| PD2        | Pin # 9        | 1         | 29              |

| PD3        | Pin # 10       | 1         | 30              |

| PD4        | Pin # 6        | 1         | 26              |

| PD5        | Pin # 11       | 1         | 31              |

| PD6        | $Pin \ \# \ 5$ | 1         | 25              |

| PD7        | Pin # 4        | 1         | 27              |

| PF0        | Pin # 8        | 1         | 28              |

| PF1        | Pin # 7        | 1         | 27              |

Table 2.3: Pin Mapping between the Custom Board and the native pin names for the CPLD and microcontroller.

| ď  | COM3 - PuTTY |             |           |      |         |   |               |        | _            |       | × |   |

|----|--------------|-------------|-----------|------|---------|---|---------------|--------|--------------|-------|---|---|

| х: | (0x7EF> 0x7  | E (126)) 0x | 90 (144); | ; Y: | (0x831  | > | 0 <b>x</b> 83 | (131)) | 0x91         | (145) | - | ^ |

| х: | (0x7E5> 0x7  | E (126)) 0x | 85 (133); | ; Y: | (0x81E  | > | 0x81          | (129)) | 0x91         | (145) |   |   |

| х: | (0x8B5> 0x8  | B (139)) 0x | 80 (128); | ; Y: | (0x839  | > | 0 <b>x</b> 83 | (131)) | 0x8D         | (141) |   |   |

| х: | (0x906> 0x9  | 0 (144)) Ox | 7D (125); | ; Y: | (0x83E  | > | 0x83          | (131)) | 0x86         | (134) |   |   |

| х: | (0x970> 0x9  | 7 (151)) Ox | 84 (132); | ; Y: | (0x815  | > | 0x81          | (129)) | 0x82         | (130) |   |   |

| х: | (0x7FD> 0x7  | F (127)) 0x | 8C (140); | ; Y: | (0x895  | > | 0x89          | (137)) | <b>0x84</b>  | (132) |   |   |

| х: | (0x8EF> 0x8  | E (142)) 0x | 8D (141); | ; Y: | (0x7C9  | > | <b>0x7</b> C  | (124)) | 0x86         | (134) |   |   |

| х: | (0x930> 0x9  | 3 (147)) Ox | 8D (141); | : Y: | (0x936  | > | 0x93          | (147)) | 0x82         | (130) |   |   |

| Х: | (0x8FB> 0x8  | F (143)) Ox | 8F (143); | ; Y: | (0x89A) | > | 0x89          | (137)) | <b>0x88</b>  | (136) |   |   |

| х: | (0x9C1> 0x9  | C (156)) 0x | 8B (139); | : Y: | (0x88F  | > | 88x0          | (136)) | <b>0x88</b>  | (136) |   |   |

| Х: | (0x8B9> 0x8  | B (139)) Ox | 92 (146); | ; Y: | (0x78E  | > | 0x78          | (120)) | <b>0x87</b>  | (135) |   |   |

| х: | (0x9CB> 0x9  | C (156)) 0x | 94 (148); | : Y: | (0x7E3  | > | 0x7E          | (126)) | 0x89         | (137) |   |   |

| х: | (0x904> 0x9  | 0 (144)) Ox | 90 (144); | ; Y: | (0xB0C  | > | 0xB0          | (176)) | 0x7F         | (127) |   |   |

| Х: | (0x8C0> 0x8  | C (140)) 0x | 94 (148); | ; Y: | (0x901  | > | 0x90          | (144)) | 0x89         | (137) |   |   |

| х: | (0x8F3> 0x8  | F (143)) 0x | 91 (145); | ; Y: | (0x7B8  | > | 0x7B          | (123)) | 0x8E         | (142) |   |   |

| Х: | (0x9BB> 0x9  | B (155)) 0x | 91 (145); | ; Y: | (0x5D1  | > | 0x5D          | (093)) | 0x8E         | (142) |   |   |

| Х: | (0xA25> 0xA  | 2 (162)) Ox | 92 (146); | ; Y: | (0xBC5  | > | 0xBC          | (188)) | 0x89         | (137) |   |   |

| Х: | (0x90F> 0x9  | 0 (144)) Ox | 93 (147); | ; Y: | (0x89A) | > | 0x89          | (137)) | 0x8B         | (139) |   |   |

| х: | (0xAB2> 0xA  | B (171)) 0x | 96 (150); | ; Y: | (0x844  | > | 0x84          | (132)) | 0x85         | (133) |   |   |

| Х: | (0x733> 0x7  | 3 (115)) Ox | 9C (156); | : Y: | (0x7F1  | > | 0x7F          | (127)) | <b>0x8</b> A | (138) |   |   |

| х: | (0x86F> 0x8  | 6 (134)) Ox | 95 (149); | ; Y: | (0x9B9  | > | 0x9B          | (155)) | 0x91         | (145) |   |   |

| Х: | (0x828> 0x8  | 2 (130)) Ox | 8D (141); | : Y: | (0x77E  | > | 0x77          | (119)) | 0x89         | (137) |   |   |

| х: | (0x88A> 0x8  | 8 (136)) Ox | 88 (136); | : Y: | (0x88D) | > | 88 <b>x</b> 0 | (136)) | 0x86         | (134) |   |   |

|    |              |             |           |      |         |   |               |        |              |       |   | ¥ |

Figure 2.4: The data the default application sends to the computer.

- 3. Read back the filtered data from the CPLD.

- 4. Send the filtered accelerometer data to the attached PC.

The data that the application sends to the computer can be seen in Fig. 2.4. This application enumerates as a generic USB Serial Port to the computer. A connection can be made to it with the following settings: 9600 baud, 8 Data Bits, No Parity and 1 Stop Bit.

The format that the data is sent is in the following format:

- X: (0x88A --> 0x88 (136)) 0x88 (136);

- Y: (0x88D --> 0x88 (136)) 0x86 (134)

Both the X- and Y-axis have three hexadecimal output values per iteration. The first value is the raw, unsigned twelve bit output from the accelerometer. The second value is the first value converted to an eight bit unsigned value, simply by throwing away the four least significant bits. In this example, for the X axis the raw value is **0x88A** and the truncated value is **0x88**. The final value for each axis is the result after the CPLD applied its algorithm. For ease of reading, the truncated and filtered values are repeated in decimal after the hexadecimal value is displayed.

The CPLD smooths the data coming from the accelerometer using a FIR filter, where y(n) is the output, x(n) is the current input and  $x(n - \{1, 2, 3\})$  are the three most recent inputs to the CPLD:

$$y(n) = \frac{x(n) + x(n-1) + x(n-2) + x(n-3))}{4}$$

(2.1)

This application ensures that there is always activity between the microcontroller, the CPLD, the accelerometer and the serial port.

#### Revisions

If this board were to go through another revision while still keeping things basic (i.e. not upgrading to a MAX 10 FPGA), several things would be changed. As discussed previously, the accelerometer would be updated to the newer model.

The two rows of 0.1" headers allow easy access to every signal on the board except for the two power rails. This mistake would be rectified by changing the two twelve pin headers into two thirteen pin headers, with the 1.8V rail going to one header and the 3.3V rail going to the other header.

The ICSP header would be removed to save space and money as it is not strictly necessary. The JTAG header provides a programming interface for both ICs.

The 0.1  $\Omega$  sense resistors would be increased to a value of 0.5  $\Omega$  or even 1  $\Omega$ , as the current draw of the board was lower than expected, causing their voltage drop to be barely noticeable on an oscilloscope.

Finally, the ATMEGA16U4 would be replaced with the ATMEGA32U4 and the main resonator would be replaced with an 8 MHz model from the same line. Both items would be done to enhance compatibility and interchangeability with that of other Arduino models.

#### 2.2.2 Off-the-shelf Boards

This course is designed to use the purpose-built board. However, with some care and modification of the assignments an off-the-shelf development board, such as the Arduino Uno R3, can be used.

The Arduino Uno R3 lacks the co-processor in the form of the CPLD and it lacks the integrated sensor, the accelerometer. A variety of sensors can be easily added in the form of 'shields', daughter boards that easily plug in to the expansion headers on the Uno. It would be possible to make a shield that contains a CPLD (or a FPGA).

Such a shield would be just as big as the purpose-built board, if not bulkier, with

insignificant cost-savings.

# Chapter 3

# **Syllabus**

# 3.1 Prerequisites

EECS 281: Digital Logic Design is recommended but not required

# 3.2 Credit Hours

This course is three credit hours.

# 3.3 Course Description

This course focuses on the hands-on learning of computer hardware security. The course will follow a distinctive hands-on teaching approach using a well-designed set of experiments as the learning tool. Students will be able to "hack" a system at different levels and analyze existing countermeasures.

# **3.4** Key Concepts

Introduction to comprehensive coverage on security issues — information, network, software, and hardware security. Understand information security through data encryption and decryption to protect data and systems. Learn buffer overflow attacks: stack overflow, heap overflow, and array indexing errors. Learn bus snooping attacks and protection schemes through different kinds of encryption. Be able to reverse engineer a closed system to figure out how the hardware components functions.

## 3.5 Course Requirements

There is no required textbook. The following books serve as a useful, but optional, references for concepts explored in this course:

- Erickson, Jon. "Hacking: The Art of Exploitation." No Starch Press, San Francisco, 2008. ISBN: 978-1593271442.[14]

- Huang, Andrew. "Hacking the Xbox: An Introduction to Reverse Engineering." No Starch Press, San Francisco, 2008. ISBN: 1-59327-029-1[3].

- Petzold, Charles. "Code: The Hidden Language of Computer Hardware and Software." Microsoft Press, Redmond, 2000. ISBN: 0-7356-1131-9[5].

## **3.6** Student Expectations

The following criteria are essential for your success in this course.