# THE DEVELOPMENT OF AN INTEGRATED BATTERY MANAGEMENT SYSTEM AND CHARGER

A Thesis

Presented to

The Graduate Faculty of the University of Akron

In Partial Fulfillment

of the Requirements for the Degree

Master of Science

Thomas V. Vo

August, 2014

# THE DEVELOPMENT OF AN INTEGRATED BATTERY MANAGEMENT SYSTEM AND CHARGER

Thomas V. Vo

Thesis

Approved

Accepted

Advisor Dr. Tom T. Hartley Department Chair Dr. Abbas Omar

Committee Member Dr. Seungdeog Choi Dean of the College Dr. George K. Haritos

Committee Member Dr. Yilmaz Sozer Dean of the Graduate School Dr. George R. Newkome

Date

## ABSTRACT

An investigation into battery management for lithium-based battery packs was performed. Out of the investigation of the various management/balancing methodologies came a proposed management methodology that is integrated with a charging system and utilizes cost-effective, lossy, bypass resistors for cell balancing. This integration allows the management system to cater the charging current to the needs of the battery pack and overcome the limitations of the lossy bypass on its own. To first investigate this concept, a LiFePO<sub>4</sub> cell model was obtained. This was done using a cell discharging procedure and characterization process that provides a mathematical first-principles cell model. The obtained model was then used to simulate various pack configurations, battery management configurations, including the proposed management method. The results from these simulations demonstrated that the proposed management methodology balanced cell voltages within a battery pack in as little as a single charge cycle. To confirm this concept a manually hand-controlled experiment, consisting of voltmeter monitoring cell voltages, manual activation of lossy bypass resistors, and manual adjustments of charging current, was performed. The results from this experiment confirmed the ability to balance the cell voltages within a single cycle. Hardware and software was developed to automate the proposed management methodology. Data collected from the automated implementation was in agreement with the performed simulations and successfully demonstrated a functional automated version of the proposed integrated battery management system and charger.

#### ACKNOWLEDGMENTS

I would like to thank my advisor Dr. Tom T. Hartley for sharing his methods, knowledge, his patience, and believing in me. Graduate school and life in general for that matter, is a non-linear system, hard to model and even harder yet to control. I'm grateful for having such a great role model during my undergraduate and graduate years to help optimize my output from this system.

Thanks to Matt Taschner for helping me along the journey as well. We learned, developed, discussed many things together and the experience would not have been the same without him. He pushed through getting his thesis done and was an inspiration for me to do the same.

A big thanks goes out to Erik Rinaldo for all of the practical knowledge he passed on in an endless number of projects/tasks he always was willing to help me with. Thanks to both Erik Rinaldo and Greg Lewis for the support in ordering the endless amount of items we had purchased for all research purposes. Also a huge thanks goes out to Gay Boden for helping me push through the massive amount of logistics, forms, and paperwork to be able to complete my thesis and work.

Last and not least, I would like to thank my family and friends for their unending support as I pursue my interests. Without a great support network this whole process would

have been all the more challenging on my own. No matter the contribution, large or small, thank you all for your kind words of support and help.

# TABLE OF CONTENTS

| Page                                                  |

|-------------------------------------------------------|

| LIST OF FIGURES                                       |

| LIST OF TABLES                                        |

| CHAPTER                                               |

| I. INTRODUCTION                                       |

| 1.1 Types of Cell Combinations (Battery Packs)        |

| 1.1.1 Series-Connected Cells                          |

| 1.1.2 Parallel-Connected Cells                        |

| 1.1.3 Series and Parallel Connected Cells 4           |

| 1.2 Goals of Research                                 |

| 1.3 Thesis Outline                                    |

| II. BACKGROUND AND RELATED WORK7                      |

| 2.1 The History of Electrochemical Cells7             |

| 2.2 Electrochemical cells                             |

| 2.3 Cell Chemistries                                  |

| 2.3.1 Lead-Acid                                       |

| 2.3.2 Nickel-Cadmium                                  |

| 2.3.3 Nickel-Metal Hydride                            |

| 2.3.4 Lithium Based Chemistries                       |

| 2.3.4.1 Lithium Cobalt Oxide (LiCoO <sub>2</sub> )14  |

| 2.3.4.2 Lithium Manganese Oxide (LiMnO <sub>2</sub> ) |

| 2.3.4.3 Lithium Iron Phosphate (LiFePO <sub>4</sub> )               | 15 |

|---------------------------------------------------------------------|----|

| 2.3.4.4 Lithium-Titanate (Li <sub>2</sub> TiO <sub>3</sub> )        | 15 |

| 2.4 Charging                                                        | 15 |

| 2.4.1 Lithium-based Battery Charging                                | 16 |

| 2.4.2 Floating/Trickle Charging                                     | 17 |

| 2.4.3 Lithium Ion Battery Discharging                               | 18 |

| 2.5 Need for Cell Balancing and Battery Management                  | 19 |

| 2.6 Cell Balancing Methods Summary                                  | 21 |

| 2.6.1 Passive Balancing                                             | 21 |

| 2.6.2 Active Balancing                                              | 23 |

| 2.7 A Proposed Integrated Charger and Battery Management System     | 26 |

| 2.8 Summary                                                         | 30 |

| III. BATTERY CELL MODELING                                          | 31 |

| 3.1 Introduction                                                    | 31 |

| 3.2 Battery Modeling                                                | 33 |

| 3.3 Procedure for Data Collection                                   | 39 |

| 3.4 Processing Collected Data                                       | 41 |

| 3.5 Obtained Cell Model Parameters                                  | 45 |

| 3.6 Cell Model Output and Equivalent Circuit Diagram for Cell Model | 46 |

| 3.7 Summary                                                         | 48 |

| IV. CELL MODEL SIMULATIONS                                          | 49 |

| 4.1 Simulations of a 3-Cell Series Connected Battery Pack           | 49 |

| 4.1.1 Battery Pack without Passive Bypass                           | 51 |

| 4.1.2 Battery Pack with Passive Bypass                              | 55 |

| 4.2 Simulations of 10-Cell Pack                                      | . 57 |

|----------------------------------------------------------------------|------|

| 4.2.1 Simulation with Non-Integrated Charger and without any BMS     | . 57 |

| 4.2.2 Simulation with 2A Fixed Bypass and Non-Integrated Charger     | . 60 |

| 4.2.3 Simulation with BMS and Integrated Charger                     | . 64 |

| 4.3 Summary                                                          | . 67 |

| V. HARDWARE FOR BMS IMPLEMENTATION                                   | . 68 |

| 5.1 Overview of Hardware for Integrated Charger and BMS              | . 69 |

| 5.1.1 Hardware for Individual Cell Management Unit (ICMU)            | . 70 |

| 5.1.2 PCB Connection                                                 | . 71 |

| 5.1.3 ICMU Power Circuitry                                           | . 74 |

| 5.1.4 ICMU Microcontroller                                           | . 76 |

| 5.1.5 Implementation of Voltage and Current Monitoring               | . 77 |

| 5.1.6 Implementation of Current Bypass Circuit                       | . 79 |

| 5.1.7 Implementation of Cell Temperature Monitoring                  | . 82 |

| 5.1.8 Implementation of LED displays for Status Indication           | . 83 |

| 5.1.9 Implementation of Communication Circuits between BPMU and ICMU | . 86 |

| 5.1.10 Implementation of ICMU Address Hardware Identification        | . 88 |

| 5.1.11 Hardware for BPMU/ICMU Hybrid                                 | . 89 |

| VI. SOFTWARE FOR BMS IMPLEMENTATION                                  | . 91 |

| 6.1 ICMU Software Overview                                           | . 91 |

| 6.1.1 Analog Voltage Reading                                         | . 91 |

| 6.1.2 Read, Filter, Convert, and Process Analog Readings             | . 92 |

| 6.1.3 Run Control Loop for Bypass Current                            | . 92 |

| 6.1.4 Package ICMU's Data into a Communication Packet for BPMU       | . 94 |

| 6.1.5 Update Status LEDs                                                      |

|-------------------------------------------------------------------------------|

| 6.2 ICMU Interrupts                                                           |

| 6.2.1 I2C Interrupt                                                           |

| 6.2.2 Timer Interrupt                                                         |

| 6.2.3 ADC Interrupt                                                           |

| 6.3 BPMU/ICMU Hybrid Software Overview                                        |

| 6.3.1 Process ICMU Data Packets, Convert and Print out                        |

| 6.3.2 Determine Cell Status and Take Corrective Action as Necessary           |

| 6.3.3 Implementation of I2C Communication Scheme 100                          |

| 6.3.4 Implementation of Charger Control Interface 100                         |

| VII. SIMULATION VALIDATION AND RESULTS 104                                    |

| 7.1 Discharge and Charge Cycles Results from a 4-cell Battery 104             |

| 7.2 Results from the Integrated Charger and BMS on a 10-Cell Battery Pack 100 |

| 7.2.1 Discharge Cycle                                                         |

| 7.2.2 Charge Cycle                                                            |

| 7.3 Chapter Summary 113                                                       |

| VIII. CONCLUSIONS                                                             |

| BIBLIOGRAPHY118                                                               |

| APPENDICES                                                                    |

| APPENDIX A: MATLAB CODE FOR SIMULATIONS 122                                   |

| APPENDIX B: ICMU CODE148                                                      |

| APPENDIX C: ICMU/BPMU Hybrid Code                                             |

## LIST OF FIGURES

| Figure Page                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1 Electrochemical Cell pictured during charge process and electrons and ion travel paths                                                                                                                   |

| 2.2 Electrochemical Cell pictured during discharge process and electrons and ion travel paths                                                                                                                |

| <ul> <li>2.3 Ragone plot comparing several types of cell chemistries and other energy storage devices (Kalhammer, 2007).</li> </ul>                                                                          |

| <ul> <li>2.4 A CC/CV charger first applies constant current rate until the battery reaches a set-point voltage, charging current is then reduced to maintain the set-point voltage (Simpson, 2011)</li></ul> |

| 2.5 Initial capacity of LiCoO2 cells before and after 300 cycles at varying discharge currents. The capacity fade increases with higher c-rates (Ning et al, 2003)                                           |

| 2.6 Passive Resistive Bypass (Moore, 2009)                                                                                                                                                                   |

| 2.7 Capacitor-Based Shuttle (Yevgen, 2009)                                                                                                                                                                   |

| 2.8 Shuttle circuit with remote cells connection capability (Yevgen, 2009)25                                                                                                                                 |

| 2.9 Inductive converter cell balancing circuit (Moore, 2001)                                                                                                                                                 |

| 2.10 High Level Block Diagram for Integrated BMS and Charger System                                                                                                                                          |

| 2.11 Detailed block diagram for Individual Cell Manager Unit within BMS                                                                                                                                      |

| 2.12 Detailed block diagram for Battery Pack Manager Unit within BMS                                                                                                                                         |

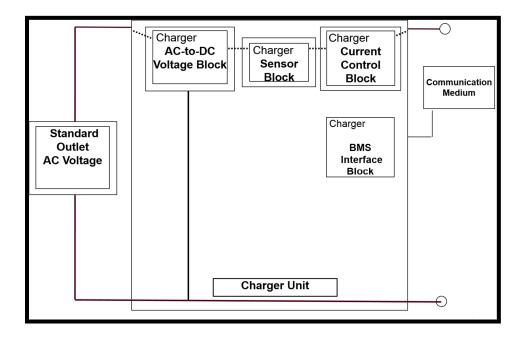

| 2.13 Detailed block diagram for Charger for integrated BMS concept                                                                                                                                           |

| 3.1 Measured Battery Voltage for full cell discharge cycle                                                                                                                                                   |

| 3.2 Control block diagram of open-loop cell model                                                                                                                                                            |

| 3.3  | Control block diagram of closed-loop cell model with observer                                                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.4  | Diagram of circuit used to collect cell discharge data                                                                                                                |

| 3.5  | Graph of collected discharge data (time axis is in seconds)                                                                                                           |

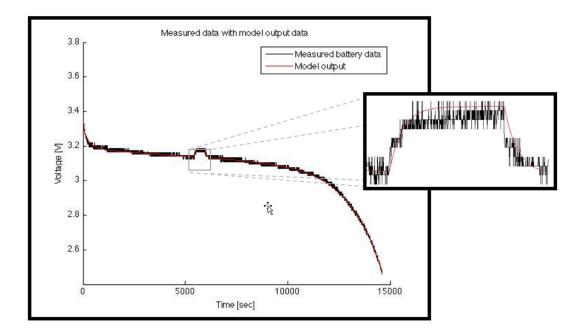

| 3.6  | Measured battery data (black) with cell model output plotted over measured data (Red). To the right of the picture is a zoomed view of the temporary load removal.    |

| 3.7: | Equivalent circuit diagram for cell model with a dependent source used to represent non-linearity characteristics of cell                                             |

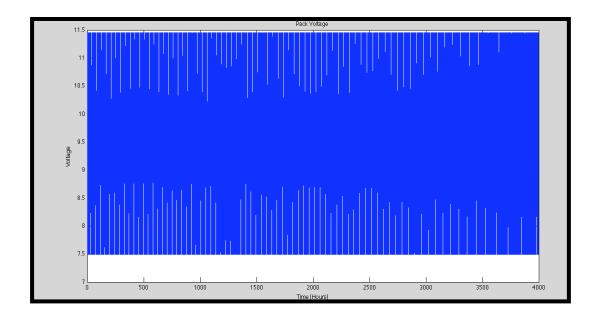

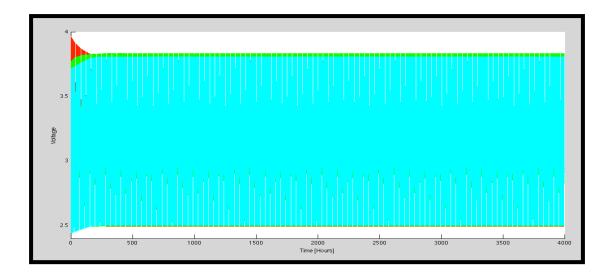

| 4.1  | 3-cell series battery pack voltage over 916 charge/discharge cycles                                                                                                   |

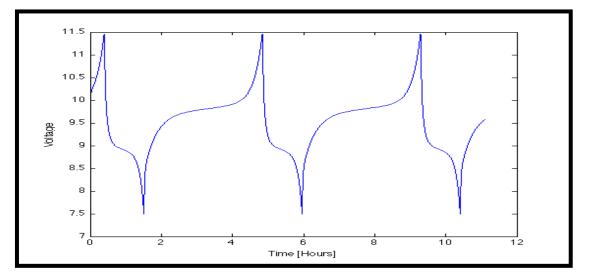

| 4.2  | Zoomed in view of the beginning cycles of the 3-cell series battery pack simulations.<br>The final cycles of the simulation also look similar to these                |

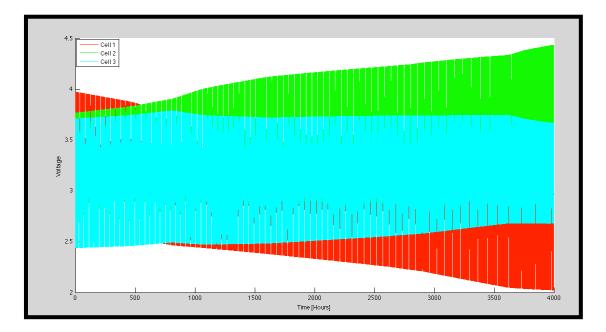

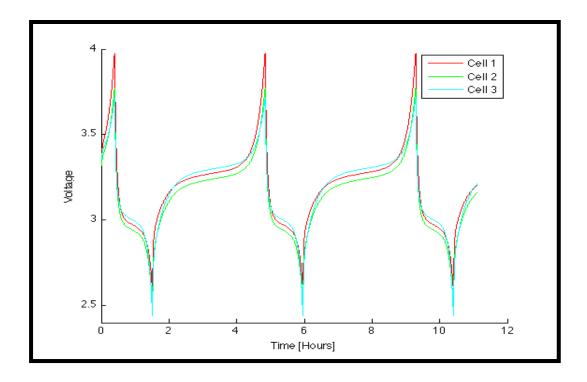

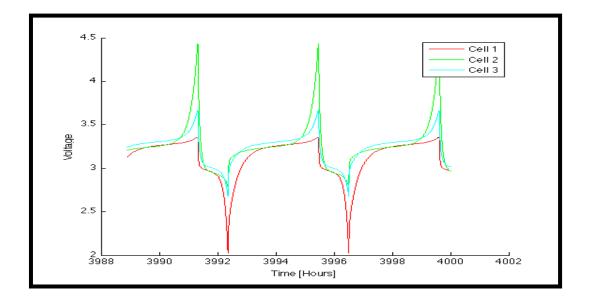

| 4.3  | 3-cell series battery pack initially unbalanced, without balancing circuits after 916 charge/discharge cycles                                                         |

| 4.4  | Zoomed in view of initial cycles of 3-cell simulation without bypasses                                                                                                |

| 4.5  | Zoomed in view of final cycles of 3-cell simulation without bypasses                                                                                                  |

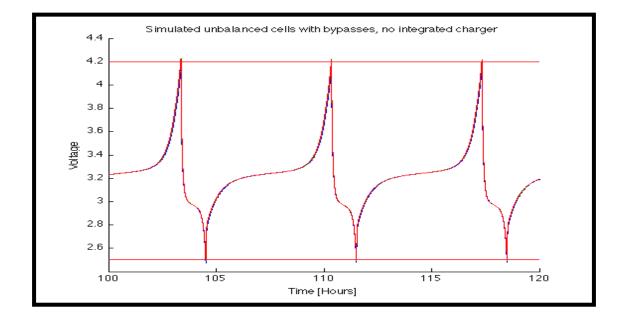

| 4.6  | Simulations performed with the same initial conditions as the previous simulation and cell parameters but with the addition of balancing circuitry being simulated 55 |

| 4.7  | Zoomed in view of the initial cycles of the 3-cell simulation with bypasses 56                                                                                        |

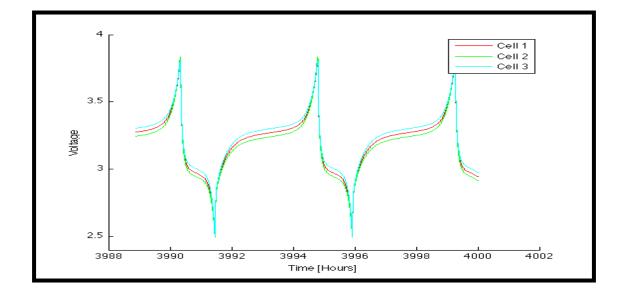

| 4.8  | Zoomed in view of the final cycles of the 3-cell simulation with bypasses                                                                                             |

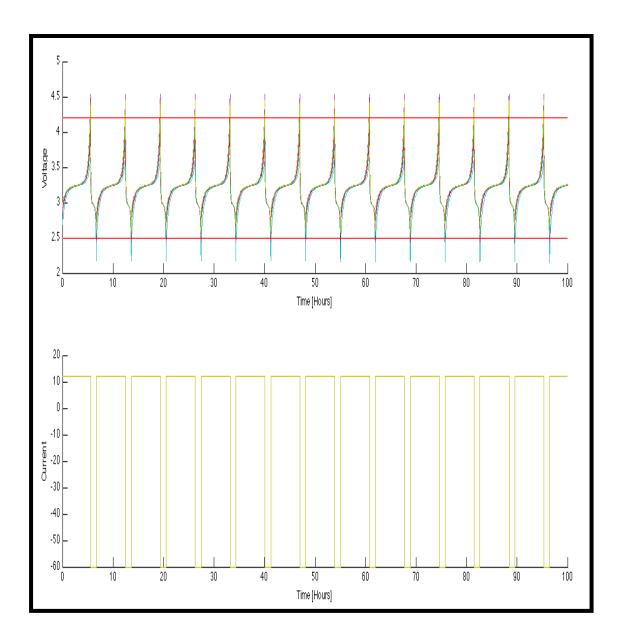

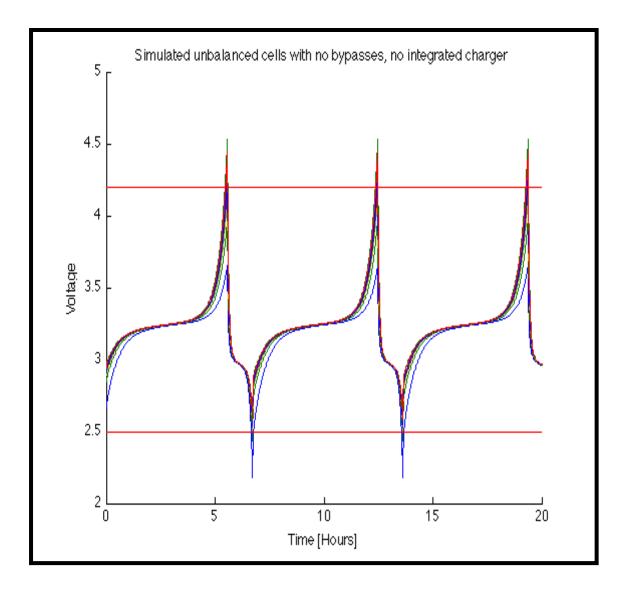

| 4.9  | Simulations performed with the same initial conditions and cell parameters and without an integrated charger or any BMS                                               |

| 4.10 | Zoomed in view of the initial cycles of 10-cell pack without bypasses                                                                                                 |

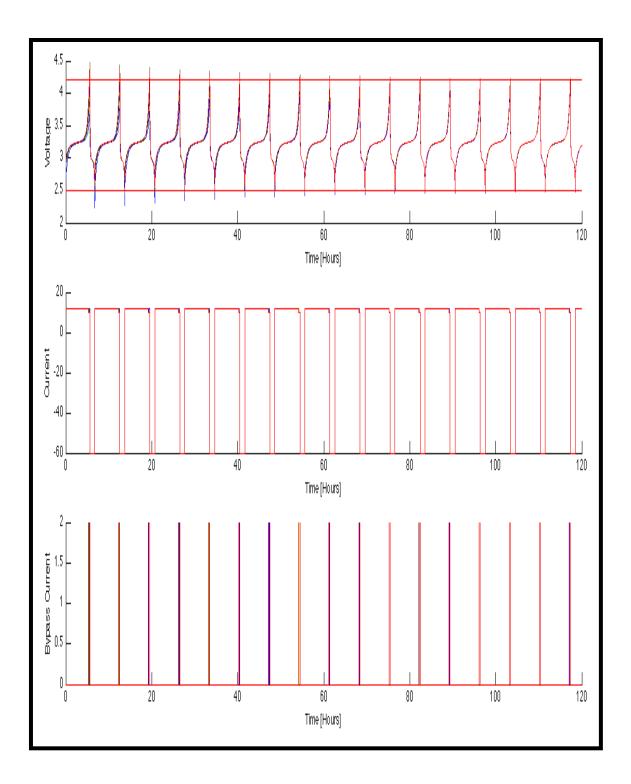

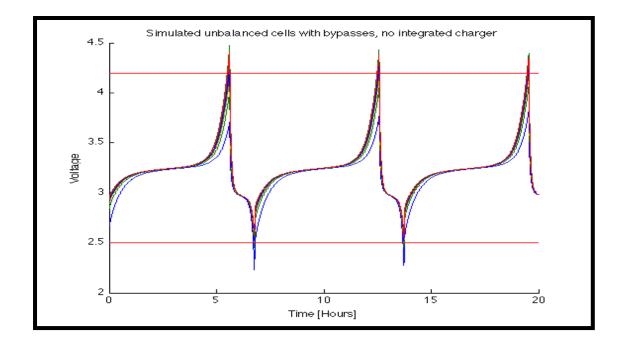

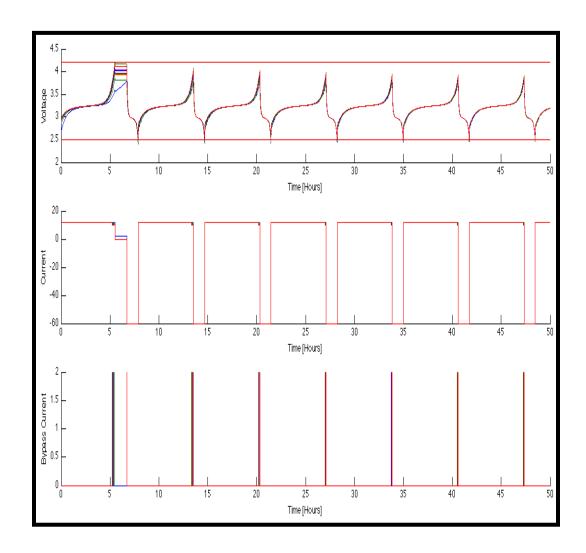

| 4.11 | Simulations performed with the same initial conditions and cell parameters but with the passive bypass and non-integrated charger                                     |

| 4.12 | Zoomed in view of the initial cycles of the passive bypasses-only-simulations63                                                                                       |

|      |                                                                                                                                                                       |

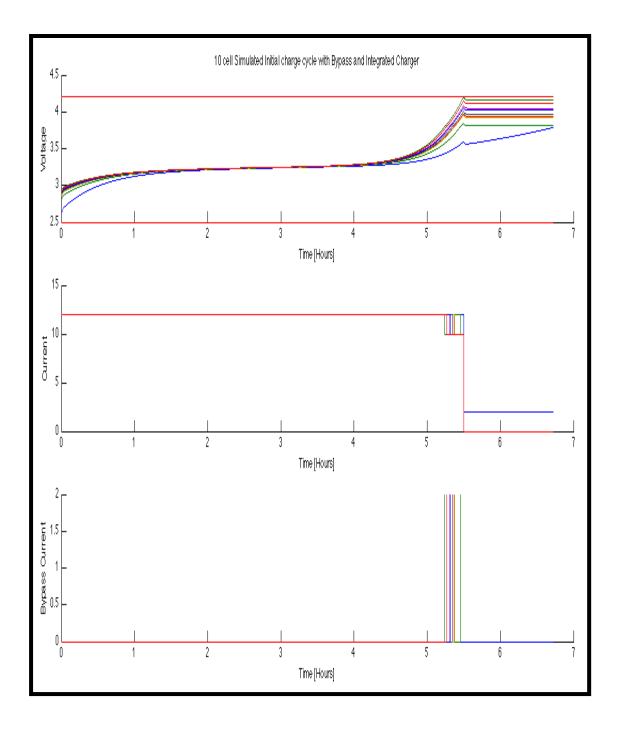

| 4.14 | Simulations performed with the same initial conditions and cell parameters but with the integrated charger and with BMS                             |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.15 | Zoomed in view of the first cycle of integrated charger and BMS simulation 66                                                                       |

| 5.1  | Single 60Ah LiFePO4 Cell                                                                                                                            |

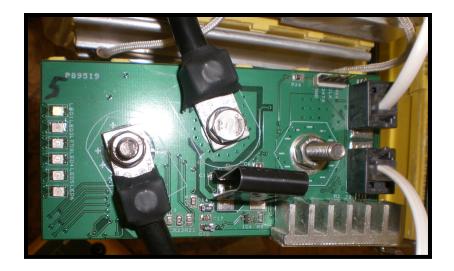

| 5.2  | Individual Cell Management Unit pictured mounted on a single LiFePO4 Cell 70                                                                        |

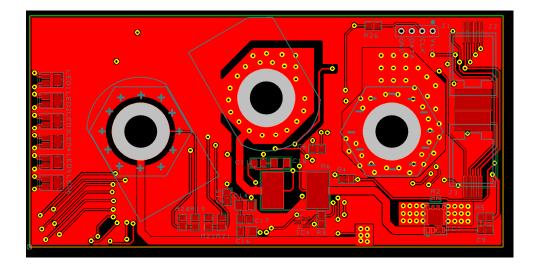

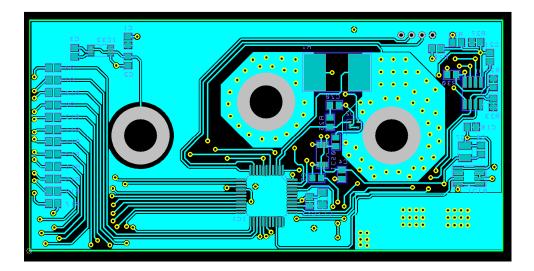

| 5.3  | Top side of ICMU PCB                                                                                                                                |

| 5.4  | Bottom side of ICMU PCB                                                                                                                             |

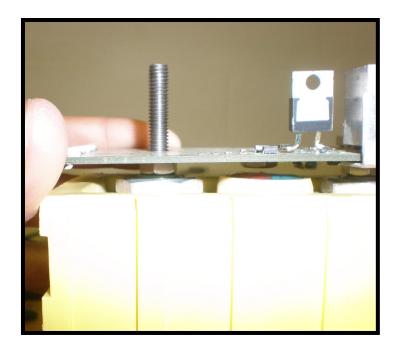

| 5.5  | Cell with M6 threaded bolt inserted with nut                                                                                                        |

| 5.6  | Top View of ICMU board on a single LiFePO4 Cell before being tightened down with nuts on the threaded shafts                                        |

| 5.7  | Circuit board tightened down onto battery terminals and also shown are connections to adjacent cells in the series connected cells                  |

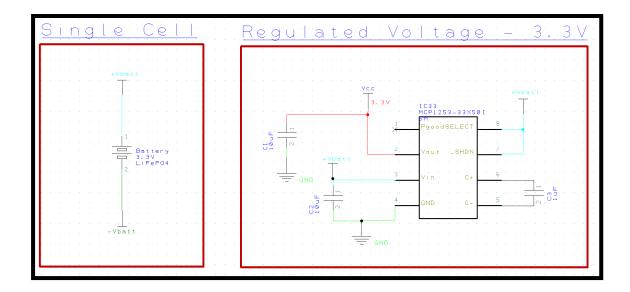

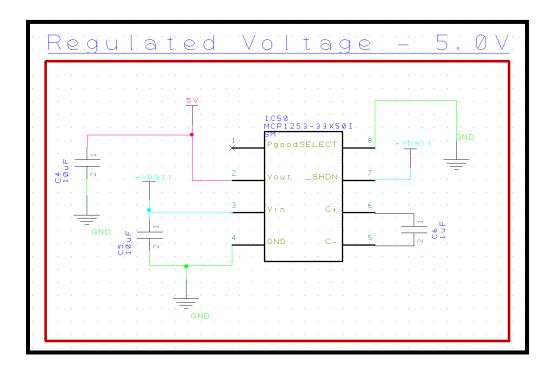

| 5.8  | Schematic: Single LiFePO4 Cell and 3.3 volt bus derived from charge pump 75                                                                         |

| 5.9  | Schematic: 5 volt bus derived from charge pump75                                                                                                    |

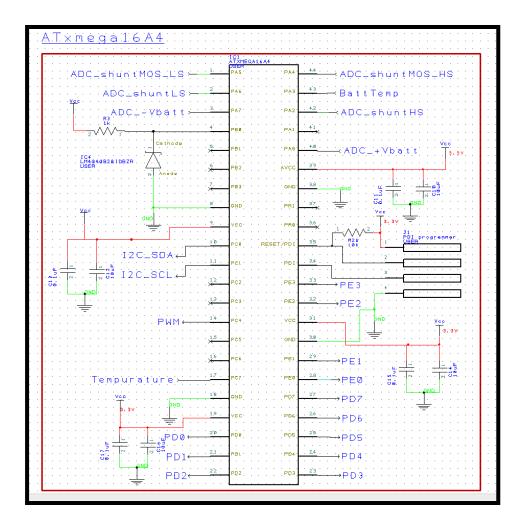

| 5.10 | Schematic: Microcontroller schematic for ICMU PCB                                                                                                   |

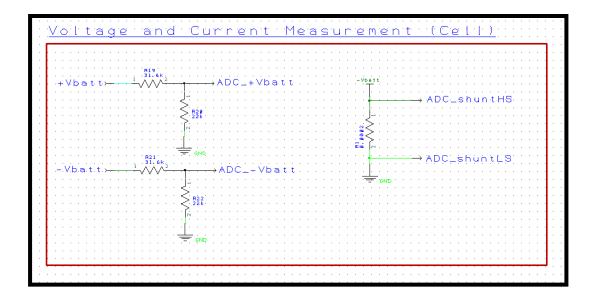

| 5.11 | Schematic: Voltage divider to scale cell voltage for microcontroller's ADC on ICMU PCB and measure the current going in and out of the managed cell |

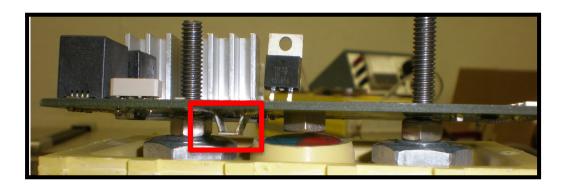

| 5.12 | Current Shunt used to measure system current is pictured in red box                                                                                 |

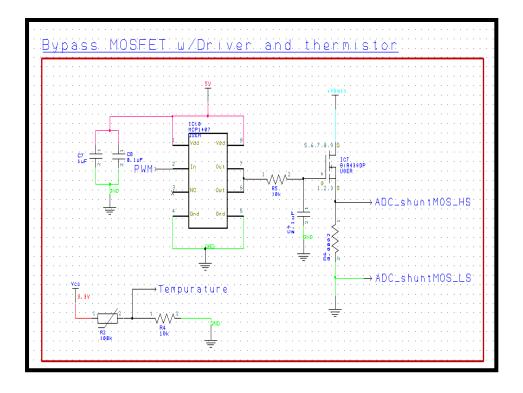

| 5.13 | Schematic: Bypass MOSFET circuit and bypass's overtemperature sensor on ICMU PCB                                                                    |

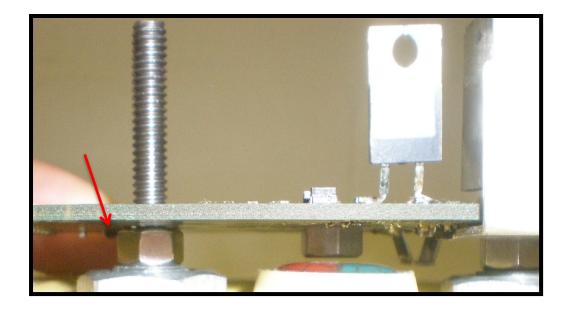

| 5.14 | The red box shows the location of bypass resistor and MOSFET configured to be a voltage-controlled resistor (underneath silver heat-sink)           |

| 5.15 | Location of cell temperature sensor near cell terminal bolt (small black integrated circuit identified by arrow)                                    |

| 5.16 | Schematic: Temperature sensor to measure cell temperature on ICMU PCB 83                                                                            |

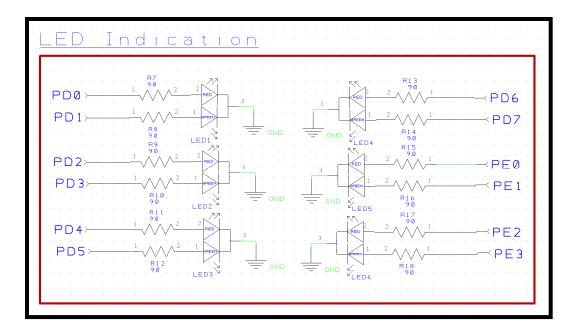

| 5.17 | Schematic: Status LEDs on ICMU PCB                                                                                                                  |

| 5.18 | Actual Implementation of dual color LEDs                                                                                                            |

| 5.19 | Battery Pack with ICMUs displaying various LED colors to demonstrate cell condition                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

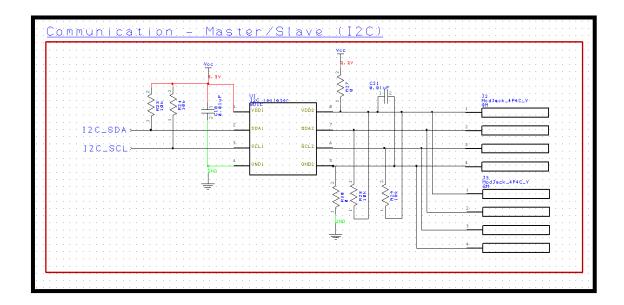

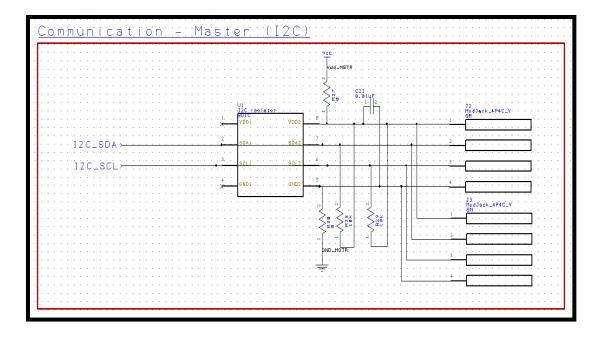

| 5.20 | Schematic: Isolated communication I2C Bus on ICMU PCB                                                                                                                                                                  |

| 5.21 | I2C connections shown from daisy chaining ICMU to ICMU                                                                                                                                                                 |

| 5.22 | I2C connections for BPMU                                                                                                                                                                                               |

| 6.1  | MOSFET operating regions based upon gate voltage, drain current and drain to source voltage                                                                                                                            |

| 6.2: | A high-level schematic of the charging device (Taschner, 2011)                                                                                                                                                         |

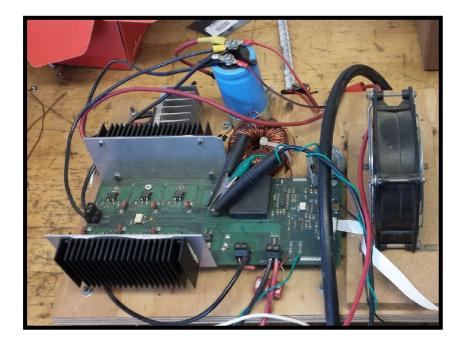

| 6.3: | Photo of charging device (Taschner, 2011) 101                                                                                                                                                                          |

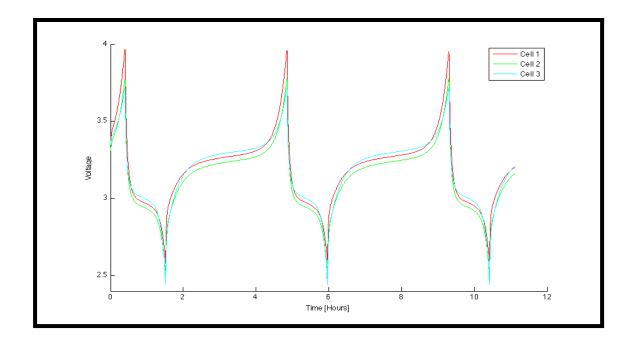

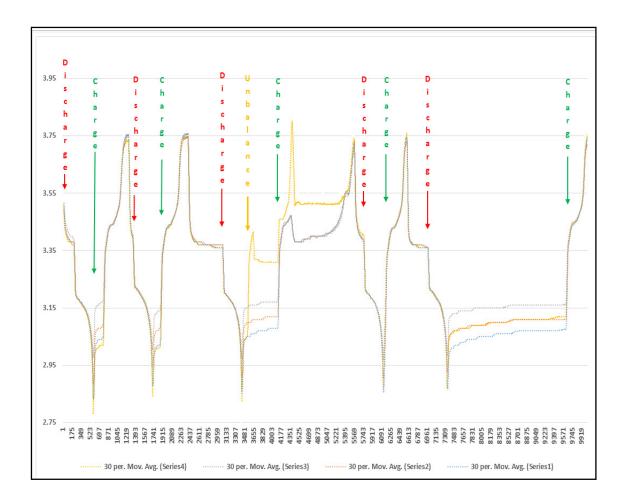

| 7.1  | Data plotted from a 4-Cell series-connected battery pack manually-controlled experiment                                                                                                                                |

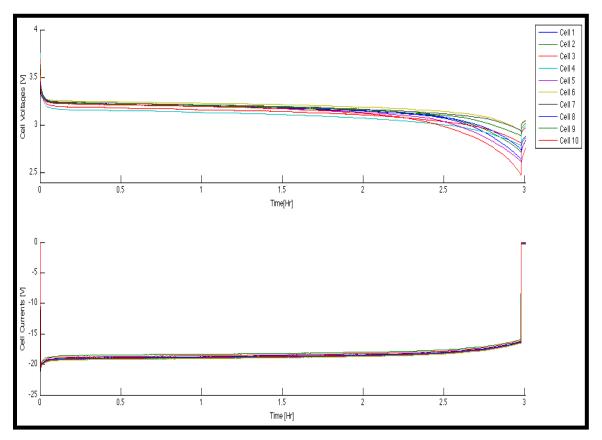

| 7.2  | Discharge cycle of 10 Cell Series Connected LiFePO4 Battery Pack 108                                                                                                                                                   |

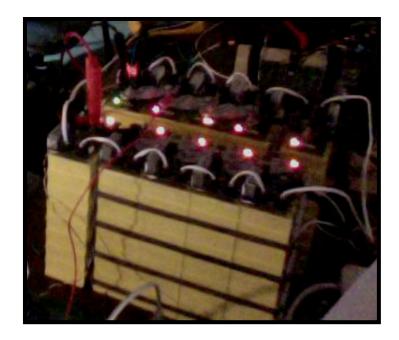

| 7.3  | Battery Pack with ICMU and ICMU/BMPU Hybrid attached to each cell. As pictured here each cell is charging and is not bypassing any current                                                                             |

| 7.4  | Battery Pack with ICMU and ICMU/BPMU Hybrid attached to each cell. As pictured here, 4 cells are bypassing current since they have reached a voltage of at least 3.8V.                                                 |

| 7.5  | Battery Pack with ICMU and ICMU/BPMU Hybrid attached to each cell. As pictured here, all cells are in bypass with the exception of the ICMU/BPMU Hybrid 111                                                            |

| 7.6  | Battery Pack with ICMU and ICMU/BPMU Hybrid attached to each cell. As pictured here, all cells are in bypass. Shortly after this picture was taken, the BPMU commanded the Charger to discontinue the charging process |

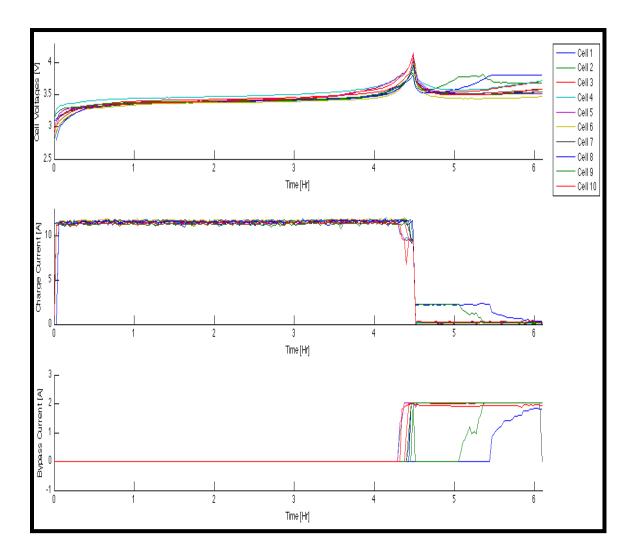

| 7.7  | Charge cycle with integrated charger and BMS for a 10 cell series-connected battery pack                                                                                                                               |

## LIST OF TABLES

| Table |                                                                   | Page |

|-------|-------------------------------------------------------------------|------|

| 3.1   | Values for obtained parameters for LiFePO <sub>4</sub> cell model | 46   |

| 6.1   | Communication packet sent from the BPMU to the charger            | 103  |

## CHAPTER I

#### **INTRODUCTION**

Portable battery applications today can consist of either a single electrochemical cell (which will further be referred to simply as a "cell") or a battery pack that consists of a combination of two or more cells. However, in industry, the term battery is often interchangeably used to describe both an individual cell as well as a battery pack. A cell that is designed such that it only is discharged once, and not recharged, is referred to as a primary cell. A cell that is designed such that it can be discharged and recharged multiple times is known as a secondary cell. It is the secondary cells and their applications that are the focus of this research. When using these secondary cells, special care must be taken to ensure the cells' voltage, temperature, and maximum current remains within the manufacturer's specified operating range. Maintaining this range will help to ensure that the manufacturer's specified cell capacity, the total possible amount of charge before damage occurs, stays consistent with each charge and discharge cycle. This number of charge and discharge cycles is also referred to as the cells' cycle life. Cell manufacturer's specifications often provide a minimum cycle life to which the cell should be capable of maintaining a specified storage capacity. That is, provided there are not manufacturing defects and the cells are properly used and maintained. In general, this minimum cell cycle

life can increase or decrease with more aggressive or lower demanding deviations from the cell manufacturer's recommended voltage operating ranges (Hartmann, 2008).

## 1.1 Types of Cell Combinations (Battery Packs)

In applications where a single cell is utilized, monitoring and maintaining the recommended manufacturer's operating range is straightforward. This is because the charging device and load can be controlled to cater to that individual cell's operation. On the other hand, in applications where there is a battery consisting of multiple cells, ensuring each individual cell stays inside the required voltage range can become more challenging. Battery packs can consist of two cells (i.e. handheld portable consumer products) to several thousand (i.e. electric vehicle applications). Battery packs can be constructed such that they are connected in series, parallel, or a combination of series and parallel. The various combinations of cells and the challenges of monitoring and managing them will be discussed in the following paragraphs.

## 1.1.1 Series-Connected Cells

In applications that demand higher voltages than an individual cell can provide, a number of cells can be connected in series to create a battery pack with the required higher voltage. This type of battery pack configuration is referred to as series-connected or simply as a series string. During operation of this battery configuration type, the current during charging and discharging is the same current through each cell within the string. This is advantageous when measuring current as only a single current measurement is required. However, when it comes to monitoring cell voltages, circuitry is required for each individual cell. In addition, due to the fact that a single current charges and discharges these cells, how well balanced the stored energy in each cell is becomes an issue. Depending on the balance of energy within the pack and individual cell construction variations, cells may finish charging and discharging at different times. Variations between the cells is what causes the individual cell voltages to go outside the manufacturer's specified range, and cause damage to individual cells. As will be discussed later in this document, several methods exist that allow the cells in the string to be balanced.

In general, it is possible for one or more cells to fail in an open-circuit state or in a short-circuit state. If a cell fails in an open-circuit condition, there is no longer a current path. This renders the series-connected battery pack unusable. On the other hand, a short-circuit cell failure condition, while not ideal, will still allow for current to be drawn from the battery pack. The short-circuit condition will reduce the voltage of the overall battery pack by the voltage that was once provided from the short-circuit cell.

## 1.1.2 Parallel-Connected Cells

In applications that demand higher current than an individual cell can provide, multiple cells may be connected in parallel to provide higher current draw. Since the cells are connected in parallel, all of the cells' voltages are equal. If there is voltage difference before the cells are connected in parallel, the higher potential cells will transfer energy to the lower potential cells until the voltages balance (to prevent a large surge of current the cells should be relatively balanced). In terms of monitoring circuitry, paralleling cells is beneficial in that only one circuit is needed to measure the whole parallel group's voltage. However, the exact individual currents provided by each cell are unknown unless the individual cell currents are measured. In terms of cell failures in this configuration, unlike the series configuration, the open-circuit fault condition does not render this pack configuration useless. However, with this type of failure the application will draw higher currents from the remaining cells. If the remaining parallel cells cannot handle the new current demand, they could also be damaged. In the case of the short-circuit fault condition, this will cause all of the other parallel connected cells to discharge through the faulted cell and render the battery pack un-useable.

## 1.1.3 Series and Parallel Connected Cells

In applications that require both higher voltages and higher current, a combination of series-connected and parallel-connected cells is required to form the battery pack. There are two common combinations that exist. The first combination is paralleled-seriesconnected cell strings. This combination consists of several cells connected to form series strings, which in turn are connected in parallel. The second combination is "seriesconnected parallel groupings". This combination consists of several cells connected to form parallel cell groupings. These parallel cell groupings are in turn connected in series. Based upon the previous discussion, the configuration that stands out in terms of reliability is the first combination of paralleled-series-connected cell strings. In this configuration, the fault that rendered the original independent series string unusable, has less of an impact and improves overall reliability (McDowall, 2005). This is because an open-circuit failure results in only one-of-the-many strings to become unusable. The remaining strings can still provide energy to allow the application to continue. In the second configuration, the fault that renders the series-connected-parallel groupings unusable still poses an issue. If a cell fails in a short-circuit condition, it will still drain energy from the remaining cells within that entire grouping.

## 1.2 Goals of Research

The focus of this research is to monitor and protect cells within a battery pack that are connected in a series-connected configuration. To ensure that the cells stay balanced within a series-connected configuration, the use of a cost-effective, lossy, cell bypass is investigated. Although only a single series-string is investigated, the principles of this research can be carried over to paralleled-series-string battery packs. In terms of cell chemistry, lithium-based chemistries are of focus in this research due to their high energy density, lower costs, and the traction it is gaining within the market place (Krieger, 2103) (Vincent, 2000). To perform this research a first-principles cell model is obtained via data collected through a given procedure. This model obtained in turn is then used to simulate the cell balancing circuitry and its effectiveness. In order to further improve the utility of the cost-effective, lossy, cell-bypass, a concept of integrating the cell balancing system and the charging device is proposed and investigated.

## 1.3 Thesis Outline

The research performed is provided over seven chapters. Chapter I is an introduction to cells and batteries. Chapter II provides a history of cells as well as background information on cells, cell balancing methods, and a proposed balancing method and charging system is provided. Chapter III provides details on a procedure that is performed to collect data used to determine a cell model. Chapter IV uses the obtained model to demonstrate the effectiveness of a passive bypass for balancing a series-connected battery pack. Also simulated in Chapter IV is the proposed balancing system. Chapter V and Chapter VI provides a summary of the software and hardware, respectively, used to implement an interactive charger and passive bypass balancing battery management

system. Chapter VII provides results from experiments performed to test the proposed method. Chapter VIII concludes the thesis along with recommendations for future work in this area.

## CHAPTER II

#### BACKGROUND AND RELATED WORK

This chapter discusses the history of electrochemical cells and battery packs. A description of the inner working of electrochemical cells is given along with the various cell chemistries. This section ends with operational considerations when using electrochemical cells, a summary on charging techniques, and a summary on cell-balancing techniques.

## 2.1 The History of Electrochemical Cells

Although the earliest electric cells were in existence over 2,000 years ago, the history of the battery truly begins in the 18th and 19th centuries. People like Alessandro Volta (1745 - 1827) and Luigi Galvani (1737 - 1798) carried out the groundwork that led to an electrochemical energy storage device, and their names live on in terms such as "volts" and the "galvanic cell" (Bergveld, 2001).

Around the 1800s the voltaic column, the world's first working battery was created. This battery consisted of alternate copper and zinc plates, separated by scraps of cloth saturated with acid. Using this first battery, Volta discovered that certain liquids initiated chemical reactions between metals, thereby generating electrical energy (Bergveld, 2001). In the early 19th century, Volta worked in close collaboration with the French National Institute to further develop the battery. The first battery suitable for mass production was developed in 1802 by the chemist Dr. William Cruickshank (Anders, 2003). He stacked alternating layers of copper and zinc sheets of equal dimensions. This stack was then placed in a sealed wooden chest and sealed with cement. This chest in turn was then filled with a saline lye.

In 1859 the French physicist Gaston Planté used conductor plates in dilute sulphuric acid, which led to the first rechargeable battery (Bergveld, 2001). Previous batteries developed up to this point were all primary cells and were not re-charged. Planté's invention led to the first rechargeable secondary battery, which was a lead-acid chemistry that is used to this day.

Over the following decades the lead battery underwent a number of significant further developments. By introducing a variety of alloys, battery performance was greatly improved which then minimized the need for maintenance. Experimentation with lithium batteries began in 1912 under G.N. Lewis, and in the 1970s the first non-rechargeable lithium batteries were sold. A research team managed by Akira Yoshino of Asahi Chemical, Japan built the first lithium ion battery prototype in 1985, a rechargeable and more stable version of the lithium battery; followed by Sony that commercialized the lithium ion battery in 1991 (Vincent, 2000) (The Economist, 2008). The next section will discuss the inner workings of these cells.

## 2.2 Electrochemical cells

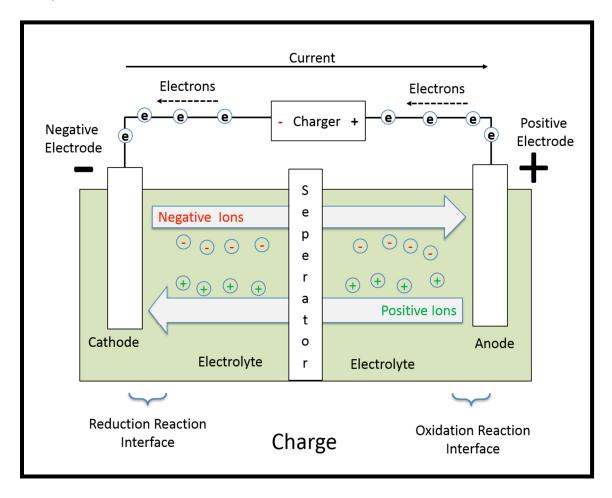

Electrochemical cells are aptly named because they can provide electrical energy stored in the form of chemical energy. This energy can then be utilized at a later time by conversion of the chemical energy back to electrical energy. At a high level, a cell is comprised of two metal electrodes suspended in an electrolyte. At the interfaces between the electrodes and electrolyte are where chemical reactions take place allowing for the conversion to and from electrical energy (depending on whether the cell is being used as a load or if it is being charged, respectively). The two electrodes switch roles as anodes or cathodes, depending on whether they are being charged or discharged. The two electrodes will be designated as PE and NE, for the positive electrode and negative electrode, respectively. In the case of charging, the PE and NE are designated as the anode and cathode, respectively. During charging, at the interface between the electrolyte and the PE, an oxidation reaction occurs. As a result of this, electrons are free to flow out to the external charging circuitry. Simultaneously, at the electrolyte and the NE interface, a chemical reduction process occurs that accepts electrons from the external charge circuitry. Inside the electrolyte, negatively charged ions produced from the reduction reaction occurring at the NE, move towards the PE. Similarly within the electrolyte, positively charged ions produced by the oxidation reaction at the PE move towards the NE. Thus, the flow of current is possible because of the electrons, which travel in and out of the cell, use the electrodes as a medium to travel through. The availability of free electrons in the PE and the "room" to accept electrons in the NE is made possible through the chemical reactions made at the electrolyte and electrode interface. These reactions can continue because the positive and negative ions use the electrolyte as a medium to travel through.

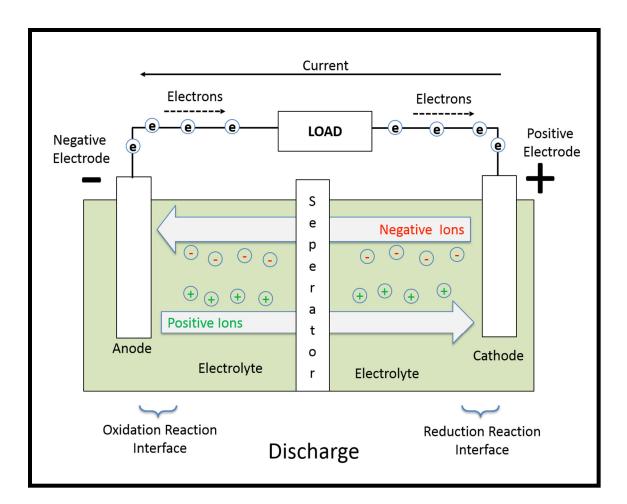

The discharge process through a cell is the reverse of the charging process. By definition, the PE and NE switch roles as the anode and cathode. The location of the reactions and direction of movements for the electrons and ions are also switched. This can be more clearly seen by comparing Figure 2.1 and Figure 2.2. Pictured within in the figure, in between the PE and the NE, is an electrically isolating separator. The separator is typically a porous material that still allows the ions to easily travel through, but not so porous that it does not behave well as an electrical insulator (Kumar et al., 2010) (Bergveld, 2001).

Figure 2.1: Electrochemical Cell pictured during charge process and electrons and ion

travel paths.

Figure 2.2: Electrochemical Cell pictured during discharge process and electrons and ion travel paths.

## 2.3 Cell Chemistries

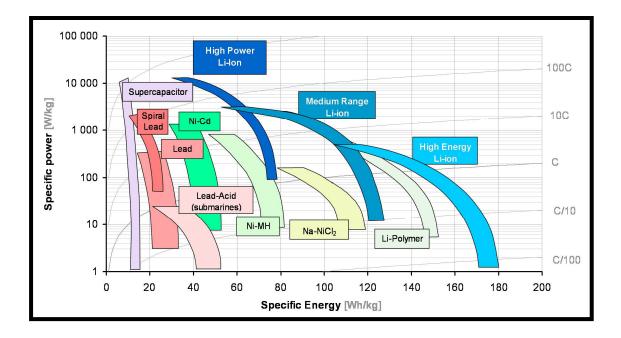

Although the focus of this research is on rechargeable Lithium Ion (Li-Ion) battery cells, a brief overview of other battery chemistries is given in the following sections. For reference, a comparison of multiple cell chemistries and storage technologies are given in the Ragone Plot in Figure 2.3 (Kalhammer, 2007). As can be seen, the various types of lithium-based energy storage devices, outperform the other storage devices in terms of energy storage and instantaneous power per kilogram of material.

Figure 2.3: Ragone plot comparing several types of cell chemistries and other energy storage devices (Kalhammer, 2007).

## 2.3.1 Lead-Acid

The oldest form of rechargeable battery is the lead-acid battery. The lead-acid battery was developed into two main designations. The first being sealed lead-acid (SLA) and the second being large valve regulated lead-acid (VRLA). Both battery types should not be operated at high depths of discharge to preserve cycle life. An advantage of the lead-acid battery is that cells may be balanced by charging the battery pack with a slow, trickle charge for long durations. Typical charge times are 8-16 hours, and typical cycle life is 200-300 cycles. This short cycle life is due to the corrosion that occurs for the positive electrode which causes depletion of the active material and expansion of the plates. The optimum operating temperature for lead-acid is 25 degrees C, and as a general rule, a change of 8 degrees C will cut the cycle life in half. The lead-acid battery has the lowest

energy density of rechargeable cells, making it unsuitable for smaller consumer electronics (Buchmann, 2011).

#### 2.3.2 Nickel-Cadmium

The Nickel-Cadmium (NiCd) battery has advantages in that it is well-suited for fast charging and rigorous discharge conditions. NiCd batteries have a typical cycle life of 1,000 cycles, and offer good performance at low temperatures without significant impact to cycle life. The NiCd has a decent shelf life as compared with other rechargeable cells, and is the lowest-cost battery in terms of cost per cycle. Unfortunately, the NiCd battery suffers from the memory effect, and relatively low energy density. The memory effect occurs when NiCd cells are charged after being only partially discharged several times. This effect causes the cell to lose some of its prior capacity and it "remembers" the new smaller capacity (Buchmann, 2011). To prevent this, the NiCd cell simply has to be discharged to its full rated capacity.

#### 2.3.3 Nickel-Metal Hydride

The Nickel-Metal Hydride (NiMH) battery offers 30-40 percent higher energy density as compared to NiCd, and is less prone to the memory effect. The disadvantages of the NiMH are related to its performance which is depleted if cycled at high discharge rates. Additionally, the NiMH requires a more complex charging algorithm, and more frequent maintenance to prevent crystalline formation. This higher-cost battery has a high self-discharge rate (50% higher than NiCd), and is sensitive to high temperatures.

#### 2.3.4 Lithium Based Chemistries

The Lithium-Ion (Li-Ion) battery is probably the most well-known chemistry on the market today. Original development for this battery began in 1912, but was not commercially available until 1991 due to concerns of safety. The energy density of Li-ion cells are twice that of NiCd, while also offering a low self-discharge rate and low-maintenance with a high cycle life. Because of safety concerns, the Li-ion cells require protective circuits (such as those discussed in this thesis), and are still relatively expensive to manufacture. The cells support higher voltages, and also offer moderate discharge currents. There are several types of lithium-based cell chemistries as will be discussed in the following sections (Buchmann, 2011).

## 2.3.4.1 Lithium Cobalt Oxide (LiCoO<sub>2</sub>)

This chemistry is used in small portable electronics such as cameras, phones, tablets, and some laptops. The positive electrode is derived from cobalt oxide and the negative electrode is graphite carbon. Typical charge and discharge current maximum's are relatively small. Anything higher causes overall cell life to decrease. While the specific energy, the cells' ability to store energy per unit of weight, of this chemistry is high, the specific power is low. The specific power is a measure of how much instantaneous power the cell can provide in a short period of time (Buchmann, 2011).

## 2.3.4.2 Lithium Manganese Oxide (LiMnO<sub>2</sub>)

This chemistry was first introduced in 1996 and had a positive electrode made of lithium manganese oxide. Due to the architecture, a three-dimensional spinel structure, ions can flow more freely, decreasing internal resistance. This allows for high currents which make this chemistry suitable for applications such as power tools, medical equipment, and electric vehicles. Compared to lithium cobalt, lithium manganese has a capacity roughly one-third the size of lithium cobalt's storage capacity (Buchmann, 2011).

## 2.3.4.3 Lithium Iron Phosphate (LiFePO<sub>4</sub>)

In 1996, researchers at the University of Texas implemented phosphate as a positive electrode for a lithium based cell. This material which can be designed with nano-scale phosphate which offers low resistance, high current rating, and long cycle life. Along with the aforementioned benefits and a relatively higher abuse tolerance, this technology finds applications also in power tools, electric vehicles, and back-up power applications. In comparison to the LiMnO<sub>2</sub> chemistry, due to LiFePO<sub>4</sub>'s lower 3.2-3.3V nominal voltage, it has a slightly lower specific energy (Buchmann, 2011) (Padhi et. al, 1996).

### 2.3.4.4 Lithium-Titanate (Li<sub>2</sub>TiO<sub>3</sub>)

This chemistry has been around since the 1980s. In this cell chemistry Lithiumtitanate, as opposed to carbon, is used for the negative electrode. This also forms a spinel structure as with the LiMnO<sub>2</sub> cell chemistry, enabling lower internal resistance. This allows this chemistry to safely charge and discharge quickly at high currents, and has lowtemperature discharge characteristics (down to  $-30^{\circ}$ C). Due to the fact that a single cell provides 2.4V nominally, its specific energy is relatively low (Buchmann, 2011).

## 2.4 Charging

There are several cell charging methods that can be used when it comes to cell charging. A few of these modes are constant-current charging, constant-voltage charging, trickle-charging, float-charging, and pulse-charging. Since the focus of this research is on lithium-based cell technologies, the commonly used constant-current, constant-voltage method will be discussed in greater detail. The other methods will be briefly discussed in the following sections.

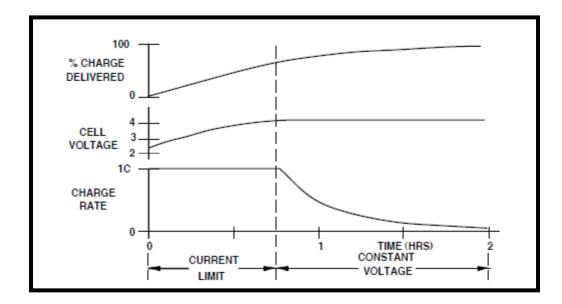

## 2.4.1 Lithium-based Battery Charging

A lithium-based battery charger is typically a fixed voltage source that is current limited. The charger will charge the battery at a constant current (CC) until the battery voltage reaches a pre-set value, the set-point voltage. This charging current is typically limited to a 1C charge rate, however, higher or lower charge rates may be possible depending on the recommendation of the manufacturer. The "C rate" is a relative specification based upon the Ah rating of the cell. This is easily explained in the form of an example. If a cell has a rated capacity of 2Ah, 1C, 2C, and 3C corresponds with charge (or discharge) currents of 2 amps, 4 amps, and 6 amps. About 65% of the total charge is delivered to the battery during the constant current phase of charging.

Once the set-point voltage is reached during the CC phase, the charger will begin to decrease current to maintain the set-point voltage on the battery. This is known as the constant voltage (CV) phase of charging. Most major Li-ion cell manufacturers recommend 4.200V +/- 50 mV as the ideal set point voltage. The constant-voltage cut-off time is typically given by the manufacturer with a desired degree of accuracy to ensure the specified cell cycle-life and capacity can be met. It is important to note that this value is specified for the voltage available at the cell's terminals. When current is actively charged or discharged from the cell, the series resistance in the form of terminal connections and/or wiring provides measurement offsets from the true cell's terminal voltage. A method to overcome this may be accomplished by providing two high impedance measurement wires connected directly to the cell's terminals. Since these two wires are high impedance and are not part of the cell's main current path, the offset voltage measurement issues are overcome (Bergveld, 2001).

Figure 2.4: A CC/CV charger first applies constant current rate until the battery reaches a set-point voltage, charging current is then reduced to maintain the set-point voltage

(Simpson, 2011).

## 2.4.2 Floating/Trickle Charging

When charging battery packs with chemistries of lead-acid, NiCd, or NiMH, float charging and/or trickle charging is performed. This type of charging is utilized after a charge cycle has already completed, and while the battery or cell is unused. The charge current is typically small (less than 0.05 C) and is used to both compensate for the self-discharge of the battery pack as well as balance the pack at the end of charge. This is important in the case of lead-acid especially as sulfation occurs more readily at lower discharge states, leading to poor battery performance.

In terms of lithium based chemistries, holding this chemistry at higher voltages for long durations instead leads to lower cycle life. Some possible causes attributing to the lowering of cycle life are electrolyte decomposition, formation of a passivation layer on the negative electrode, and dendrite formation. Each of these conditions can decrease cycle life as the available active materials required for charging/discharging decreases. In the extreme case, the dendrites can grow so that a short is formed between the positive and negative electrodes (Bergveld, 2001).

## 2.4.3 Lithium Ion Battery Discharging

The end-of-discharge voltage for a Li-ion cell is typically 2.5V on average. At this point, approximately 95% of the energy is depleted, and from there, the cell voltage drops rapidly if discharging were allowed to continue. To protect the cell from overdischarging, most battery management systems will prevent operation beyond this low-voltage cutoff. When a load is removed from a battery after discharge, the voltage will gradually recover by a small amount.

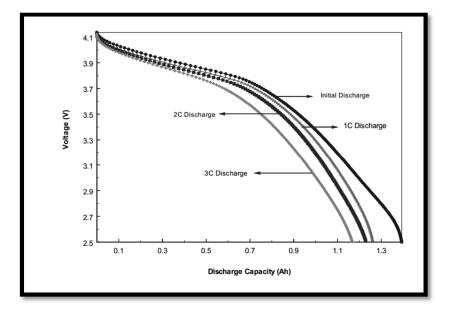

In terms of choice of discharge rates and overall cell cycle life, higher discharge rates lead to faster capacity fade as can be seen in Figure 2.5 (Ning et al, 2003).

Figure 2.5: Initial capacity of  $LiCoO_2$  cells before and after 300 cycles at varying discharge currents. The capacity fade increases with higher c-rates (Ning et al, 2003).

Historically, Li-ion cells had been considered unsuitable for high current loads. In recent years, however, many Li-ion systems permit discharge rates upwards of 50C. This means that a cell rated at 1.5Ah can provide a steady load of 45 amps, and this is being achieved primarily by lowering the internal resistance through optimizing the surface area between the active cell materials (Choi et. al, 2002).

## 2.5 Need for Cell Balancing and Battery Management

Chargers for series-connected packs often look at the battery pack's overall voltage for controlling the charging current. If each cell is identical and evenly charged, it could be assumed that each cell is at the same voltage. However, in practice individual cells' stateof-charge (SoC), or the amount of stored energy within in a cell, is likely to be unequal. During charging, this can cause cells with higher SoC to reach higher than recommended operating voltages. Similarly, during discharge, cells with lower SoC will reach lower than recommended operating voltages.

The choice of what voltage to charge a cell to and what voltage to discharge a cell to ultimately affect the number of charge/discharge cycles that can be achieved with that cell (Hartmann, 2008). In a series-connected battery pack without a method to balance cell SoC, all SoC's are hard to regulate if the individual cell voltages are very different. Again, this is due to the fact that the same current is used to charge each cell. This will cause one or more cells to become fully-charged faster than others. An option at this point is to simply stop charging the series string and leave the remaining cells not fully charged. However, during discharge, the lowest charged cells will discharge the quickest and then energy in the higher charged cells will go unused. This is non-ideal since the full-capacity of the battery pack is not being utilized.

The main causes of cell imbalance are variations in an individual cell's impedance, capacity, and self-discharge rate. These factors will cause divergence in the cells' voltage over time. Since most battery chargers detect full charge by checking whether the voltage of the entire string of cells has reached the voltage-regulation point, individual cell voltages can vary as long as they do not exceed the limits for overvoltage protection. However, both weak cells (i.e., cells with lower capacity or higher internal impedance) and warm cells tend to exhibit higher voltage than the rest of the series cells at full charge termination. These cells are weakened further by continuous overcharge cycles (Andrea, 2010).

## 2.6 Cell Balancing Methods Summary

The impact of cell imbalance on run-time performance and battery life in applications using series-connected cells is certainly undesirable. The fundamental solution of cell balancing equalizes the voltages and SoCs among the cells when they are at full charge. Cell balancing is usually categorized into two types, passive and active. With passive balancing, excess energy is dissipated as heat. Active-balancing, on the other hand, is more energy efficient as it attempts to transfer energy conservatively from cell to cell.

The fact that 100% of the excess energy from a higher-energy cell is dissipated as heat makes the passive method less preferable to use during discharge because of the obvious impact on battery run time. Active cell balancing, which utilizes capacitive or inductive charge shuttling to transfer charge between battery cells, is significantly more efficient because energy is transferred to where it is needed instead of being bled off. Of course, the trade-off for this improved efficiency is the need for additional components and complexity at higher cost.

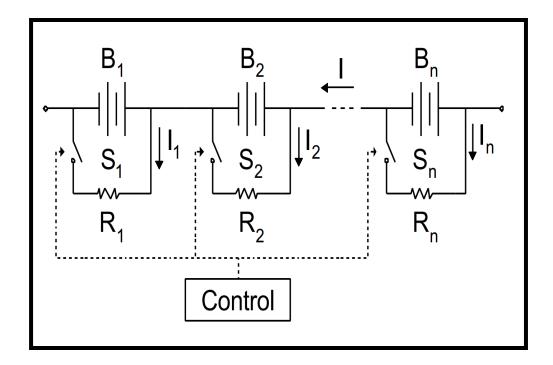

#### 2.6.1 Passive Balancing

The easiest approach to cell balancing is to equalize cell voltages. This can be done by comparing cell voltages with programmable thresholds to determine if cell balancing is needed. If any particular cell hits the threshold, a resistive bypass is enabled. The main disadvantage of this method is the energy lost through the bypassing. This method is known as passive cell balancing (Moore, 2009) (Andrea, 2010). Passive balancing is a costeffective, lossy, option to reduce the disparity between the SoC of each cell. The bypass resistor allows higher charged cells to burn-off excess energy in the form of heat (Figure 2.6). It also creates a path to allow energy to shunt around a cell in a series-connected string. The limitation that comes from utilizing a bypass is the amount of heat that is generated from the bypass device itself. One strategy for utilizing a bypass is to simply turn on the bypass device once the cell hits a specific voltage. This allows the rate-ofcharge to the highest charged cells to be reduced and allows current to be shunted around that particular cell.

Based upon the charging current and bypass resistance, there are three conditions that can exist when a bypass is implemented. One condition is if the bypass resistor is designed such that it bypasses less than the charging current. This implies that the remaining charging current that is not bypassed continues to charge the cell. The second condition is if the bypass resistor is selected such that it bypasses approximately the same value of the charging current. In this condition, the cell stops charging and the cell's voltage will stay constant. This is because if the cell's voltage goes up, the fixed-resistance bypass will bypass a little more current as well. If the cell's voltage goes down, the fixed-resistance bypass also bypasses less current. The third condition is if the bypass resistor is selected such that it bypasses all of the charging current and also draws additional current from the cell. This allows higher charged cells to decrease their SoC while allowing other cells to increase their SoC.

Figure 2.6: Passive Resistive Bypass (Moore, 2009).

# 2.6.2 Active Balancing

Another approach is active cell balancing. This method overcomes the energy loss of the passive method by using capacitive or inductive charge storage and shuttling to deliver energy to where it is needed most, and with little loss. The disadvantage to this method is in component count, cost, and complexity. Active balancing techniques fall into four main groups (Yevgen, 2009) (Moore, 2001):

1. Cell to cell: energy is transferred between neighboring cells.

2. Cell to battery: energy is removed from cells with highest SoC and dumped to the whole battery.

3. Battery to cell: Energy is removed from the battery pack and transferred to the cells with least SoC.

4. Bidirectional: Based on needs, energy is transferred from cell to battery or vice versa.

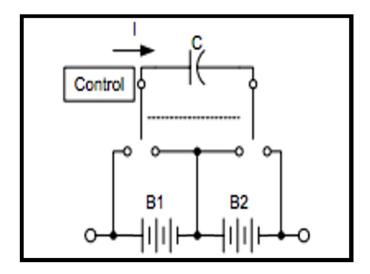

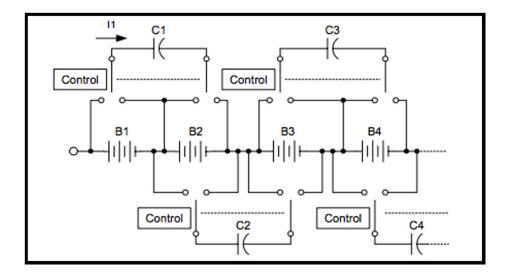

These methods may be implemented in a variety of ways. A simple approach to redistribute the energy between the cells is to connect a capacitor first to higher voltage cell, than to lower voltage cell, as shown Figure 2.7.

Figure 2.7: Capacitor-Based Shuttle (Yevgen, 2009).

More complicated implementations allow the connection of not only two nearby cells, but also cells for far away in the stack for faster equilibration Figure 2.8.

Figure 2.8: Shuttle circuit with remote cells connection capability (Yevgen, 2009).

The main problem with this method is that significant energy losses occur during capacitor charging, due to high currents because of high voltage mismatch. Another problem is that high voltage differences between the unbalanced cells exist only in highly discharged states. Because this method's transfer rate is proportional to cell voltage differences, it only becomes efficient near the end of discharge so that the total amount of unbalance that can be removed during one cycle is low.

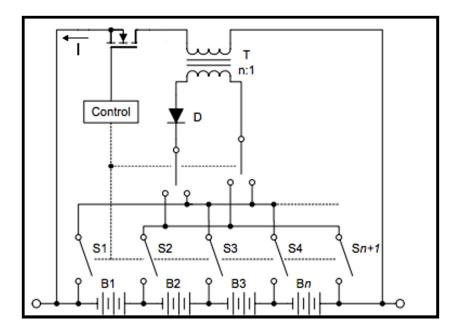

Another active balancing method, depicted in Figure 2.9, is implemented by taking energy from the battery pack as a whole and redistributing it to a single cell. This is done by directing the battery pack current through a transformer which is then switched to one of the cells that needs additional charge. However, the efficiency of such a converter is limited, and the need to use a transformer results in increased price and size of the overall solution (Moore, 2001).

Figure 2.9: Inductive converter cell balancing circuit (Moore, 2001).

## 2.7 A Proposed Integrated Charger and Battery Management System

A study performed in 2011 compared several balancing methods consisting of both passive and active circuitry (Daowd et al, 2011). In the investigation, each method was evaluated and simulated within MATLAB/Simulink. Each method was graded upon its equalization speed, complexity, size, cost, and efficiency. The method that outperformed others in terms of simplicity, and cost-effectiveness, was the passive resistive shunt bypass. In terms of speed and efficiency, the resistive shunt bypass received average to less-than-average ratings. In the case of many high volume commercial applications, cost and development time is often of great concern. In fact, many available battery management integrated circuit manufacturers, such as Texas Instruments, utilize passive resistive shunts for balancing (Texas Instruments, 2012). In this research, the resistive shunt bypass is used due its popularity, cost-effectiveness, and minimal amount of components. A proposed

method to further improve the speed of balancing with passive resistive shunts and reduce the number of cycles a battery pack stays unbalanced is discussed next.

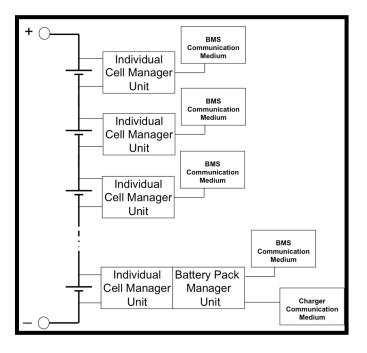

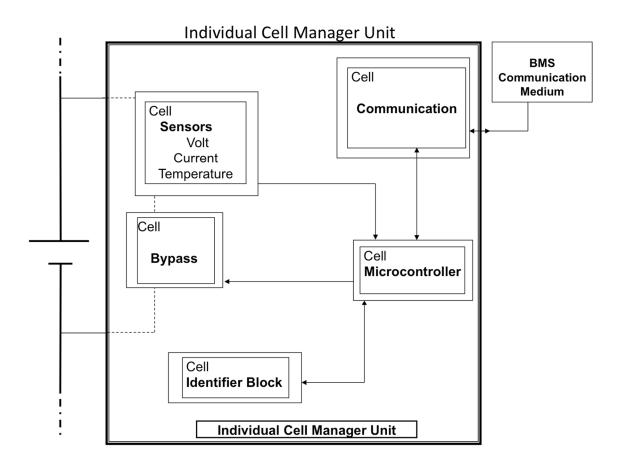

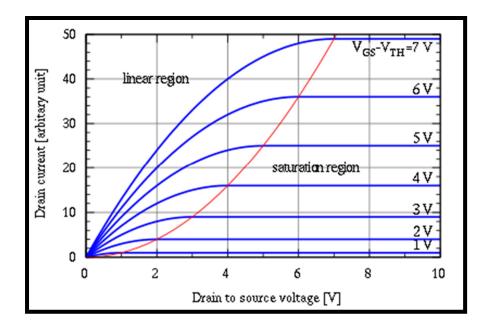

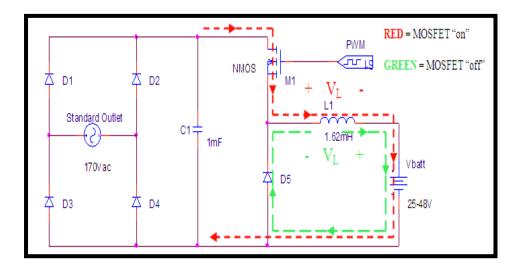

The proposed battery system will use a BMS that interfaces directly with the charging system as shown in Figure 2.10. The BMS consists of one Individual Cell Management Unit (ICMU) per a cell and a single Battery Pack Master Unit (BPMU) for the entire battery pack. The block diagram of Figure 2.11 depicts an ICMU which consists of circuitry that at a high level, includes a voltage, current and temperature monitor, and an adjustable bypass current device. In terms of the adjustable passive bypass device, this will be achieved by a MOSFET driven in its linear region. In doing so this causes the MOSFET to behave as a voltage-controlled resistor. The adjustability of the bypass current as well as the adjustability of the charging current allows the system to have more flexibility when it comes to equalizing the energy within battery pack's cells.

Figure 2.10: High Level Block Diagram for Integrated BMS and Charger System.

Figure 2.11: Detailed block diagram for Individual Cell Manager Unit within BMS.

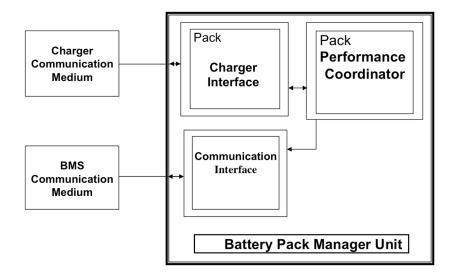

The BPMU, shown in Figure 2.12, processes data from each ICMU for monitoring of the battery pack as a whole. The BPMU will communicate battery pack issues during charge and discharge. In addition, the BPMU will also have a communication interface to the charging system. This interface will allow the BPMU to directly control the charging current profile as it demands from the charger. A block diagram of the integrated charger is shown in Figure 2.13.

Figure 2.12: Detailed block diagram for Battery Pack Manager Unit within BMS.

Figure 2.13: Detailed block diagram for Charger for integrated BMS concept.

The sequence of steps for the proposed method of charging and balancing will be discussed next. First, the charging device will initially charge the battery pack at the maximum constant current rate that the battery pack application can accept. When the highest charged cell is nearing its full charge voltage, the BMS can request the charger to decrease its current as desired. Simultaneously, the BMS can activate bypass current devices on each cell as necessary, shunting as much current as possible around the highest charged cells. In doing so, this allows the remaining lower charged cells to continue charging at a higher rate. If the highest charged cells continue to charge too quickly (even with the bypasses on), the BMS can then request the charging device to lower its charging current as necessary. This continues until the bypass devices can shunt all of the charging current around a given cell and discontinue the charging to any individual cell.

## 2.8 Summary

This chapter provided a brief history on the discovery and the development of cells. Also provided was background information on cells and how they function electrically and chemically during the charge and discharge processes. Next, an overview of cell chemistries used most in industry was provided. This led to a discussion of methods that can be used to perform cell balancing within a battery pack. Lastly, the chapter concluded with a proposed method for balancing using an integrated charger with a resistive-bypass based battery management system.

### CHAPTER III

### BATTERY CELL MODELING

This chapter will discuss a procedure that can be used to obtain a mathematical cell model. The benefits of using a cell model and how a cell model may be used for various applications are also discussed.

## 3.1 Introduction

To be able to simulate the voltage behavior of a cell during usage, either on its own or within a battery pack, an accurate cell model may be used. Using a cell model allows simulations and investigations to be performed of how individual cells behave or multiple cells behave within a battery pack. This allows theories and concepts to be tested without actually spending time on a physical test set-up. This chapter will discuss a cell model and how the parameters for this model are obtained. In order to obtain parameters for the cell model, data must be collected from the cell of interest. The data collected must be obtained following a procedure that allows the cell's dynamics of interest to be observed, as well as either a full charge cycle or a full discharge cycle. After collecting the data, the data is graphed and analyzed to obtain some of the model's parameters. These parameters can vary from cell size, cell chemistry, and even from cell to cell within a manufacturing batch. With regard to the variability within a manufacturing batch, battery packs designed for space applications go through categorizing newly manufactured cells in order to pick cells with well-matched characteristics. The goal and assumption is that these cells start out with the same SoC and have very similar charge/discharge characteristics as they are used throughout their lifetime. If this is indeed the case, the assumption is that such a battery pack no longer requires a battery management system (Pearson, 2004).

Also, cell modeling improves accuracy estimates for a cell's SoC. This is especially the case in applications where the power profile varies such that the electrochemistry dynamics are not able to reach a state of equilibrium. The cell voltage is dependent on multiple factors such as the charge/discharge current, temperature, and the cell's age. This being the case, it can be difficult to provide an accurate estimate of a cell's SoC solely upon its voltage. Also, a sensor cannot directly be employed to read the cell's SoC directly, however with the use of a mathematic cell model/algorithm, this is possible. An exception for using a cell's voltage as an estimate for its current SoC is when the current (and power) is relatively low such that the open-circuit voltage is close to the running voltage. In cases such as these, it is possible to utilize a table that correlates the SoC with open-circuit voltage (Plett, 2004).

Accuracy of the SoC is important in applications where aggressive power profiles demanded from the battery pack are required. The accuracy also allows more aggressive use of energy available within the battery, as the true SoC of each cell is known. To make this concept clearer, take the following example. In a hypothetical application where the cell's voltage is close to the manufacturer's recommended cut-off voltage, the cell's voltage may not be accurately reflected when a large current is drawn from the cell. Due to the cell's internal impedance, an internal voltage drop may occur that is correlated with the current draw from the cell. This is an offset from the true cell voltage, and causes an external voltage measurement to appear as if it were below the cut-off voltage. This issue may be alleviated from more accurate SoC estimates via real-time cell models.

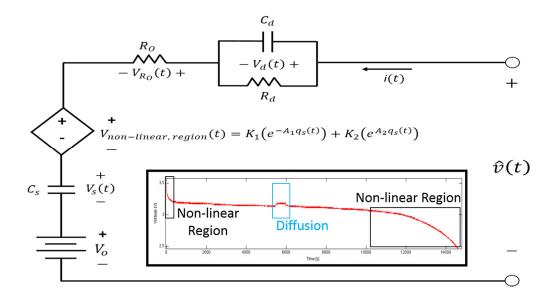

## 3.2 Battery Modeling

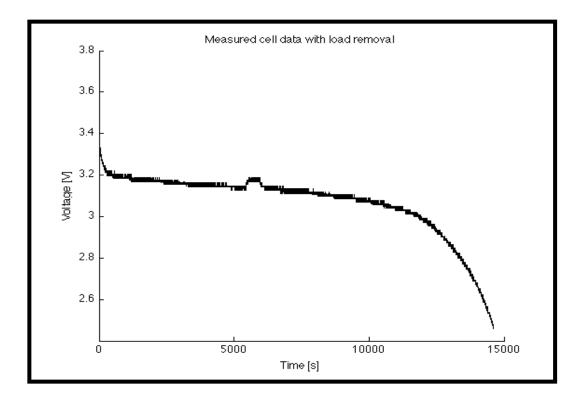

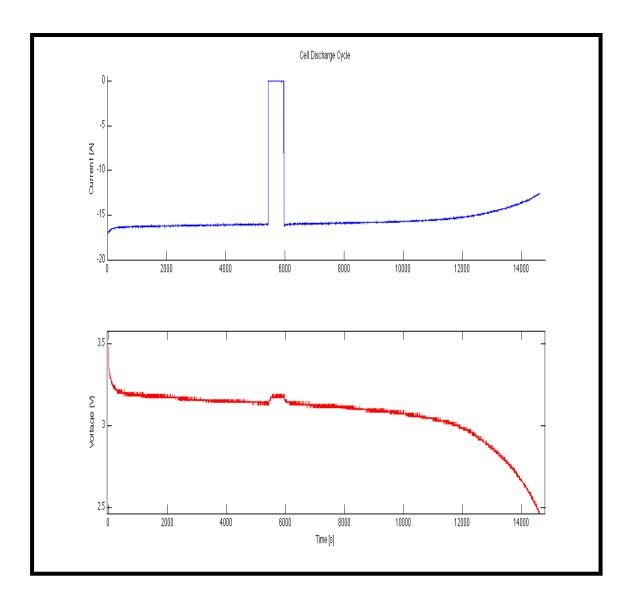

The cell model used in this research is derived from a first-principles based structure (Hartley & Jannette, 2005). In other words, the model is based upon established laws of physics. This model is a generalized structure with parameters that are acquired through data collection consisting of voltage, current, and temperature measurements from a cell as it is discharged through a low-resistive load. To model the charge diffusion characteristics of the cell, during the discharge cycle, the load is temporarily removed from the cell in order to observe the resulting transient response. An example of a complete discharge cycle with charge diffusion transient (small transient towards middle of plot) can be observed in Figure 3.1.

Figure 3.1: Measured Battery Voltage for full cell discharge cycle.

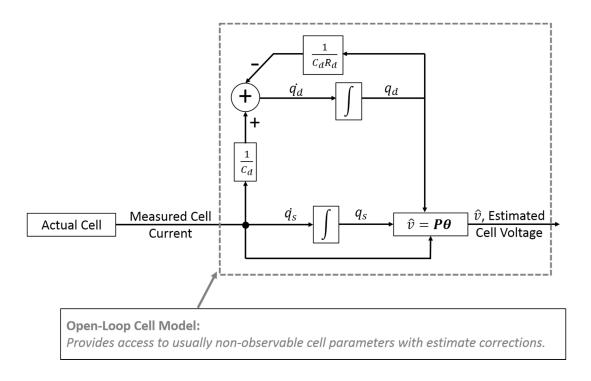

The model obtained will generate a voltage as a function of the stored charge, diffusing charge, and the amount of current flowing in or out of a given cell at any given time, which are denoted by  $q_s(t)$ ,  $q_d(t)$ , and i(t), respectively.

The state equations of the cell model are the stored-charge rate given by

$$\dot{q}_s(t) = i(t) \tag{1}$$

and the diffusing-charge rate given by

$$\dot{q}_{d}(t) = \frac{1}{c_{d}}i(t) - \frac{1}{c_{d}R_{d}}q_{d}(t)$$

(2)

where  $C_d$  is the diffusion capacitance and  $R_d$  is the diffusion resistance (Hartley & Jannette, 2005). The values for the diffusion parameters are obtained by analyzing the diffusion transient response. In order to obtain the stored charge and the diffusing-charge states, equations (1) and (2) are integrated with the measured current during the discharge cycle.

Using only a linear combination of the integrated states  $q_s(t)$ ,  $q_d(t)$ , and the current, i(t), the linear portion of the voltage curve of Figure 3.1 can be accurately modeled. In order to represent the non-linear portions of the voltage curve in the beginning and end of the discharge cycle, two additional exponential terms dependent on  $q_s(t)$  are incorporated. System identification is performed on the data collected using batch least squares to acquire the following parameters

$$\theta = \begin{bmatrix} V_o & R_o & \frac{1}{C_s} & K_d & K_1 & K_2 \end{bmatrix}^T$$

(3)

each of which corresponds to an element of

$$P(t) = \begin{bmatrix} 1 \ i(t) \ q_s(t) \ q_d(t) \ e^{-A_1 q_s(t)} \ e^{A_2 q_s(t)} \end{bmatrix}$$

(4)

such that the battery voltage is given by

$$\hat{v}(t) = P(t)\theta$$

$$= (1)(V_o) + (i(t))(R_o) + (q_s(t))(\frac{1}{c_s})$$

$$+ (q_d(t))(K_d) + (e^{-A_1q_s(t)})(K_1) + (e^{A_2q_s(t)})(K_2).$$

(5)

Based upon the state  $q_s(t)$ , the SoC is calculated as follows

$$Q_{SoC}(t) = \frac{q_s(t)}{q_{s,max}} 100\%$$

(6)

where  $q_{s,max}$  is the rated full capacity of a given cell.

The scope of the research did not implement this model in real-time, however, a brief discussion of such an implementation follows. A real-time implementation allows an application to track cell parameters, usually not directly measureable, that provide more information about a cell's condition. For example, the (SoC) can be extracted from the data with higher accuracy than directly measuring the cell's voltage alone (Hartmann, 2008) (Bergveld, 2001). This is especially useful in cases where the cell's current consumption is dynamically changing, which causes voltage measurements alone to be misleading when it is used for SoC estimation. By implementing a cell model on a computing device (e.g. microcontroller, computer, etc...) in real-time, this allows real-time access to information about the aforementioned non-direct measurements.

There are several additional benefits to be gained from a real-time model. Selfdischarge can be modeled by measuring a cell's remaining capacity after being stored for a long period of time. With an accurate self-discharge model, it can be determined that a cell is failing by detecting a fast self-discharge rate.

In terms of accuracy of a real-time cell model, it is vital in the case of aggressive designs and high-power usage of battery packs. The ability to accurately predict remaining SoC in a battery pack allows for maximum power draw, and may be estimated without overdischarging a cell or causing it damage. This could also allow a smaller battery pack

be utilized for a given application. This is as opposed to sizing the battery pack with a large design margin and higher cost (Plett, 2004).

Figure 3.2: Control block diagram of open-loop cell model.

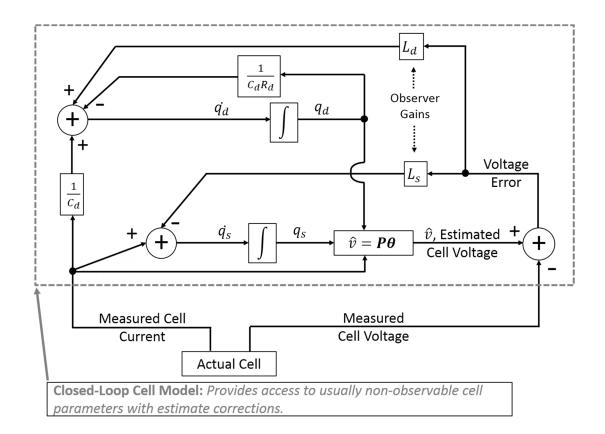

In order to improve accuracy of the model's states, a real-time observer can be implemented to supplement the model running on the computing device. The real-time observer will compare the model's output voltage with an actual measured voltage of the cell of interest by calculating the error,

$$e(t) = v(t) - \hat{v}(t), \tag{7}$$

where v(t) is the cell's measured voltage and  $\hat{v}(t)$  is the model's estimated voltage given.

Equations (1) and (2) become

$$\dot{q}_s(t) = i(t) + L_s e(t), \tag{8}$$

$$\dot{q}_d(t) = \frac{1}{c_d} i(t) - \frac{1}{c_d R_d} q_d(t) + L_d e(t), \tag{9}$$

where  $L_s$  and  $L_d$  are observer gains that are multiplied by the error, e(t), to correct the state estimates, for  $q_s(t)$  and  $q_d(t)$ , respectively, (Plett, 2004) (Vamsi et. al, 2007) (Bergveld, 2001).

Figure 3.3: Control block diagram of closed-loop cell model with observer.

To further improve estimates, there are additional methods that can be implemented. This includes providing the ability for the cell model's internal parameters to adapt such that it tracks the aging effects of the cell. This is opposed to determining the cell's parameters from a single set of data and keeping the internal model parameters at fixed values indefinitely. Also, taking operating cell temperatures into the real-time model allows for more accurate cell-model estimates. A possible approach for adapting cell parameters with temperatures is to gather cell operation data at specific temperatures of interest. A polynomial fit may then be used to match temperatures to correlating coefficients (Plett, 2004) (Hartmann, 2008).

## 3.3 Procedure for Data Collection

In order to get a cell model, data must be collected from the cell during its operation. In this research a fully charged LiFePO<sub>4</sub>, 3.3V nominal, 60Ah cell was used. The cell was charged per the cell manufacturer's recommendations using a power supply with settings for constant current and constant voltage. The cell was first charged in constant current mode at 20A per the manufacturer's recommended charging current of C/3. The power supply was set for a constant voltage of 4.2V, at which point the charger automatically tapered the charging current to maintain the desired 4.2V. The charge process was stopped when the charging current fell below C/6. The cell was then left to rest several hours to allow the cell's voltage to settle after the charging process.

Next, the cell was discharged via a fixed load resistor bank. The equivalent resistance used during the discharge was ~0.21 ohms which provided a nominal discharge current of ~16A. Both the cell's discharging current and the cell's voltage was logged using a microprocessor development board. These measurements were done via a resistive shunt and voltage divider, respectively. The discharging procedure consisted of connecting the load to the cell, removing the load, re-applying the load, and stopping the discharge process. The step of removing the load was performed in order to capture the dynamics

associated with the cell's charge diffusion. The load was removed long enough until the cell's voltage increased and reached a steady-state. At that point, the load was re-applied until the cell's voltage hit the manufacturer's stated cell cut-off voltage. The data collected in this process is graphed in Figure 3.5.

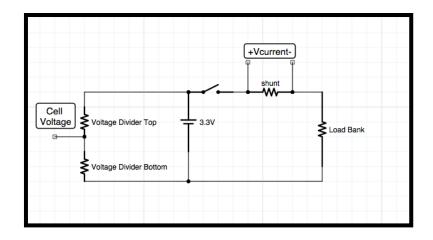

Figure 3.4: Diagram of circuit used to collect cell discharge data.

Figure 3.5: Graph of collected discharge data (time axis is in seconds)

# 3.4 Processing Collected Data

Using the graphed data in Figure 3.5, measurements are made from specific features from the plot. These measurements are then used to calculate and obtain values for the cell model's parameters. The following are the parameters and how they are extracted from the graph.

- 1.  $R_o$ : To determine this value, two other values must be obtained beforehand.

- The current before load removal (BLR),  $I_{BLR}$ , which can visually be determined from the plot.

- The "instantaneous" change in voltage observed directly after removal of the load. This is designated as the voltage after load removal,  $V_{ALR,\Delta}$ . In terms of the "instantaneous" change in voltage, what should be observed upon load removal is a sudden jump in voltage due to the lack of a voltage drop across the cell's internal impedance (because of the sudden stop in load current). It is noteworthy to distinguish between the "instantaneous" voltage change and the exponential voltage change due to the cell's diffusion properties (of which the parameters are obtained in the next section), because they occur very closely one after the other in the graph.

• To calculate

$$R_o$$

the following equation is used:  $R_o = \frac{V_{ALR,\Delta}}{I_{BLR}}$

- 2. Diffusion Time Constant: To determine the Diffusion Time Constant,  $\tau_d$ , the cell dynamics associated with load removal are analyzed. The following steps are used to determine the time constant:

- Determine the initial voltage,  $V_{Diff,initial}$ , immediately after the removal of the load.

- Next, determine the time,  $T_{Diff,initial}$ , at which the load was removed.

- Determine steady-state voltage,  $V_{Diff,SS}$ , after load removal (this requires that during data collection the cell voltage was allowed to reach a steady-state after the load was removed).

• Calculate the voltage that corresponds with 63% of the voltage difference between the initial voltage and steady-state voltage. This value is the diffusion voltage after one time constant which will be designated as  $V_{Diff,T_1}$ , This step is summarized by the following:

$$V_{Diff,T_1} = (V_{Diff,SS} - V_{Diff,initial}) \times 0.63.$$

- Visually determine the time,  $T_{Diff,T_1}$ , at which the time at which  $V_{Diff,T_1}$  occurs.

- Finally,  $\tau_d$  can be calculated with:

$$\tau_d = T_{Diff,T_1} - T_{Diff,Initial}$$

- 3.  $R_d$ : To determine  $R_d$  the following steps can be followed:

- Visually determine the current,  $I_{Diff,initial}$ , right before the load is removed.

- Use  $V_{Diff,\tau}$  to determine the current right before the load is removed.

- $R_D$  may be calculated with:

$$R_{d = \frac{V_{Diff,\tau}}{I_{Diff,initial}}}$$

4.  $C_d$ : may simply be calculated with the obtained values of  $R_d$  and  $\tau_d$  using the following:

$$C_d = \frac{R_d}{\tau_d}$$

- 5. To determine  $V_o$ , two parameters are required, the change in voltage after the load removal and the voltage at the end of the end of the linear region of cell.  $V_o = V_{ALR,\Delta}$ + end of linear region voltage.